Werbung

In einer Fragerunde mit Intel-CEO Pat Gelsinger wurde dieser gefragt, ob Intel an einer Technik wie AMDs 3D V-Cache arbeitet. Diese Frage beantwortete Intel grundsätzlich mit einem "Ja", aber in den vergangenen Stunden wurden zahlreiche Meldungen veröffentlicht, die wir etwas einordnen wollen.

Die Antwort von Pat Gelsinger lautete wie folgt:

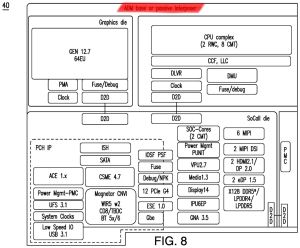

Das Gerücht zu einem erweiterten Cache im Base-Tile von Meteor Lake ist nicht neu. Für die kommenden Generation hat sich Intel aber offensichtlich gegen diesen zusätzlichen Cache entschieden. Ein entsprechendes Patent hat Intel zugesprochen bekommen und darin wird ein Meteor-Lake-Prozessor gezeigt, der wie im ausführlichen Artikel beschrieben über einen passiven Interposer verfügt oder mit einem Adamantine getauften Interposer ausgestattet werden kann. Wie groß dieser L4-Cache geworden wäre, darüber gibt es noch keinerlei gesicherte Informationen. Gerüchten zufolge soll Intel Meteor Lake mit 128 bis 512 MB getestet haben.

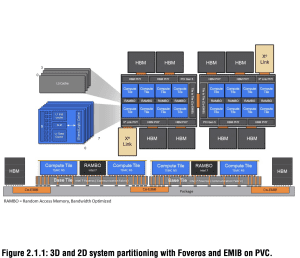

Einen SRAM im Interposer unterzubringen, ist allerdings auch keine neue Idee und wurde von Intel sogar schon umgesetzt. Genau darauf verweist Gelsinger in seiner Antwort. Ponte Vecchio sieht im Base-Tile 144 MB an L2-Cache vor. Auf dem Base-Tile sitzen die Compute-, Rambo-Cache und Xe-Link-Tiles.

Für Arrow Lake und nun potentiell für Lunar Lake und die folgenden Generationen könnte dies ähnlich aussehen. In der Umsetzung gibt es einen entscheidenen Unterschied: Während AMD den 3D V-Cache in Form eines SRAM auf das Compute-Chiplet setzt, platziert Intel den zusätzlichen Cache im Base-Tile und setzt die Tiles oben auf. Hinsichtlich der Kühlung scheint es dabei keine größeren Probleme zu geben, sonst hätte man die Technik für Ponte Vecchio nicht in dieser Form umgesetzt.

Die Frage die sich uns allerdings stellt, während der SRAM bei Ponte Vecchio als L2-Cache genutzt wurde, beschreibt das Adamantine-Patent ihn als L4-Cache. Die Cache-Ebenen machen aber einen entscheidenden Unterschied in dessen Nutzung. Von einem L4-Cache können die CPU-Kerne womöglich nicht in der Form profitieren, wie dies für einen L2- oder L3-Cache der Fall ist. AMD hat mit dem 3D V-Cache den L3-Cache erweitert, wovon die CPU-Leistung in den Ryzen-X3D-Modellen vor allem in Spielen profitiert hat.

In welcher Form wir den Stapel-Speicher bei Intel im Client-Segment also sehen werden, wird sich noch zeigen müssen. Eine große Überraschung sollten entsprechende Pläne aber nicht sein.