Werbung

Seit Mai 2020 war der Fugaku der schnellste Supercomputer, stand im Japan und wurde erst zwei Jahre später durch den Frontier mit AMD-Hardware abgelöst. Die Besonderheit des Fugaku war und ist, dass hier eigens entwickelte A64FX-Prozessoren von Fujitsu zum Einsatz kommen. Bei diesen handelt es sich um ARM-Prozessoren mit speziellen Vektor-Einheiten, die letztendlich für die hohe Rechenleitung des Supercomputers verantwortlich sind.

Nun hat Fujitsu ein mögliches Nachfolgedesign der A64FX-Prozessoren umrissen (via MONOist). Dass daraus auch ein neuer Supercomputer für Japan wird bzw. dieser auf den neuen Prozessoren basieren wird, ist unklar. Fujitsu beschreibt den Nachfolger als Datacenter- und AI-Prozessor und weniger als ein HPC-Design für einen Supercomputer. Aber genau wie die A64FX-Prozessoren soll auch die Monaka getaufte Design nicht nur einem Kunden zur Verfügung stehen, wenngleich sich beim Vorgänger fast alles auf den Fugaku konzentriert hat. Offenbar will man sich hier breiter aufstellen. Den A64FX findet man allenfalls noch in Testumgebungen wie am Leibniz-Rechenzentrum (LRZ). Einen signifikanten Marktanteil am Servermarkt konnte Fujitsu damit aber nie erlangen.

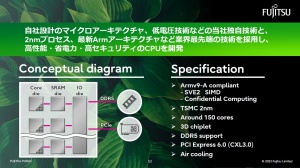

Geplant sind die Monaka-Prozessoren für 2027. Wieder soll eine ARMv9-Architektur die Basis der Mikroarchitektur sein. SVE2-Vektoreinheiten (Scalable Vector Extensions) spielen auch hier eine wichtige Rolle. Die Länge dieser Vektoreinheiten kann von 128 bis 2.048 Bit festgelegt werden. Bei den A64FX-Prozessoren können Vektoren mit einer Länge von 512 Bit in einem Durchlauf berechnet werden.

Etwa 150 dieser Prozessorkerne mit den angeschlossenen Vektoreinheiten sollen auf einem Core-Die ihren Platz finden. Gefertigt werden diesen Chips bei TSMC in 2 nm – wenn denn auf Seiten der Entwicklung und Fertigung alles nach Plan verläuft. An I/O-Funktionalität vorgesehen sind DDR5 als Speicher und für die Anbindung weiterer Beschleuniger bzw. externem Speicher PCI-Express 6.0 mit der Unterstützung von CXL 3.0.

Das Package soll ein 3D-Chiplet-Design werden. Ein Konzept-Diagramm zeigt mehrere Core-Dies und SRAM-Dies sowie einen großen I/O-Die. Die SRAM-Dies dürften auf die Core-Dies gestapelt werden, was den Begriff des 3D-Chiplets erklärt. Wie viele Core-Dies sich in einem Package befinden, dazu verrät Fujitsu allerdings nichts.

Weitere Details zum Monaka-Design werden sicherlich in den kommenden Monaten und Jahren folgen. Fujitsu zeigt an dieser Stelle aber schon einmal, dass man auch ein Stück vom Server-Kuchen abhaben möchte.