Werbung

Clearwater Forest soll mit seinen Efficiency-Kernen nicht nur aus Produktsicht ein herausragendes Produkt werden, sondern auch aus technischer Sicht. Bisher hat Intel in zahlreichen Gelegenheiten immer mal wieder einige kleine technische Details zu Clearwater Forest verkündet – so zum Beispiel die Fertigung in Intel 18A.

Ein von Intel veröffentlichtes Dokument (PDF), welches schon den Namen Clearwater Forest trägt, sonst aber eher länglich mit "Intel Delivers Cutting-Edge Process Technologies to the Data Center with Intel 18A and Advanced Chiplet Packaging" umschrieben ist, enthüllt nun einige Details der Fertigung von Clearwater Forest. Darauf gestoßen sind die Kollegen von ComputerBase.

Die Fertigung der Compute-Dies mit den Efficiency-Kernen wird in Intel 18A erfolgen – soweit ist dies keine Neuigkeit. Damit einher der Einsatz der RibbonFET und der rückseitigen Strom- und Spannungsversorgung mittels PowerVia. Clearwater Forest soll für Intel das Aushängeschild für die Fertigung in Intel 18A sein.

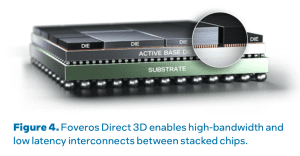

Zweites Highlight wird das Packaging sein. Auch hier wird es einige "Firsts" geben, also erstmalige Einsätze einer Technik. Dazu gehört unter anderem Foveros Direct 3D. Dies erlaubt eine vertikale Verbindung übereinander gestapelter Chiplets mit extrem geringen Bump-Abständen, was wiederum hohe Interconnect-Bandbreiten ermöglicht. Foveros Direct 3D nutzt ein Hybrid-Bonding zwischen den Kontaktpunkten der einzelnen Chips. Kupfer-Vias werden zueinander ausgerichtet zusammengebracht, was Intel als "thermocompression bonding of copper vias" beschreibt. Vergleichbar ist dies mit TSMCs SoIC-Technik wie es für den 3D V-Cache zum Einsatz kommt.

Laut Intel kann Foveros Direct 3D sowohl "Face-to-Face" wie "Face-to-Back" verwendet werden. Zudem ist es hier möglich, Wafer und Chips unterschiedlicher Hersteller zu verwenden. Die erste Generation von Foveros Direct 3D wird Bump-Abstände von 9 µm ermöglichen. In der nächsten werden es dann 3 µm sein.

Um die Verbindung mittels Foveros Direct 3D zu ermöglichen, wird Intel den Base-Die von Clearwater Forest in Intel 3-T fertigen lassen – einem der neuen Prozesse, die auf der IFS Direct Connect angekündigt wurden. Interessant ist hier zudem, dass Intel im Dokument einen lokalen Cache erwähnt, der im Base-Die sitzt:

"This unit of CPU chiplets sitting atop a large “local” cache becomes a complete compute module, which can then be replicated to scale up compute capability and create a SKU stack based on core count and cache requirements."

Erste Erfahrungen mit einem Cache im Base-Die sammelte Intel bereits mit Ponte Vecchio. Auch zu Meteor Lake gab es schon Gerüchte bezüglich eines Caches im Base-Die.

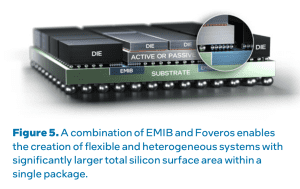

Eine weitere Packaging-Technik, die hier zum Einsatz kommen soll, ist EMIB 3.5D. EMIBs (Embedded Multi-die Integrated Bridge) hat Intel bereits vielfach im Einsatz – so auch bei Clearwater Forest. Die Kombination aus EMIB und Foveros nennt sich dann EMIB 3.5D. Es handelt sich aber um zwei getrennte Prozessschritte und Techniken. Die zweite Generation von EMIB reduziert den Bump-Abstand von 55 auf 45 µm – dies war aber schon vorher bekannt.

Der auf der Bühne gezeigte Chip von Clearwater Forest scheint über den Compute-Dies über zwei quadratische Cover aus Silizium zu verfügen. Oben und unten sind die beiden I/O-Dies zu erkennen, die wir auch schon bei Sierra Forest und Granite Rapids in diesem Jahr in ähnlicher Form sehen werden.