Werbung

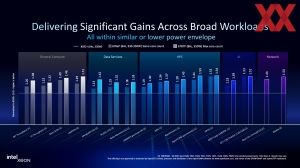

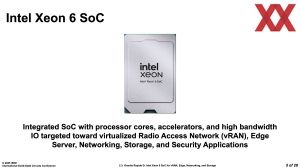

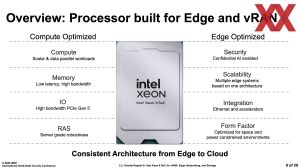

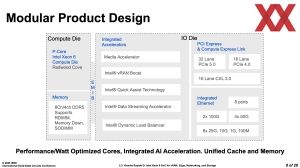

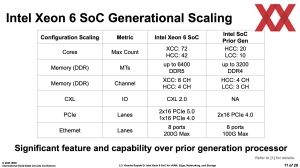

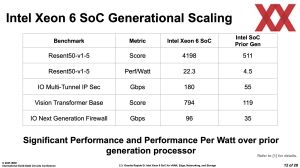

Für den Netzwerk- und sogenannten Edge-Bereich sieht Intel die Xeon 6 SoCs vor, die man zur HotChips erstmals vorgestellt hatte. Diese werden nun offiziell eingeführt und sollen mit bis zu 72 Kernen das beste Leistung/Watt-Verhältnis bieten. Um in diesen Bereichen die entsprechenden Ausstattungsmerkmale bieten zu können, nutzt man einerseits die AMX-Einheiten der verwendeten Performance-Kerne.

Über den I/O-Tile des Package, den wir uns noch genauer anschauen werden, werden zudem schnelle Netzwerkschnittstellen sowie die Möglichkeit, ein vRAN (Radio Access Network) anzubieten, bereitgestellt. Ein RAN ist der Teil eines Mobilfunknetzes, der die drahtlose Kommunikation zwischen Endgeräten und dem Kernnetzwerk ermöglicht.

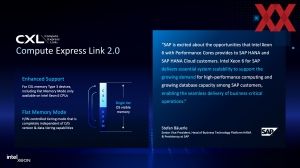

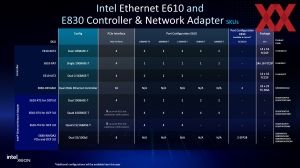

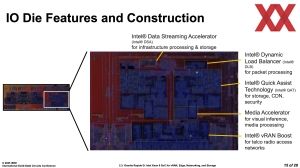

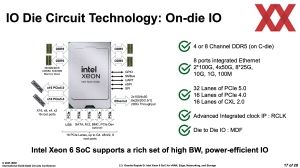

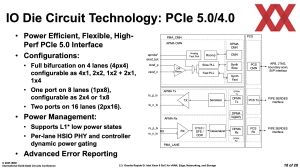

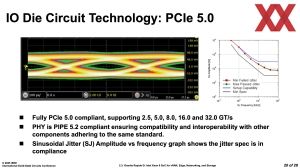

Für die schnelle Netzwerk-Kommunikation zur Verfügung stehen 2x 100GbE an Ethernet-Anbindung durch den Xeon 6 SoC. Der Chip bietet acht Ports, die als 1GbE, 10GbE, 25GbE, 50GbE oder 100GbE ausgelegt werden können. Maximal möglich sind 2x 100GbE und 4x 50GbE. Außerdem bietet der Xeon 6 SoC 32 PCI-Express-5.0- sowie jeweils 16 PCI-Express-4.0-, bzw. CXL-2.0-Lanes. Hinzu kommen die bekannten Beschleuniger wie Intels QuickAssist Technology, vRAN Boost, Dynamic Load Balancer und DataStreaming Accelerator.

Neben der Nutzung im Netzwerkbereich zeigt der Einsatz des DataStreaming-Beschleunigers bereits, dass der Xeon 6 SoC auch für Video-Services eingesetzt werden kann.

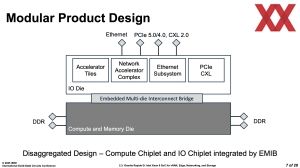

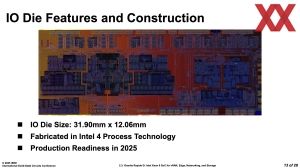

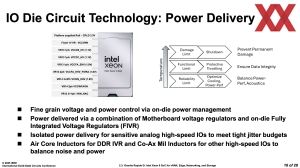

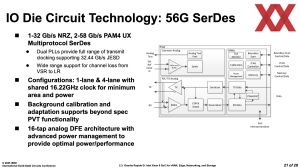

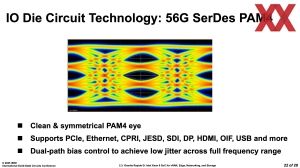

Für die Fertigung des Compute-Chiplets mit den Performance-Kernen setzt Intel auf die eigene Fertigung in Intel 3, die wir an anderer Stelle bereits genauer beleuchtet haben. Der I/O-Chiplet mit dem I/O-Fabric, den Ethernet-Controllern, Beschleunigern und SerDes für das Ethernet sowie PCIe und CXL wird in Intel 4 gefertigt. Für Sierra Forest-SP/AP und Granite Rapids-SP/AP setzt Intel auf Intel 7. Laut Intel hat man den Intel-4-Prozess so angepasst, dass er für diesen Anwendungsbereich ideal geeignet ist.

Mehr Details vom ISSCC 2025

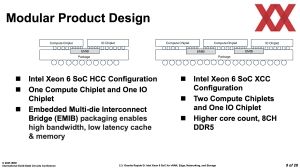

Auf der International Solid-State Circuits Conference (ISSCC) nannte Intel noch einige weitere Details. So kommt für den Xeon 6 SoC in einer HCC-Konfiguration (High Core Count) mit einem Compute-Tile und einem I/O-Tile. Die XCC-Konfiguration (Extreme Core Count) bringt es auf zwei Compute-Tiles und ebenfalls einen I/O-Tile.

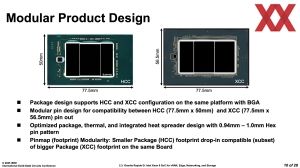

Auch wenn die beiden Packages eine unterschiedliche Größe von 77,5 x 50 mm (HCC) und 77,5 x 56,5 mm (XCC) aufweisen, so sind sie Pin-kompatibel zueinander. Auf einer Plattform können also wahlweise beide Varianten verlötet werden. Die Pinmap weist also eine gewisse Modularität auf.

In der Fertigung setzt Intel wie gesagt auf Intel 3 für den Compute-Tile und Intel 4 für den I/O-Tile. Das HCC-Package besitzt einen zusätzlichen Dummy-Chip in der Größe des I/O-Tile, der für einen gleichmäßigen Druck und eine bessere Verteilung der Abwärme sorgen soll.

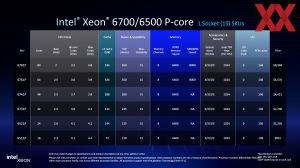

Da auf beiden Packages die gleichen I/O-Tiles zum Einsatz kommen, bieten beide die gleichen I/O-Funktionen. 2x 200GbE sowie 32x PCIe 5.0 und 16x PCIe 4.0 sind immer vorhanden. Die HCC-Variante kann bis zu 42 Kerne bereitstellen. Vier Speicherkanäle können mit DDR5-6400 bestückt werden. In der XCC-Variante sind es maximal 72 Kerne und acht Speicherkanäle.

Für den I/O-Tile machte Intel auf dem ISSCC angaben zur Größe. Der in Intel 4 gefertigte Chip kommt auf Abmessungen von rund 31,9 x 12,06 mm und damit eine Größe von 384,7 mm². Im I/O-Tile befinden sich ein Die-2-Die-Interface für die Anbindung an den Compute-Tile, der integrierten Beschleuniger und Ethernet-Controller. Dazu gehören die SerDes für das Ethernet sowie die PCI-Express/CXL-Lanes.