Werbung

In einem Video-Interview durch KitGuru äußerte sich Ori Lempel, Senior Principal Engineer in Core Design, zur aktuellen Entwicklung neuer Mikroarchitekturen durch das Intel Development Center (IDC) im israelischen Haifa, welches wir vor einigen Jahren selbst besucht haben.

Laut Lempel arbeitet das Designteam bereits am "Great-Grandchild" von Lion Cove, der aktuellen Mikroarchitektur der Performance-Kerne, wie sie in Lunar Lake und Arrow Lake zum Einsatz kommen. Offiziell hat Intel noch keinen Codenamen für das genannt, was nach Lion Cove kommen wird. Die für Panther Lake eingesetzte Mikroarchitektur wird allerdings auf den Namen Cougar Cove hören, dessen Nachfolger für Nova Lake wird als Coyote Cove gehandelt. Das was Lempel als Urenkel von Lion Cove bezeichnet, soll laut Gerüchten auf den Namen Griffin Cove hören.

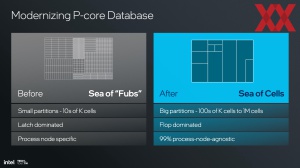

Zudem sprach Lempel darüber, wie sich Intel weiter unabhängig von einer spezifischen Fertigung (bei Intel oder extern) machen will. Diesen Plan hatte man bereits mit Lion Cove und dazu hat Intel zentrale Designrichtlinien der Mikroarchitektur überarbeitet. Das P-Kern-Design ist nicht länger in mehrere hundert sogenannte "FUBs" (Functional Units/Blocks) untergliedert, sondern setzt nun auf weniger, dafür wesentlich größere Zellen, die mehr Designelemente und letztlich auch mehr Transistoren integrieren.

Im Zuge dieser Neuausrichtung setzt Intel verstärkt auf Standardsoftware im EDA-Bereich und verlässt sich nicht mehr ausschließlich auf eigene Werkzeuge – ein Schritt, der die Zusammenarbeit mit Partnern wie TSMC spürbar vereinfacht. Letztlich entsteht so eine Mikroarchitektur, die sich vom jeweiligen Fertiger entkoppelt und es Intel erlaubt, Lion Cove in unterschiedlichen Varianten anzubieten und flexibel an spezifische Anforderungen anzupassen. Geplant war den Compute-Tile mit den Performance-Kernen für Arrow Lake in Intel 20A zu fertigen, während sie für Lunar Lake bei TSMC in die Auftragsfertigung gingen.

Für Panther Lake ist geplant den Compute-Tile in Intel 18A zu fertigen und in diesen Fertigungsprozess setzt Intel große Hoffnungen. Ob sich diese erfüllen werden, ist allerdings noch offen. In der zweiten Jahreshälfte 2025 sollen die ersten Notebook-Prozessoren auf Basis von Panther Lake erscheinen. Offenbar aber werden auch Cougar Cove, Coyote Cove und Griffin Cove derart Foundry-agnostisch entwickelt. Die Designteams wollen sich nicht mehr auf eine Fertigung verlassen müssen und alte Fehler wiederholen.

Intel erläutert des Fehlen von SMT

Mit Lion Cove verzichtete Intel auf den Einsatz von Simultaneous Multithreading (SMT) für die Performance-Kerne. Dies sorgte für einige Diskussionen und Mutmaßungen, warum man sich so entschieden hat.

Ori Lempel erklärt, dass jede Rechenlast (Workload) sowohl parallele als auch serielle Anteile enthält. Die parallelen Anteile lassen sich effizient auf mehrere Prozessorkerne verteilen und profitieren sowohl von steigender Kernanzahl als auch von Simultaneous Multithreading (SMT). SMT kann dabei zusätzliche Leistung aus einem Kern herausholen, indem mehrere Threads gleichzeitig abgearbeitet werden. Jedoch wirken sich diese Vorteile ausschließlich auf die parallelisierbaren Teile des Codes aus. Die seriellen Anteile – also jene, die nur schrittweise auf einem einzigen Kern verarbeitet werden können – werden durch SMT hingegen oft verlangsamt, da die Ressourcen eines Kerns auf mehrere Threads aufgeteilt werden müssen. Lempel weist darauf hin, dass allein durch das Aktivieren von SMT diese seriellen Komponenten bis zu 20 % langsamer ausgeführt werden können.

Wenn man die Kernanzahl weiter erhöht, stößt man an eine Grenze der Effizienz: SMT führt dann zunehmend zu künstlichen Engpässen, sogenannten "Thread Contention"-Problemen, bei denen sich Threads gegenseitig blockieren oder behindern. Diese entstehen dadurch, dass einzelne Aufgaben nur geringe Teile eines Kerns beanspruchen, aber dennoch viel Wartezeit im System verursachen. Das führt dazu, dass der Prozessor insgesamt ineffizient arbeitet, obwohl die theoretische Rechenkapazität hoch ist.

Zur Veranschaulichung verwendet Lempel das Bild von Arbeitern, die Steine aus dem Boden ziehen und in Kisten legen. Die Kisten symbolisieren die Prozessorkerne, und anfangs bringt die Vergrößerung der Anzahl von Arbeitern und Kisten Leistungssteigerungen. Doch je mehr man hinzufügt, desto mehr Zeit wird verschwendet, weil der eigentliche Engpass – das Herausziehen und Einlagern der Steine – nicht gleichzeitig schneller wird.

Zusammengefasst macht Lempel deutlich, dass steigende Parallelität und der Einsatz von SMT nur dann sinnvoll sind, wenn auch das zugrunde liegende Software- oder Systemdesign entsprechend angepasst wird. Andernfalls entstehen Ineffizienzen, die den theoretischen Leistungsvorteil zunichtemachen.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen