In einer Pressekonferenz gab Intel heute erste Details zur Nehalem-Architektur bekannt. Nehalem besitzt neben den bislang bereits angekündigten oder vermuteten Features ein skalierbares Design, welches es Intel ermöglicht, Prozessoren mit zwei bis acht Kernen auf dem Nehalem-Design zu erstellen. Die ersten Prozessoren - voraussichtlich monolithische Quad-Cores - sollen im vierten Quartal 2008 in Produktion gehen. Neben einem integrierten Memory-Controller, der 3-Channel-DDR3 unterstützt, einem verbesserten Hyperthreading und einem Quick-Path-Interconnect als neue I/O-Anbindung besitzt Nehalem auch einen Shared-Inclusive-L3-Cache. Beim Quad-Core wird dieser eine Größe von 8 MB besitzen. Sämtliche Nehalem-Bestandteile sind dynamisch an- und abschaltbar, weshalb Nehalem wohl auch beim Stromverbrauch punkten kann. Weitere Infos haben wir unter "Read More" zusammengefasst.

In einer Pressekonferenz gab Intel heute erste Details zur Nehalem-Architektur bekannt. Nehalem besitzt neben den bislang bereits angekündigten oder vermuteten Features ein skalierbares Design, welches es Intel ermöglicht, Prozessoren mit zwei bis acht Kernen auf dem Nehalem-Design zu erstellen. Die ersten Prozessoren - voraussichtlich monolithische Quad-Cores - sollen im vierten Quartal 2008 in Produktion gehen. Neben einem integrierten Memory-Controller, der 3-Channel-DDR3 unterstützt, einem verbesserten Hyperthreading und einem Quick-Path-Interconnect als neue I/O-Anbindung besitzt Nehalem auch einen Shared-Inclusive-L3-Cache. Beim Quad-Core wird dieser eine Größe von 8 MB besitzen. Sämtliche Nehalem-Bestandteile sind dynamisch an- und abschaltbar, weshalb Nehalem wohl auch beim Stromverbrauch punkten kann. Weitere Infos haben wir unter "Read More" zusammengefasst.Werbung

Der Nehalem-Wafer: Zu erkennen ist ein Prozessor-Die mit vier Kernen und vier großen Cachebereichen mit je 2 MB L3-Cache. Die Kerne sind SMT-Fähig, somit ist dieser Quad-Core in der Lage, 8 Threads gleichzeitig zu bearbeiten. Das Memory-Interface befindet sich am oberen Rand des Dies

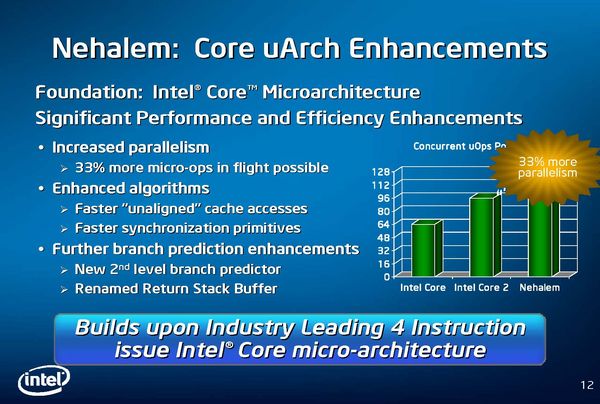

Nehalem basiert auf der Core-Architektur, die jedoch deutlich aufgebessert wurde. So ist Nehalems Architektur zwar weiterhin 4-fach skalar, jeder Kern kann also 4 Befehle gleichzeitig bearbeiten - Intels Netburst-Architektur und sämtliche aktuelle AMD-Prozessoren können nur 3 Befehle gleichzeitig abarbeiten. Verbessert wurden die Anzahl der gleichzeitig abzuarbeitenden µOps, neue Algorithmen für Speicherzugriffe, die "unaligned" stattfinden, implementiert, die Synchronisierung der Kerne überarbeitet und die Recheneinheit für die Sprungvorhersage verbessert.

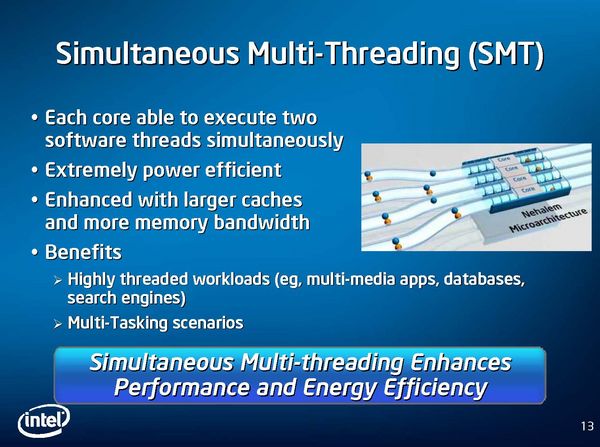

SMT (Simultaneous Multi-Threading) findet man ebenso wiederum im Nehalem, zuletzt besaßen alle Netburst-Prozessoren diese Technik. Die Technik hilft, die Prozessorkerne mit einer besseren Energieeffizienz zu nutzen, im Vergleich zur Netburst-Architektur wurde Hyperthreading hingegen noch einmal verbessert und kann aufgrund der Caches und der höheren Bandbreite effizienter arbeiten.

Hyperthreading is back: Aufgrund der HT-Technik können in einem 2-Way-Server mit zwei Quad-Core-Prozessoren sogar 16 Threads gleichzeitig bearbeitet werden.

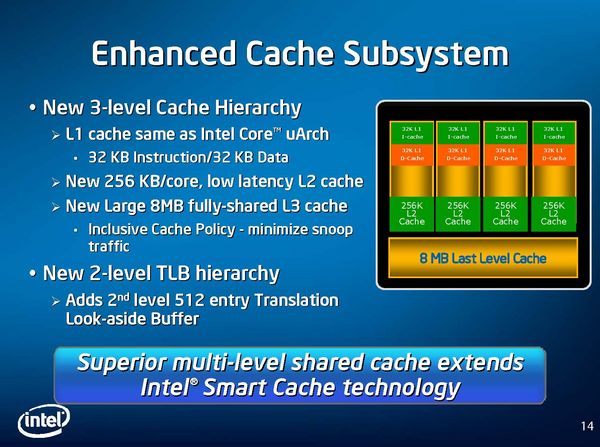

Interessant ist auch der Cache des Nehalem. Nehalem bekommt neben dem auch bei der Core-Architektur zu findenden L1-Daten- und Instruktions-Cache von je 32kB (µOps) einen 256 kB großen L2-Cache pro Kern. Einen Shared-L2-Cache wie bei der Core-Architektur gibt es also nicht mehr, jeder Cache hat seinen eigenen L2-Cache. Jedoch steht allen Kernen ein gemeinsamer L3-Cache mit 8 MB zur Verfügung, der die Daten der einzelnen Kerne "inklusive" speichert. Dies bedeutet, dass Daten im L1- und L2-Cache der Prozessoren auch im L3-Cache vorhanden sind. Dies mag als Verschwendung des kostbaren Cache-Speichers erscheinen, hat aber den entscheidenden Vorteil, dass ein Kern nur mit dem L3-Cache kommunizieren muss, wenn er Daten benötigt. Sind die Daten dort nicht vorhanden, liegen sie auch nicht in einem der L1- und L2-Caches der anderen Kerne. Somit wird eine Cache-Kohärenz erreicht bei gleichzeitig hoher Bandbreite.

Die Architektur mag einem vom AMD Phenom bekannt vorkommen, hier ist eine ähnliche Architektur für die Caches implementiert. Auch den Translation-Lookaside-Buffer (TLB) besitzt Intel in einer 2-Level-Ausführung - hoffendlich ohne Bug.

Hyperthreading is back: Aufgrund der HT-Technik können in einem 2-Way-Server mit zwei Quad-Core-Prozessoren sogar 16 Threads gleichzeitig bearbeitet werden.

Auch neue Chipsätze benötigt der Nehalem - ebenso wie einen neuen Sockel. Nehalem wird aufgrund des 25,6 GB/s schnellen Quick-Path-Interconnects (QPI) eine deutlich gesteigerte Bandbreite aufweisen, zudem laufen die Speicherzugriffe auf dem dedizierten Memory-Interface. Der Tylersburg-Chipsatz kann auch zwei QPI-Links zur Verfügung stellen und somit Dual-Sockel-Systeme mit zwei Nehalem-Prozessoren ermöglichen, die dann auch untereinander über ein QPI-Interface kommunizieren können. Für Desktop-Systeme wird der Typersburg-Chipsatz jedoch nur einen QPI-Link zur Verfügung stellen.

Der integrierte Speichercontroller des Nehalem unterstützt DDR3 mit bis zu 1333 MHz in einem Triple-Channel-Interface, insgesamt können drei Speichermodule pro Channel eingesetzt werden. Boards mit neun Speichersockeln wird es wohl aber eher nur im Serverbereich geben, im Desktop-Segment werden wohl aus ATX-Platzgründen nur drei oder sechs Slots üblich sein. Durch die Integration des Speichercontrollers wird die Latenz deutlich abgesenkt. Der Speichercontroller könnte dabei Intel einen ähnlichen Performance-Boost verschaffen, wie AMD ihn seinerzeit zur Einführung der Athlon-64-Architektur erreichen konnte.

Der Tylersburg-Chipsatz verkommt aufgrund des integrierten Memory-Controllers zu einem puren I/O-Hub.

Noch nichts sagte Intel zu der möglicherweise auch integrierten Grafik im Kern des Nehalem. Auch genaue Daten zum Erscheinungstermin, der TDP und dem Stromverbrauch, der Taktung und der tatsächlichen Performance gab man noch nicht. Nur einen Ausblick auf das Jahr 2009, denn dann folgt der nächste "Tick" des Tick-Tock-Modells: Die Nehalem-Architektur wird auf 32nm geshrinkt - der Codename für diese Architektur ist "Sandy Bidge".