HWL News Bot

News

Thread Starter

- Mitglied seit

- 06.03.2017

- Beiträge

- 114.386

... weiterlesen

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

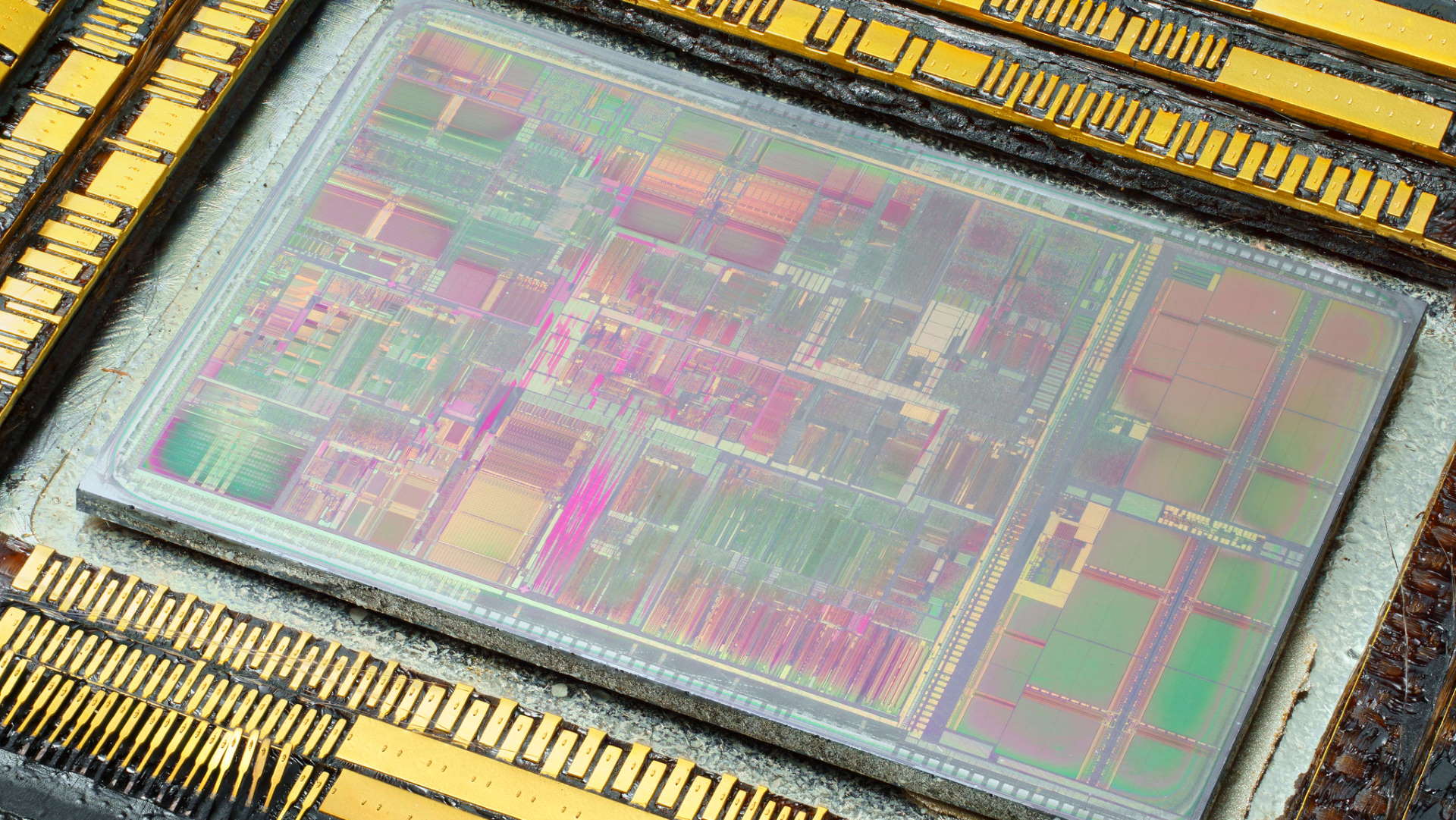

Es sei noch erwähnt, daß Intel mit dem 10nm+ auf das Compute-Die des i5-L16G7 49,4 MT/mm² gepackt hat. Das ist das Dichteste, was wir von Intel bisher in der Realität kennen. Ein Coffee Lake in 14nm++ soll auf 37,2 MT/mm² kommen. Intel ist sehr schweigsam, was seine Prozeßdichten über ein ganzes Die hinweg gemessen anbelangt...Eine in 8 nm bei Samsung gefertigte GA102-GPU kommt auf 44,56 MT/mm², die in 7 nm bei TSMC gefertigte GA100 auf 65,37 MT/mm².

Also die Gatelänge zu nehmen um die beiden zu vergleichen ist halt auch n bisschen komisch. Eigentlich greift man dafür auf die Kanallänge zurück, bzw Gatebreite.

Das haben wir auch gemacht. Die Kanallänge heißt aber Gatelänge. Die Breite wäre ja in Richtung der Finnen. Und da kommt es dann drauf an ob dein FinFet 2, 3, 5 oder wie viele Finnen auch immer hat. Das wäre aber für den Vergleich "noch schlechter" weil die Anzahl der Finnen vom Transistortyp abhängig ist.