Vielleicht stelle ich mir das auch einfach nur zu kompliziert vor und sehe daher keine einfach Lösung.

Wahrscheinlich das...

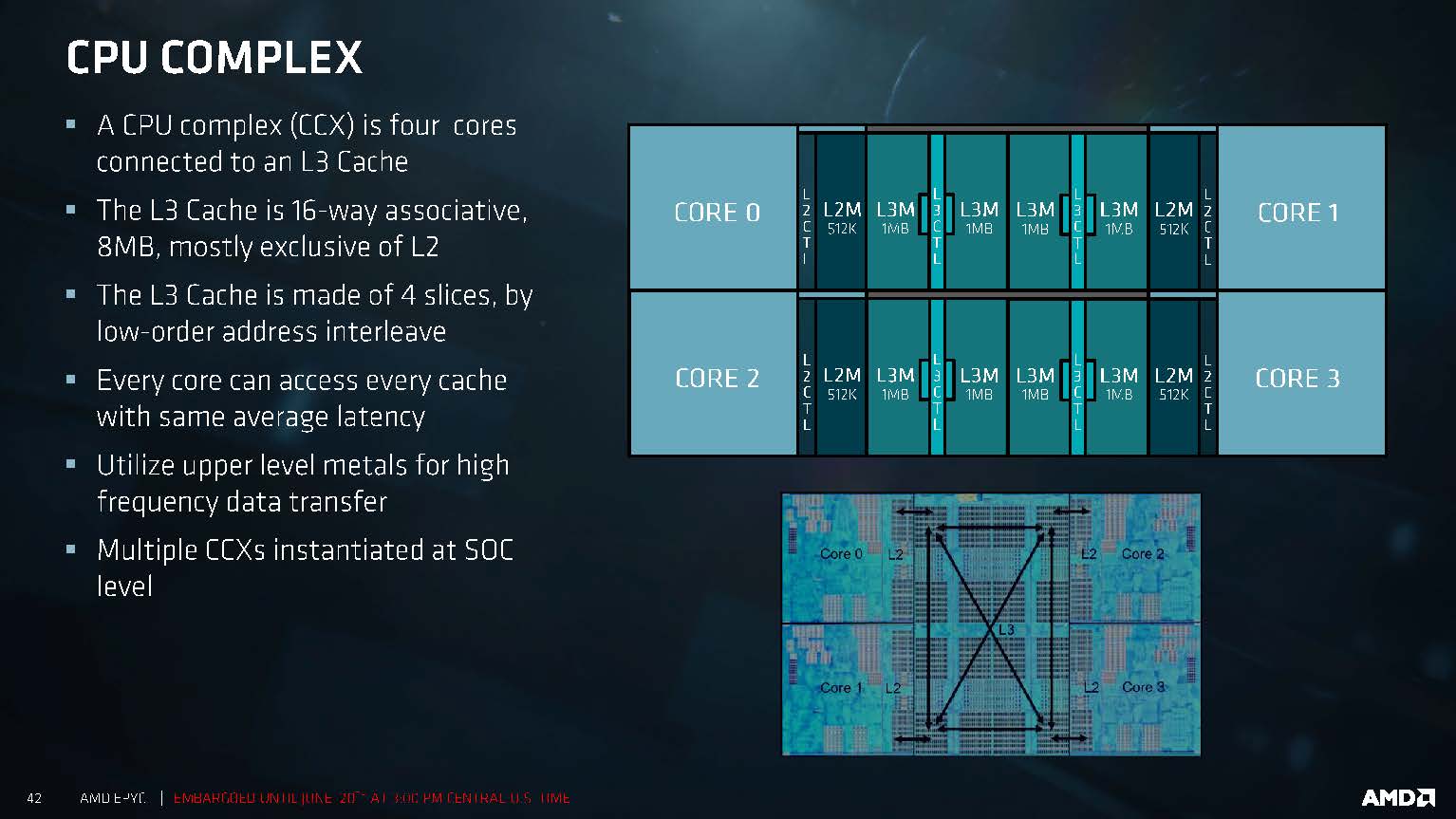

Ich würde mich nicht auf diese schematische Darstellung mit dem Kreuz im Viereck versteifen. Das ist halt nur ein Schema. Wie du auf dem DIE Shot sehen kannst ist das kein Kreuz in der Mitte, sondern da hängen quasi pro Core vier Blöcke Cache verbunden über diese "Mittelstege" zusammen.

Warum sollte man dort nicht jetzt einfach zwei weitere dieser Dinger dran bauen können?

Nimmt man das Schema 1:1, kreuzen sich die Datenleitungen in der Mitte, wenn das mit zwei Sachen geht, geht das mit drei auch. Dann bekommt halt jeder Cacheblock eine Verbindung mehr und du hast alle sechs Cores angebunden.

Wie man das am Ende genau realisiert, ist denke ich nicht das größte Problem. NV hat damals in den Details zur 970er Speicherproblematik bspw. erklärt, dass dort ne Crossbar mit acht "Beinchen" zum Einsatz kommt. Jeder L2 Cacheblock hängt dort an einem Beinchen. Die 970er hat nur 7 aktive Beinchen -> und damit einen Cache/ROP Block ohne Funktion.

Die Skalierung ist dort mit der Breite/Anzahl gegeben, da die Daten verteilt liegen... Was in dem Fall auch Notwendig ist, um eben vollen Speed zu bekommen.

Beim Ringbus von Intel hängt der Spaß an so einem Bussystem, wie die Cores intern auch. Bei Broadwell wurden zwei Blöcke "Cache" gegen den L4 Cache eingetauscht -> deswegen soll Broadwell eben weniger L3 Cache haben...

Mit dem Mesh auf SKL-X/SP verfolgt man hingegen nen anderen Ansatz - da hängt alles in einer Art Mesh zusammen, so dass die Wege möglichst fast immer gleich sind. Das mehrfach-Ringbus System von vorher hat da Übergänge zwischen den einzelnen Ringen notwendig (also mehrere Hobs zum Cachezugriff)

Wie man schön sieht - verschiedenste Produkte haben verschiedenste Ansätze, auch über die Uplink-Zahl 3 hinaus...

Dem könnte man durch einen höheren Takt der Data Fabric entgegenkommen, so wie man es aktuell bei Ryzen mit höherem Ramtakt macht.

Entgegenkommen sicher - mir stellt sich aber eben die Frage, wozu sollte man das machen?

Wer braucht denn einen 4C CCX Ansatz? Im Moment ist Raven Ridge der kleinste gemeinsame Nenner beim CCX (mit 1x CCX only) und dabei auch das Produkt, was eben aktuell im Nachsehen ggü. der Konkurenz (und ggü. dem Rest Portfolio) ist, weil man eben nicht mehr Cores bereit stellen kann.

Ein Doppel-CCX + GPU würde dann das APU Design über den Haufen werfen... Egal wie man es dreht, meiner Meinung nach spricht nichts für das Festhalten an 4C CCXen, vor allem wenn die APU eben mehr wie 4C bekommt - und davon gehe ich mit der Zen2 Architektur aus!

Bezogen auf den Mainstream stimme ich dir da zu, also bezogen auf die normalen Ryzen. Aber bei Threadripper können hier schon Vorteile ergeben. Die Latenzen sind laut dem Test von THG bei Die-To-Die (257ns) deutlich höher als bei Cross-CCX (178ns). Wenn jetzt 4 anstatt 2 CCX auf einem Die liegen, dann könnte man Threadripper Modelle bis 16 Kerne mit Latenzen im Cross-CCX-Bereich bringen und auch Threadripper Modelle mit 2 aktiven Dies könnten geringere Average Latenzen haben, wenn man durch schlaue Mechanismen die Die-to-Die-Kommunikation einschränkt. Letzteres würde dann auch für Epyc gelten.

6C CCXen wären aber noch mehr im Vorteil... Wenn das also der Grund sein soll, dann wäre es sogar noch sinniger, größere CCXen zu bauen anstatt "mehr" bei gleicher Core Anzahl.

Ich denke auch nicht, dass man bei AMD am Aufbau der Reihe groß was ändert. Der Epyc Server Prozessor wird weiter primär 1P-2P sein, vllt kommen noch größere Modelle, mal gucken. TR bekommt wieder ein Doppel-DIE Konstrukt und der Mainstream wird mit einem DIE verarztet.

Es spricht für mich nichts dafür, das bestehende Konstrukt derart einzureißen - nur um an 4C CCXen festzuhalten, die (siehe oben) aber in keinem Markt mehr gebraucht werden...

- - - Updated - - -

Durch den neuen Fertigungsprozess in 7 nm sowie eine vollkommen überarbeitete Architektur erwartet man nicht nur eine höhere Effizienz,

sondern auch eine signifikante Leistungssteigerung, welche an die aktuellen Vega-Grafikkarten sowie die Nvidia GeForce GTX 1080 herankommen soll, und das in der Mittelklasse.

Exakt das gleiche hat man bei Vega auch erwartet.

Wenn angeblich doch nicht so viel Budget bereit stehen würde frage ich mich ja, wie das immer im Vorfeld so hochgehypt werden kann?

Einfach mal abwarten - wenns was wird, wirds was, wenn nicht, dann eben nicht...