Thread Starter

- Mitglied seit

- 15.11.2002

- Beiträge

- 27.014

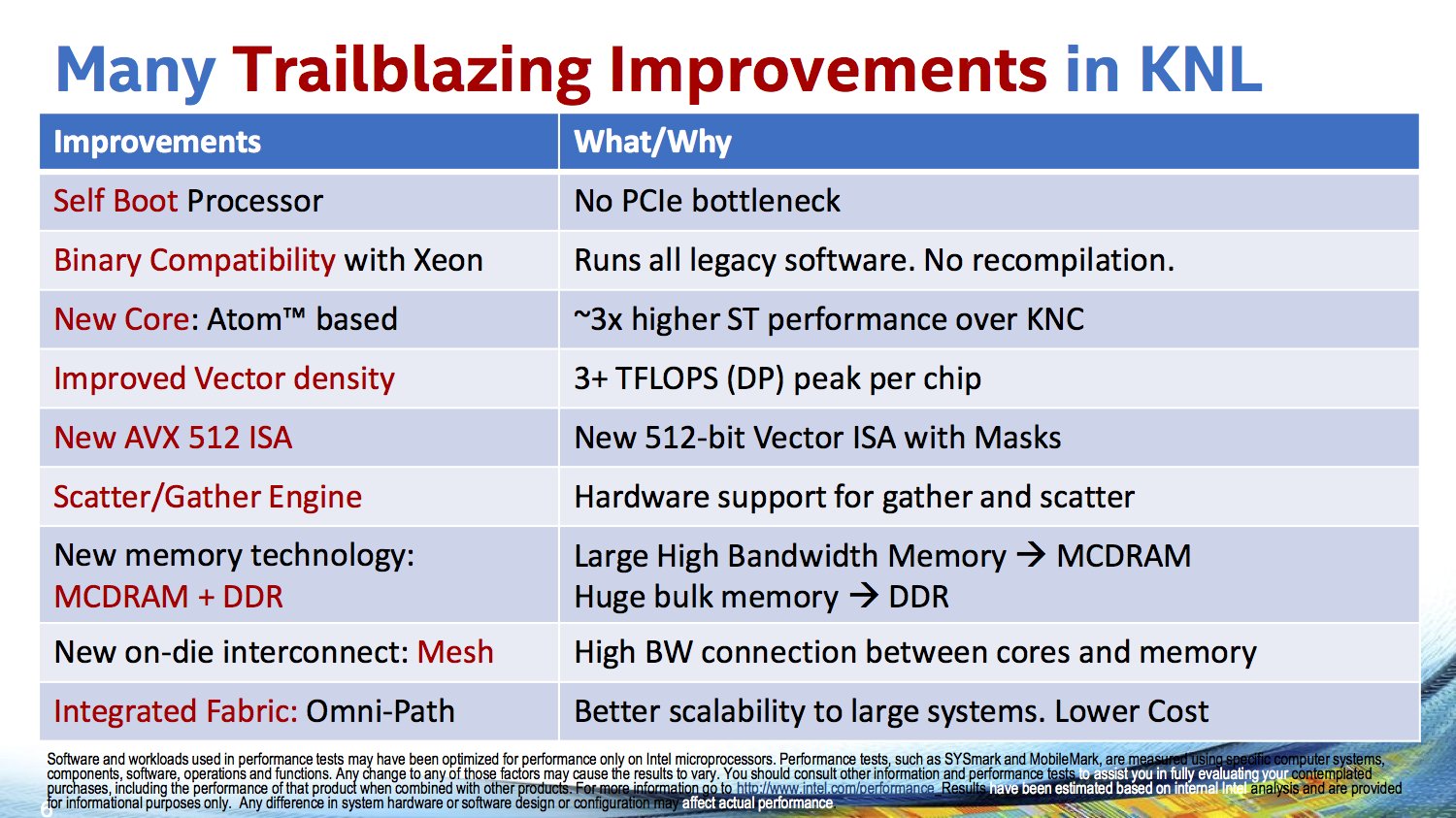

<p><img src="/images/stories/logos-2015/intel3.jpg" width="100" height="100" alt="intel3" style="margin: 10px; float: left;" />Gegen Ende des Jahres will Intel mit der nächsten Xeon-Phi-Generation starten. Die Knights-Landing-Generation wird im 14-nm-FinFET-Verfahren gefertigt und kommt auf 8 Milliarden Transistoren. Damit gehört dieser Chip zu den größten und komplexesten, die jemals von Intel gefertigt wurden.</p>

<p>Bisher ging man von einer <a href="index.php/news/hardware/prozessoren/34862-intel-xeon-phi-knights-landing-rechnet-auf-bis-zu-72-silvermont-kernen.html" target="_self">maximalen Ausbaustufe mit 72 Kernen auf Basis der Silvermont-Architektur</a> aus. Der Aufbau besteht dabei aus 36 Tiles oder Kacheln mit jeweils zwei Kernen. Auf der Hot-Chip-Konferenz erklärte...<br /><br /><a href="/index.php/news/hardware/prozessoren/36408-intel-knights-landing-mit-76-rechenkernen-vier-auf-reserve.html" style="font-weight:bold;">... weiterlesen</a></p>

<p>Bisher ging man von einer <a href="index.php/news/hardware/prozessoren/34862-intel-xeon-phi-knights-landing-rechnet-auf-bis-zu-72-silvermont-kernen.html" target="_self">maximalen Ausbaustufe mit 72 Kernen auf Basis der Silvermont-Architektur</a> aus. Der Aufbau besteht dabei aus 36 Tiles oder Kacheln mit jeweils zwei Kernen. Auf der Hot-Chip-Konferenz erklärte...<br /><br /><a href="/index.php/news/hardware/prozessoren/36408-intel-knights-landing-mit-76-rechenkernen-vier-auf-reserve.html" style="font-weight:bold;">... weiterlesen</a></p>

Halt wofür genau

Halt wofür genau

.

.