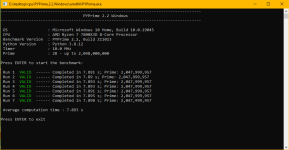

Komme mit gleichem cpu auf 9.256 im Durchschnitt ich denke dein IF geht in die Fehlercorrektur. versuch mal 2067. Sisoftsandra interthreadtest ist zum ausloten auch noch ein test um die core latency zu messen

Ich bin jetzt mal auf 2067 runter und habe da ein ähnliches Ergebnis. Kann das als Bestätigung gesehen werden, dass die Fehlerkorrektur beim IF aktuv war?

Welche Spannung müsste ich erhöhen, um gezielt den IF stabiler zu machen?

Interthread Test habe ich auch mal gemacht. Aber ich kann den leider garnicht deuten

SiSoftware Sandra

Benchmarkresultate

Allgemeine Inter-Thread-Bandbreite : 219.76GB/s

Ergebnisse : Höhere Werte sind besser.

Base 2 Ergebnis Multiplikatoren : 1GB(/s) = 1024MB(/s), 1MB(/s) = 1024kB(/s), 1kB(/s) = 1024 bytes(/s), usw.

Benchmarkresultate

Durchschnittliche Inter-Thread-Latenz : 39.4ns (8.0ns - 61.2ns)

Latenz zwischen Threads (gleicher Kern) : 8.3ns

Latenz zwischen Kernen (dasselbe Modul) : 17.9ns

Latenz zwischen Modulen (gleiches Paket) : 60.1ns

Ergebnisse : Geringere Werte sind besser.

Base 10 Ergebnis Multiplikatoren : 1s = 1000ms, 1ms = 1000µs, 1µs = 1000ns, usw.

Leistung pro Thread

Allgemeine Inter-Thread-Bandbreite : 6.87GB/s

Threadanzahl : 32

Ergebnisse : Höhere Werte sind besser.

Base 2 Ergebnis Multiplikatoren : 1GB(/s) = 1024MB(/s), 1MB(/s) = 1024kB(/s), 1kB(/s) = 1024 bytes(/s), usw.

Gegenüberstellung Leistung und Energieverbrauch

Prozessorleistung : 170.00W

Allgemeine Inter-Thread-Bandbreite : 1323.72MB/s/W

Ergebnisse : Höhere Werte sind besser.

Durchschnittliche Inter-Thread-Latenz : 2.32ns/W

Ergebnisse : Geringere Werte sind besser.

Gegenüberstellung Kapazität zu Leistung

Cachegröße gesamt : 484.89kB/W

Ergebnisse : Höhere Werte sind besser.

Gegenüberstellung Leistung und Geschwindigkeit

Allgemeine Inter-Thread-Bandbreite : 40.18MB/s/MHz

Ergebnisse : Höhere Werte sind besser.

Durchschnittliche Inter-Thread-Latenz : 0.07ns/MHz

Ergebnisse : Geringere Werte sind besser.

Benchmarkabbruch

Prozessorähnlichkeit : U0-U1 U2-U3 U4-U5 U6-U7 U8-U9 U10-U11 U12-U13 U14-U15 U16-U17 U18-U19 U20-U21 U22-U23 U24-U25 U26-U27 U28-U29 U30-U31

U0-M0C0T0 <> U2-M0C1T0 Latenzzeit Daten : 18.4ns

U0-M0C0T0 <> U4-M0C2T0 Latenzzeit Daten : 18.2ns

U0-M0C0T0 <> U6-M0C3T0 Latenzzeit Daten : 18.3ns

U0-M0C0T0 <> U8-M0C4T0 Latenzzeit Daten : 18.1ns

U0-M0C0T0 <> U10-M0C5T0 Latenzzeit Daten : 18.3ns

U0-M0C0T0 <> U12-M0C6T0 Latenzzeit Daten : 18.1ns

U0-M0C0T0 <> U14-M0C7T0 Latenzzeit Daten : 18.2ns

U0-M0C0T0 <> U16-M1C0T0 Latenzzeit Daten : 60.7ns

U0-M0C0T0 <> U18-M1C1T0 Latenzzeit Daten : 60.2ns

U0-M0C0T0 <> U20-M1C2T0 Latenzzeit Daten : 60.6ns

U0-M0C0T0 <> U22-M1C3T0 Latenzzeit Daten : 60.5ns

U0-M0C0T0 <> U24-M1C4T0 Latenzzeit Daten : 60.7ns

U0-M0C0T0 <> U26-M1C5T0 Latenzzeit Daten : 60.7ns

U0-M0C0T0 <> U28-M1C6T0 Latenzzeit Daten : 60.8ns

U0-M0C0T0 <> U30-M1C7T0 Latenzzeit Daten : 60.8ns

U0-M0C0T0 <> U1-M0C0T1 Latenzzeit Daten : 8.3ns

U0-M0C0T0 <> U3-M0C1T1 Latenzzeit Daten : 18.4ns

U0-M0C0T0 <> U5-M0C2T1 Latenzzeit Daten : 18.2ns

U0-M0C0T0 <> U7-M0C3T1 Latenzzeit Daten : 18.3ns

U0-M0C0T0 <> U9-M0C4T1 Latenzzeit Daten : 18.1ns

U0-M0C0T0 <> U11-M0C5T1 Latenzzeit Daten : 18.4ns

U0-M0C0T0 <> U13-M0C6T1 Latenzzeit Daten : 18.0ns

U0-M0C0T0 <> U15-M0C7T1 Latenzzeit Daten : 18.2ns

U0-M0C0T0 <> U17-M1C0T1 Latenzzeit Daten : 60.8ns

U0-M0C0T0 <> U19-M1C1T1 Latenzzeit Daten : 60.2ns

U0-M0C0T0 <> U21-M1C2T1 Latenzzeit Daten : 60.7ns

U0-M0C0T0 <> U23-M1C3T1 Latenzzeit Daten : 60.6ns

U0-M0C0T0 <> U25-M1C4T1 Latenzzeit Daten : 60.5ns

U0-M0C0T0 <> U27-M1C5T1 Latenzzeit Daten : 60.8ns

U0-M0C0T0 <> U29-M1C6T1 Latenzzeit Daten : 60.9ns

U0-M0C0T0 <> U31-M1C7T1 Latenzzeit Daten : 60.8ns

U2-M0C1T0 <> U4-M0C2T0 Latenzzeit Daten : 18.2ns

U2-M0C1T0 <> U6-M0C3T0 Latenzzeit Daten : 17.2ns

U2-M0C1T0 <> U8-M0C4T0 Latenzzeit Daten : 18.2ns

U2-M0C1T0 <> U10-M0C5T0 Latenzzeit Daten : 17.4ns

U2-M0C1T0 <> U12-M0C6T0 Latenzzeit Daten : 18.2ns

U2-M0C1T0 <> U14-M0C7T0 Latenzzeit Daten : 17.7ns

U2-M0C1T0 <> U16-M1C0T0 Latenzzeit Daten : 60.0ns

U2-M0C1T0 <> U18-M1C1T0 Latenzzeit Daten : 59.9ns

U2-M0C1T0 <> U20-M1C2T0 Latenzzeit Daten : 60.1ns

U2-M0C1T0 <> U22-M1C3T0 Latenzzeit Daten : 60.4ns

U2-M0C1T0 <> U24-M1C4T0 Latenzzeit Daten : 60.2ns

U2-M0C1T0 <> U26-M1C5T0 Latenzzeit Daten : 60.4ns

U2-M0C1T0 <> U28-M1C6T0 Latenzzeit Daten : 60.4ns

U2-M0C1T0 <> U30-M1C7T0 Latenzzeit Daten : 60.2ns

U2-M0C1T0 <> U1-M0C0T1 Latenzzeit Daten : 18.2ns

U2-M0C1T0 <> U3-M0C1T1 Latenzzeit Daten : 8.4ns

U2-M0C1T0 <> U5-M0C2T1 Latenzzeit Daten : 18.2ns

U2-M0C1T0 <> U7-M0C3T1 Latenzzeit Daten : 17.1ns

U2-M0C1T0 <> U9-M0C4T1 Latenzzeit Daten : 18.2ns

U2-M0C1T0 <> U11-M0C5T1 Latenzzeit Daten : 17.3ns

U2-M0C1T0 <> U13-M0C6T1 Latenzzeit Daten : 18.2ns

U2-M0C1T0 <> U15-M0C7T1 Latenzzeit Daten : 17.6ns

U2-M0C1T0 <> U17-M1C0T1 Latenzzeit Daten : 60.1ns

U2-M0C1T0 <> U19-M1C1T1 Latenzzeit Daten : 59.9ns

U2-M0C1T0 <> U21-M1C2T1 Latenzzeit Daten : 60.1ns

U2-M0C1T0 <> U23-M1C3T1 Latenzzeit Daten : 60.4ns

U2-M0C1T0 <> U25-M1C4T1 Latenzzeit Daten : 60.1ns

U2-M0C1T0 <> U27-M1C5T1 Latenzzeit Daten : 60.3ns

U2-M0C1T0 <> U29-M1C6T1 Latenzzeit Daten : 60.5ns

U2-M0C1T0 <> U31-M1C7T1 Latenzzeit Daten : 60.2ns

U4-M0C2T0 <> U6-M0C3T0 Latenzzeit Daten : 18.2ns

U4-M0C2T0 <> U8-M0C4T0 Latenzzeit Daten : 17.4ns

U4-M0C2T0 <> U10-M0C5T0 Latenzzeit Daten : 18.2ns

U4-M0C2T0 <> U12-M0C6T0 Latenzzeit Daten : 17.4ns

U4-M0C2T0 <> U14-M0C7T0 Latenzzeit Daten : 18.0ns

U4-M0C2T0 <> U16-M1C0T0 Latenzzeit Daten : 59.9ns

U4-M0C2T0 <> U18-M1C1T0 Latenzzeit Daten : 59.9ns

U4-M0C2T0 <> U20-M1C2T0 Latenzzeit Daten : 59.9ns

U4-M0C2T0 <> U22-M1C3T0 Latenzzeit Daten : 60.5ns

U4-M0C2T0 <> U24-M1C4T0 Latenzzeit Daten : 60.2ns

U4-M0C2T0 <> U26-M1C5T0 Latenzzeit Daten : 60.5ns

U4-M0C2T0 <> U28-M1C6T0 Latenzzeit Daten : 60.7ns

U4-M0C2T0 <> U30-M1C7T0 Latenzzeit Daten : 60.4ns

U4-M0C2T0 <> U1-M0C0T1 Latenzzeit Daten : 17.9ns

U4-M0C2T0 <> U3-M0C1T1 Latenzzeit Daten : 18.2ns

U4-M0C2T0 <> U5-M0C2T1 Latenzzeit Daten : 8.3ns

U4-M0C2T0 <> U7-M0C3T1 Latenzzeit Daten : 18.1ns

U4-M0C2T0 <> U9-M0C4T1 Latenzzeit Daten : 17.4ns

U4-M0C2T0 <> U11-M0C5T1 Latenzzeit Daten : 18.2ns

U4-M0C2T0 <> U13-M0C6T1 Latenzzeit Daten : 17.4ns

U4-M0C2T0 <> U15-M0C7T1 Latenzzeit Daten : 18.0ns

U4-M0C2T0 <> U17-M1C0T1 Latenzzeit Daten : 59.8ns

U4-M0C2T0 <> U19-M1C1T1 Latenzzeit Daten : 59.8ns

U4-M0C2T0 <> U21-M1C2T1 Latenzzeit Daten : 60.0ns

U4-M0C2T0 <> U23-M1C3T1 Latenzzeit Daten : 60.5ns

U4-M0C2T0 <> U25-M1C4T1 Latenzzeit Daten : 60.3ns

U4-M0C2T0 <> U27-M1C5T1 Latenzzeit Daten : 60.8ns

U4-M0C2T0 <> U29-M1C6T1 Latenzzeit Daten : 60.7ns

U4-M0C2T0 <> U31-M1C7T1 Latenzzeit Daten : 60.4ns

U6-M0C3T0 <> U8-M0C4T0 Latenzzeit Daten : 18.1ns

U6-M0C3T0 <> U10-M0C5T0 Latenzzeit Daten : 17.0ns

U6-M0C3T0 <> U12-M0C6T0 Latenzzeit Daten : 17.9ns

U6-M0C3T0 <> U14-M0C7T0 Latenzzeit Daten : 17.6ns

U6-M0C3T0 <> U16-M1C0T0 Latenzzeit Daten : 59.8ns

U6-M0C3T0 <> U18-M1C1T0 Latenzzeit Daten : 60.1ns

U6-M0C3T0 <> U20-M1C2T0 Latenzzeit Daten : 60.1ns

U6-M0C3T0 <> U22-M1C3T0 Latenzzeit Daten : 60.1ns

U6-M0C3T0 <> U24-M1C4T0 Latenzzeit Daten : 60.2ns

U6-M0C3T0 <> U26-M1C5T0 Latenzzeit Daten : 59.9ns

U6-M0C3T0 <> U28-M1C6T0 Latenzzeit Daten : 60.1ns

U6-M0C3T0 <> U30-M1C7T0 Latenzzeit Daten : 60.1ns

U6-M0C3T0 <> U1-M0C0T1 Latenzzeit Daten : 18.1ns

U6-M0C3T0 <> U3-M0C1T1 Latenzzeit Daten : 17.1ns

U6-M0C3T0 <> U5-M0C2T1 Latenzzeit Daten : 18.2ns

U6-M0C3T0 <> U7-M0C3T1 Latenzzeit Daten : 8.2ns

U6-M0C3T0 <> U9-M0C4T1 Latenzzeit Daten : 18.1ns

U6-M0C3T0 <> U11-M0C5T1 Latenzzeit Daten : 17.1ns

U6-M0C3T0 <> U13-M0C6T1 Latenzzeit Daten : 17.9ns

U6-M0C3T0 <> U15-M0C7T1 Latenzzeit Daten : 17.6ns

U6-M0C3T0 <> U17-M1C0T1 Latenzzeit Daten : 59.8ns

U6-M0C3T0 <> U19-M1C1T1 Latenzzeit Daten : 60.0ns

U6-M0C3T0 <> U21-M1C2T1 Latenzzeit Daten : 60.3ns

U6-M0C3T0 <> U23-M1C3T1 Latenzzeit Daten : 60.1ns

U6-M0C3T0 <> U25-M1C4T1 Latenzzeit Daten : 60.2ns

U6-M0C3T0 <> U27-M1C5T1 Latenzzeit Daten : 59.9ns

U6-M0C3T0 <> U29-M1C6T1 Latenzzeit Daten : 60.1ns

U6-M0C3T0 <> U31-M1C7T1 Latenzzeit Daten : 60.1ns

U8-M0C4T0 <> U10-M0C5T0 Latenzzeit Daten : 17.9ns

U8-M0C4T0 <> U12-M0C6T0 Latenzzeit Daten : 16.9ns

U8-M0C4T0 <> U14-M0C7T0 Latenzzeit Daten : 17.8ns

U8-M0C4T0 <> U16-M1C0T0 Latenzzeit Daten : 60.2ns

U8-M0C4T0 <> U18-M1C1T0 Latenzzeit Daten : 60.0ns

U8-M0C4T0 <> U20-M1C2T0 Latenzzeit Daten : 60.2ns

U8-M0C4T0 <> U22-M1C3T0 Latenzzeit Daten : 60.2ns

U8-M0C4T0 <> U24-M1C4T0 Latenzzeit Daten : 60.2ns

U8-M0C4T0 <> U26-M1C5T0 Latenzzeit Daten : 60.2ns

U8-M0C4T0 <> U28-M1C6T0 Latenzzeit Daten : 60.4ns

U8-M0C4T0 <> U30-M1C7T0 Latenzzeit Daten : 60.3ns

U8-M0C4T0 <> U1-M0C0T1 Latenzzeit Daten : 17.9ns

U8-M0C4T0 <> U3-M0C1T1 Latenzzeit Daten : 18.2ns

U8-M0C4T0 <> U5-M0C2T1 Latenzzeit Daten : 17.4ns

U8-M0C4T0 <> U7-M0C3T1 Latenzzeit Daten : 18.2ns

U8-M0C4T0 <> U9-M0C4T1 Latenzzeit Daten : 8.4ns

U8-M0C4T0 <> U11-M0C5T1 Latenzzeit Daten : 17.9ns

U8-M0C4T0 <> U13-M0C6T1 Latenzzeit Daten : 16.9ns

U8-M0C4T0 <> U15-M0C7T1 Latenzzeit Daten : 17.8ns

U8-M0C4T0 <> U17-M1C0T1 Latenzzeit Daten : 60.0ns

U8-M0C4T0 <> U19-M1C1T1 Latenzzeit Daten : 60.0ns

U8-M0C4T0 <> U21-M1C2T1 Latenzzeit Daten : 60.4ns

U8-M0C4T0 <> U23-M1C3T1 Latenzzeit Daten : 60.2ns

U8-M0C4T0 <> U25-M1C4T1 Latenzzeit Daten : 60.1ns

U8-M0C4T0 <> U27-M1C5T1 Latenzzeit Daten : 60.1ns

U8-M0C4T0 <> U29-M1C6T1 Latenzzeit Daten : 60.4ns

U8-M0C4T0 <> U31-M1C7T1 Latenzzeit Daten : 60.3ns

U10-M0C5T0 <> U12-M0C6T0 Latenzzeit Daten : 17.8ns

U10-M0C5T0 <> U14-M0C7T0 Latenzzeit Daten : 17.4ns

U10-M0C5T0 <> U16-M1C0T0 Latenzzeit Daten : 60.0ns

U10-M0C5T0 <> U18-M1C1T0 Latenzzeit Daten : 59.9ns

U10-M0C5T0 <> U20-M1C2T0 Latenzzeit Daten : 60.2ns

U10-M0C5T0 <> U22-M1C3T0 Latenzzeit Daten : 59.9ns

U10-M0C5T0 <> U24-M1C4T0 Latenzzeit Daten : 60.2ns

U10-M0C5T0 <> U26-M1C5T0 Latenzzeit Daten : 59.9ns

U10-M0C5T0 <> U28-M1C6T0 Latenzzeit Daten : 60.3ns

U10-M0C5T0 <> U30-M1C7T0 Latenzzeit Daten : 60.3ns

U10-M0C5T0 <> U1-M0C0T1 Latenzzeit Daten : 18.3ns

U10-M0C5T0 <> U3-M0C1T1 Latenzzeit Daten : 17.3ns

U10-M0C5T0 <> U5-M0C2T1 Latenzzeit Daten : 18.2ns

U10-M0C5T0 <> U7-M0C3T1 Latenzzeit Daten : 17.1ns

U10-M0C5T0 <> U9-M0C4T1 Latenzzeit Daten : 17.9ns

U10-M0C5T0 <> U11-M0C5T1 Latenzzeit Daten : 8.5ns

U10-M0C5T0 <> U13-M0C6T1 Latenzzeit Daten : 17.8ns

U10-M0C5T0 <> U15-M0C7T1 Latenzzeit Daten : 17.4ns

U10-M0C5T0 <> U17-M1C0T1 Latenzzeit Daten : 60.0ns

U10-M0C5T0 <> U19-M1C1T1 Latenzzeit Daten : 59.8ns

U10-M0C5T0 <> U21-M1C2T1 Latenzzeit Daten : 60.2ns

U10-M0C5T0 <> U23-M1C3T1 Latenzzeit Daten : 60.0ns

U10-M0C5T0 <> U25-M1C4T1 Latenzzeit Daten : 60.1ns

U10-M0C5T0 <> U27-M1C5T1 Latenzzeit Daten : 60.0ns

U10-M0C5T0 <> U29-M1C6T1 Latenzzeit Daten : 60.2ns

U10-M0C5T0 <> U31-M1C7T1 Latenzzeit Daten : 59.9ns

U12-M0C6T0 <> U14-M0C7T0 Latenzzeit Daten : 17.7ns

U12-M0C6T0 <> U16-M1C0T0 Latenzzeit Daten : 59.9ns

U12-M0C6T0 <> U18-M1C1T0 Latenzzeit Daten : 59.8ns

U12-M0C6T0 <> U20-M1C2T0 Latenzzeit Daten : 60.2ns

U12-M0C6T0 <> U22-M1C3T0 Latenzzeit Daten : 60.1ns

U12-M0C6T0 <> U24-M1C4T0 Latenzzeit Daten : 60.1ns

U12-M0C6T0 <> U26-M1C5T0 Latenzzeit Daten : 60.0ns

U12-M0C6T0 <> U28-M1C6T0 Latenzzeit Daten : 60.2ns

U12-M0C6T0 <> U30-M1C7T0 Latenzzeit Daten : 60.1ns

U12-M0C6T0 <> U1-M0C0T1 Latenzzeit Daten : 17.9ns

U12-M0C6T0 <> U3-M0C1T1 Latenzzeit Daten : 18.2ns

U12-M0C6T0 <> U5-M0C2T1 Latenzzeit Daten : 17.4ns

U12-M0C6T0 <> U7-M0C3T1 Latenzzeit Daten : 17.9ns

U12-M0C6T0 <> U9-M0C4T1 Latenzzeit Daten : 17.0ns

U12-M0C6T0 <> U11-M0C5T1 Latenzzeit Daten : 17.7ns

U12-M0C6T0 <> U13-M0C6T1 Latenzzeit Daten : 8.4ns

U12-M0C6T0 <> U15-M0C7T1 Latenzzeit Daten : 17.7ns

U12-M0C6T0 <> U17-M1C0T1 Latenzzeit Daten : 59.9ns

U12-M0C6T0 <> U19-M1C1T1 Latenzzeit Daten : 59.8ns

U12-M0C6T0 <> U21-M1C2T1 Latenzzeit Daten : 60.1ns

U12-M0C6T0 <> U23-M1C3T1 Latenzzeit Daten : 60.1ns

U12-M0C6T0 <> U25-M1C4T1 Latenzzeit Daten : 60.1ns

U12-M0C6T0 <> U27-M1C5T1 Latenzzeit Daten : 60.0ns

U12-M0C6T0 <> U29-M1C6T1 Latenzzeit Daten : 60.2ns

U12-M0C6T0 <> U31-M1C7T1 Latenzzeit Daten : 60.1ns

U14-M0C7T0 <> U16-M1C0T0 Latenzzeit Daten : 59.5ns

U14-M0C7T0 <> U18-M1C1T0 Latenzzeit Daten : 59.9ns

U14-M0C7T0 <> U20-M1C2T0 Latenzzeit Daten : 59.9ns

U14-M0C7T0 <> U22-M1C3T0 Latenzzeit Daten : 59.6ns

U14-M0C7T0 <> U24-M1C4T0 Latenzzeit Daten : 60.1ns

U14-M0C7T0 <> U26-M1C5T0 Latenzzeit Daten : 59.6ns

U14-M0C7T0 <> U28-M1C6T0 Latenzzeit Daten : 59.9ns

U14-M0C7T0 <> U30-M1C7T0 Latenzzeit Daten : 59.7ns

U14-M0C7T0 <> U1-M0C0T1 Latenzzeit Daten : 18.2ns

U14-M0C7T0 <> U3-M0C1T1 Latenzzeit Daten : 17.8ns

U14-M0C7T0 <> U5-M0C2T1 Latenzzeit Daten : 18.0ns

U14-M0C7T0 <> U7-M0C3T1 Latenzzeit Daten : 17.5ns

U14-M0C7T0 <> U9-M0C4T1 Latenzzeit Daten : 17.7ns

U14-M0C7T0 <> U11-M0C5T1 Latenzzeit Daten : 17.4ns

U14-M0C7T0 <> U13-M0C6T1 Latenzzeit Daten : 17.7ns

U14-M0C7T0 <> U15-M0C7T1 Latenzzeit Daten : 8.5ns

U14-M0C7T0 <> U17-M1C0T1 Latenzzeit Daten : 59.5ns

U14-M0C7T0 <> U19-M1C1T1 Latenzzeit Daten : 59.9ns

U14-M0C7T0 <> U21-M1C2T1 Latenzzeit Daten : 59.9ns

U14-M0C7T0 <> U23-M1C3T1 Latenzzeit Daten : 59.6ns

U14-M0C7T0 <> U25-M1C4T1 Latenzzeit Daten : 60.1ns

U14-M0C7T0 <> U27-M1C5T1 Latenzzeit Daten : 59.6ns

U14-M0C7T0 <> U29-M1C6T1 Latenzzeit Daten : 59.9ns

U14-M0C7T0 <> U31-M1C7T1 Latenzzeit Daten : 59.6ns

U16-M1C0T0 <> U18-M1C1T0 Latenzzeit Daten : 18.2ns

U16-M1C0T0 <> U20-M1C2T0 Latenzzeit Daten : 18.1ns

U16-M1C0T0 <> U22-M1C3T0 Latenzzeit Daten : 18.1ns

U16-M1C0T0 <> U24-M1C4T0 Latenzzeit Daten : 18.0ns

U16-M1C0T0 <> U26-M1C5T0 Latenzzeit Daten : 18.2ns

U16-M1C0T0 <> U28-M1C6T0 Latenzzeit Daten : 17.9ns

U16-M1C0T0 <> U30-M1C7T0 Latenzzeit Daten : 18.0ns

U16-M1C0T0 <> U1-M0C0T1 Latenzzeit Daten : 60.9ns

U16-M1C0T0 <> U3-M0C1T1 Latenzzeit Daten : 60.6ns

U16-M1C0T0 <> U5-M0C2T1 Latenzzeit Daten : 61.2ns

U16-M1C0T0 <> U7-M0C3T1 Latenzzeit Daten : 60.4ns

U16-M1C0T0 <> U9-M0C4T1 Latenzzeit Daten : 60.8ns

U16-M1C0T0 <> U11-M0C5T1 Latenzzeit Daten : 60.5ns

U16-M1C0T0 <> U13-M0C6T1 Latenzzeit Daten : 60.6ns

U16-M1C0T0 <> U15-M0C7T1 Latenzzeit Daten : 60.3ns

U16-M1C0T0 <> U17-M1C0T1 Latenzzeit Daten : 8.3ns

U16-M1C0T0 <> U19-M1C1T1 Latenzzeit Daten : 18.2ns

U16-M1C0T0 <> U21-M1C2T1 Latenzzeit Daten : 18.1ns

U16-M1C0T0 <> U23-M1C3T1 Latenzzeit Daten : 18.1ns

U16-M1C0T0 <> U25-M1C4T1 Latenzzeit Daten : 18.0ns

U16-M1C0T0 <> U27-M1C5T1 Latenzzeit Daten : 18.2ns

U16-M1C0T0 <> U29-M1C6T1 Latenzzeit Daten : 17.9ns

U16-M1C0T0 <> U31-M1C7T1 Latenzzeit Daten : 18.0ns

U18-M1C1T0 <> U20-M1C2T0 Latenzzeit Daten : 18.1ns

U18-M1C1T0 <> U22-M1C3T0 Latenzzeit Daten : 17.4ns

U18-M1C1T0 <> U24-M1C4T0 Latenzzeit Daten : 18.1ns

U18-M1C1T0 <> U26-M1C5T0 Latenzzeit Daten : 17.3ns

U18-M1C1T0 <> U28-M1C6T0 Latenzzeit Daten : 18.2ns

U18-M1C1T0 <> U30-M1C7T0 Latenzzeit Daten : 17.6ns

U18-M1C1T0 <> U1-M0C0T1 Latenzzeit Daten : 60.7ns

U18-M1C1T0 <> U3-M0C1T1 Latenzzeit Daten : 60.1ns

U18-M1C1T0 <> U5-M0C2T1 Latenzzeit Daten : 60.4ns

U18-M1C1T0 <> U7-M0C3T1 Latenzzeit Daten : 59.9ns

U18-M1C1T0 <> U9-M0C4T1 Latenzzeit Daten : 60.2ns

U18-M1C1T0 <> U11-M0C5T1 Latenzzeit Daten : 59.5ns

U18-M1C1T0 <> U13-M0C6T1 Latenzzeit Daten : 59.7ns

U18-M1C1T0 <> U15-M0C7T1 Latenzzeit Daten : 60.2ns

U18-M1C1T0 <> U17-M1C0T1 Latenzzeit Daten : 18.2ns

U18-M1C1T0 <> U19-M1C1T1 Latenzzeit Daten : 8.1ns

U18-M1C1T0 <> U21-M1C2T1 Latenzzeit Daten : 18.1ns

U18-M1C1T0 <> U23-M1C3T1 Latenzzeit Daten : 17.9ns

U18-M1C1T0 <> U25-M1C4T1 Latenzzeit Daten : 18.1ns

U18-M1C1T0 <> U27-M1C5T1 Latenzzeit Daten : 17.2ns

U18-M1C1T0 <> U29-M1C6T1 Latenzzeit Daten : 18.1ns

U18-M1C1T0 <> U31-M1C7T1 Latenzzeit Daten : 17.6ns

U20-M1C2T0 <> U22-M1C3T0 Latenzzeit Daten : 18.2ns

U20-M1C2T0 <> U24-M1C4T0 Latenzzeit Daten : 17.4ns

U20-M1C2T0 <> U26-M1C5T0 Latenzzeit Daten : 18.2ns

U20-M1C2T0 <> U28-M1C6T0 Latenzzeit Daten : 17.4ns

U20-M1C2T0 <> U30-M1C7T0 Latenzzeit Daten : 18.0ns

U20-M1C2T0 <> U1-M0C0T1 Latenzzeit Daten : 60.6ns

U20-M1C2T0 <> U3-M0C1T1 Latenzzeit Daten : 60.4ns

U20-M1C2T0 <> U5-M0C2T1 Latenzzeit Daten : 60.5ns

U20-M1C2T0 <> U7-M0C3T1 Latenzzeit Daten : 60.0ns

U20-M1C2T0 <> U9-M0C4T1 Latenzzeit Daten : 60.7ns

U20-M1C2T0 <> U11-M0C5T1 Latenzzeit Daten : 59.9ns

U20-M1C2T0 <> U13-M0C6T1 Latenzzeit Daten : 60.2ns

U20-M1C2T0 <> U15-M0C7T1 Latenzzeit Daten : 60.2ns

U20-M1C2T0 <> U17-M1C0T1 Latenzzeit Daten : 17.9ns

U20-M1C2T0 <> U19-M1C1T1 Latenzzeit Daten : 18.1ns

U20-M1C2T0 <> U21-M1C2T1 Latenzzeit Daten : 8.4ns

U20-M1C2T0 <> U23-M1C3T1 Latenzzeit Daten : 18.1ns

U20-M1C2T0 <> U25-M1C4T1 Latenzzeit Daten : 17.4ns

U20-M1C2T0 <> U27-M1C5T1 Latenzzeit Daten : 18.1ns

U20-M1C2T0 <> U29-M1C6T1 Latenzzeit Daten : 17.3ns

U20-M1C2T0 <> U31-M1C7T1 Latenzzeit Daten : 18.0ns

U22-M1C3T0 <> U24-M1C4T0 Latenzzeit Daten : 18.4ns

U22-M1C3T0 <> U26-M1C5T0 Latenzzeit Daten : 17.0ns

U22-M1C3T0 <> U28-M1C6T0 Latenzzeit Daten : 19.1ns

U22-M1C3T0 <> U30-M1C7T0 Latenzzeit Daten : 17.8ns

U22-M1C3T0 <> U1-M0C0T1 Latenzzeit Daten : 60.2ns

U22-M1C3T0 <> U3-M0C1T1 Latenzzeit Daten : 60.0ns

U22-M1C3T0 <> U5-M0C2T1 Latenzzeit Daten : 60.1ns

U22-M1C3T0 <> U7-M0C3T1 Latenzzeit Daten : 60.0ns

U22-M1C3T0 <> U9-M0C4T1 Latenzzeit Daten : 59.9ns

U22-M1C3T0 <> U11-M0C5T1 Latenzzeit Daten : 59.9ns

U22-M1C3T0 <> U13-M0C6T1 Latenzzeit Daten : 59.9ns

U22-M1C3T0 <> U15-M0C7T1 Latenzzeit Daten : 59.9ns

U22-M1C3T0 <> U17-M1C0T1 Latenzzeit Daten : 18.0ns

U22-M1C3T0 <> U19-M1C1T1 Latenzzeit Daten : 18.1ns

U22-M1C3T0 <> U21-M1C2T1 Latenzzeit Daten : 19.2ns

U22-M1C3T0 <> U23-M1C3T1 Latenzzeit Daten : 8.2ns

U22-M1C3T0 <> U25-M1C4T1 Latenzzeit Daten : 19.7ns

U22-M1C3T0 <> U27-M1C5T1 Latenzzeit Daten : 16.8ns

U22-M1C3T0 <> U29-M1C6T1 Latenzzeit Daten : 19.1ns

U22-M1C3T0 <> U31-M1C7T1 Latenzzeit Daten : 18.0ns

U24-M1C4T0 <> U26-M1C5T0 Latenzzeit Daten : 17.9ns

U24-M1C4T0 <> U28-M1C6T0 Latenzzeit Daten : 16.9ns

U24-M1C4T0 <> U30-M1C7T0 Latenzzeit Daten : 17.8ns

U24-M1C4T0 <> U1-M0C0T1 Latenzzeit Daten : 60.6ns

U24-M1C4T0 <> U3-M0C1T1 Latenzzeit Daten : 60.2ns

U24-M1C4T0 <> U5-M0C2T1 Latenzzeit Daten : 60.4ns

U24-M1C4T0 <> U7-M0C3T1 Latenzzeit Daten : 60.0ns

U24-M1C4T0 <> U9-M0C4T1 Latenzzeit Daten : 60.0ns

U24-M1C4T0 <> U11-M0C5T1 Latenzzeit Daten : 60.1ns

U24-M1C4T0 <> U13-M0C6T1 Latenzzeit Daten : 59.8ns

U24-M1C4T0 <> U15-M0C7T1 Latenzzeit Daten : 60.0ns

U24-M1C4T0 <> U17-M1C0T1 Latenzzeit Daten : 17.9ns

U24-M1C4T0 <> U19-M1C1T1 Latenzzeit Daten : 18.2ns

U24-M1C4T0 <> U21-M1C2T1 Latenzzeit Daten : 17.3ns

U24-M1C4T0 <> U23-M1C3T1 Latenzzeit Daten : 18.2ns

U24-M1C4T0 <> U25-M1C4T1 Latenzzeit Daten : 8.0ns

U24-M1C4T0 <> U27-M1C5T1 Latenzzeit Daten : 17.9ns

U24-M1C4T0 <> U29-M1C6T1 Latenzzeit Daten : 16.9ns

U24-M1C4T0 <> U31-M1C7T1 Latenzzeit Daten : 17.8ns

U26-M1C5T0 <> U28-M1C6T0 Latenzzeit Daten : 17.7ns

U26-M1C5T0 <> U30-M1C7T0 Latenzzeit Daten : 17.4ns

U26-M1C5T0 <> U1-M0C0T1 Latenzzeit Daten : 59.9ns

U26-M1C5T0 <> U3-M0C1T1 Latenzzeit Daten : 59.9ns

U26-M1C5T0 <> U5-M0C2T1 Latenzzeit Daten : 60.2ns

U26-M1C5T0 <> U7-M0C3T1 Latenzzeit Daten : 60.2ns

U26-M1C5T0 <> U9-M0C4T1 Latenzzeit Daten : 60.0ns

U26-M1C5T0 <> U11-M0C5T1 Latenzzeit Daten : 59.9ns

U26-M1C5T0 <> U13-M0C6T1 Latenzzeit Daten : 60.4ns

U26-M1C5T0 <> U15-M0C7T1 Latenzzeit Daten : 59.6ns

U26-M1C5T0 <> U17-M1C0T1 Latenzzeit Daten : 18.2ns

U26-M1C5T0 <> U19-M1C1T1 Latenzzeit Daten : 17.3ns

U26-M1C5T0 <> U21-M1C2T1 Latenzzeit Daten : 18.2ns

U26-M1C5T0 <> U23-M1C3T1 Latenzzeit Daten : 16.8ns

U26-M1C5T0 <> U25-M1C4T1 Latenzzeit Daten : 17.9ns

U26-M1C5T0 <> U27-M1C5T1 Latenzzeit Daten : 8.4ns

U26-M1C5T0 <> U29-M1C6T1 Latenzzeit Daten : 17.8ns

U26-M1C5T0 <> U31-M1C7T1 Latenzzeit Daten : 17.9ns

U28-M1C6T0 <> U30-M1C7T0 Latenzzeit Daten : 19.2ns

U28-M1C6T0 <> U1-M0C0T1 Latenzzeit Daten : 60.4ns

U28-M1C6T0 <> U3-M0C1T1 Latenzzeit Daten : 60.1ns

U28-M1C6T0 <> U5-M0C2T1 Latenzzeit Daten : 60.5ns

U28-M1C6T0 <> U7-M0C3T1 Latenzzeit Daten : 60.2ns

U28-M1C6T0 <> U9-M0C4T1 Latenzzeit Daten : 60.3ns

U28-M1C6T0 <> U11-M0C5T1 Latenzzeit Daten : 60.3ns

U28-M1C6T0 <> U13-M0C6T1 Latenzzeit Daten : 60.4ns

U28-M1C6T0 <> U15-M0C7T1 Latenzzeit Daten : 59.9ns

U28-M1C6T0 <> U17-M1C0T1 Latenzzeit Daten : 17.8ns

U28-M1C6T0 <> U19-M1C1T1 Latenzzeit Daten : 18.1ns

U28-M1C6T0 <> U21-M1C2T1 Latenzzeit Daten : 17.4ns

U28-M1C6T0 <> U23-M1C3T1 Latenzzeit Daten : 17.9ns

U28-M1C6T0 <> U25-M1C4T1 Latenzzeit Daten : 17.0ns

U28-M1C6T0 <> U27-M1C5T1 Latenzzeit Daten : 17.7ns

U28-M1C6T0 <> U29-M1C6T1 Latenzzeit Daten : 8.3ns

U28-M1C6T0 <> U31-M1C7T1 Latenzzeit Daten : 17.7ns

U30-M1C7T0 <> U1-M0C0T1 Latenzzeit Daten : 59.6ns

U30-M1C7T0 <> U3-M0C1T1 Latenzzeit Daten : 60.1ns

U30-M1C7T0 <> U5-M0C2T1 Latenzzeit Daten : 60.1ns

U30-M1C7T0 <> U7-M0C3T1 Latenzzeit Daten : 59.8ns

U30-M1C7T0 <> U9-M0C4T1 Latenzzeit Daten : 60.1ns

U30-M1C7T0 <> U11-M0C5T1 Latenzzeit Daten : 60.0ns

U30-M1C7T0 <> U13-M0C6T1 Latenzzeit Daten : 60.0ns

U30-M1C7T0 <> U15-M0C7T1 Latenzzeit Daten : 59.8ns

U30-M1C7T0 <> U17-M1C0T1 Latenzzeit Daten : 18.2ns

U30-M1C7T0 <> U19-M1C1T1 Latenzzeit Daten : 17.7ns

U30-M1C7T0 <> U21-M1C2T1 Latenzzeit Daten : 17.9ns

U30-M1C7T0 <> U23-M1C3T1 Latenzzeit Daten : 17.5ns

U30-M1C7T0 <> U25-M1C4T1 Latenzzeit Daten : 17.7ns

U30-M1C7T0 <> U27-M1C5T1 Latenzzeit Daten : 17.3ns

U30-M1C7T0 <> U29-M1C6T1 Latenzzeit Daten : 17.7ns

U30-M1C7T0 <> U31-M1C7T1 Latenzzeit Daten : 8.3ns

U1-M0C0T1 <> U3-M0C1T1 Latenzzeit Daten : 18.3ns

U1-M0C0T1 <> U5-M0C2T1 Latenzzeit Daten : 18.2ns

U1-M0C0T1 <> U7-M0C3T1 Latenzzeit Daten : 18.2ns

U1-M0C0T1 <> U9-M0C4T1 Latenzzeit Daten : 18.0ns

U1-M0C0T1 <> U11-M0C5T1 Latenzzeit Daten : 18.2ns

U1-M0C0T1 <> U13-M0C6T1 Latenzzeit Daten : 18.0ns

U1-M0C0T1 <> U15-M0C7T1 Latenzzeit Daten : 18.1ns

U1-M0C0T1 <> U17-M1C0T1 Latenzzeit Daten : 60.5ns

U1-M0C0T1 <> U19-M1C1T1 Latenzzeit Daten : 59.9ns

U1-M0C0T1 <> U21-M1C2T1 Latenzzeit Daten : 60.3ns

U1-M0C0T1 <> U23-M1C3T1 Latenzzeit Daten : 60.2ns

U1-M0C0T1 <> U25-M1C4T1 Latenzzeit Daten : 60.2ns

U1-M0C0T1 <> U27-M1C5T1 Latenzzeit Daten : 60.4ns

U1-M0C0T1 <> U29-M1C6T1 Latenzzeit Daten : 60.5ns

U1-M0C0T1 <> U31-M1C7T1 Latenzzeit Daten : 60.2ns

U3-M0C1T1 <> U5-M0C2T1 Latenzzeit Daten : 18.2ns

U3-M0C1T1 <> U7-M0C3T1 Latenzzeit Daten : 17.4ns

U3-M0C1T1 <> U9-M0C4T1 Latenzzeit Daten : 18.2ns

U3-M0C1T1 <> U11-M0C5T1 Latenzzeit Daten : 17.2ns

U3-M0C1T1 <> U13-M0C6T1 Latenzzeit Daten : 18.1ns

U3-M0C1T1 <> U15-M0C7T1 Latenzzeit Daten : 17.6ns

U3-M0C1T1 <> U17-M1C0T1 Latenzzeit Daten : 59.7ns

U3-M0C1T1 <> U19-M1C1T1 Latenzzeit Daten : 59.9ns

U3-M0C1T1 <> U21-M1C2T1 Latenzzeit Daten : 60.0ns

U3-M0C1T1 <> U23-M1C3T1 Latenzzeit Daten : 60.3ns

U3-M0C1T1 <> U25-M1C4T1 Latenzzeit Daten : 60.2ns

U3-M0C1T1 <> U27-M1C5T1 Latenzzeit Daten : 60.2ns

U3-M0C1T1 <> U29-M1C6T1 Latenzzeit Daten : 60.3ns

U3-M0C1T1 <> U31-M1C7T1 Latenzzeit Daten : 60.1ns

U5-M0C2T1 <> U7-M0C3T1 Latenzzeit Daten : 18.1ns

U5-M0C2T1 <> U9-M0C4T1 Latenzzeit Daten : 17.3ns

U5-M0C2T1 <> U11-M0C5T1 Latenzzeit Daten : 18.1ns

U5-M0C2T1 <> U13-M0C6T1 Latenzzeit Daten : 17.4ns

U5-M0C2T1 <> U15-M0C7T1 Latenzzeit Daten : 18.0ns

U5-M0C2T1 <> U17-M1C0T1 Latenzzeit Daten : 59.9ns

U5-M0C2T1 <> U19-M1C1T1 Latenzzeit Daten : 59.8ns

U5-M0C2T1 <> U21-M1C2T1 Latenzzeit Daten : 60.0ns

U5-M0C2T1 <> U23-M1C3T1 Latenzzeit Daten : 60.4ns

U5-M0C2T1 <> U25-M1C4T1 Latenzzeit Daten : 60.3ns

U5-M0C2T1 <> U27-M1C5T1 Latenzzeit Daten : 60.5ns

U5-M0C2T1 <> U29-M1C6T1 Latenzzeit Daten : 60.5ns

U5-M0C2T1 <> U31-M1C7T1 Latenzzeit Daten : 60.5ns

U7-M0C3T1 <> U9-M0C4T1 Latenzzeit Daten : 18.2ns

U7-M0C3T1 <> U11-M0C5T1 Latenzzeit Daten : 17.0ns

U7-M0C3T1 <> U13-M0C6T1 Latenzzeit Daten : 17.9ns

U7-M0C3T1 <> U15-M0C7T1 Latenzzeit Daten : 17.6ns

U7-M0C3T1 <> U17-M1C0T1 Latenzzeit Daten : 59.8ns

U7-M0C3T1 <> U19-M1C1T1 Latenzzeit Daten : 59.9ns

U7-M0C3T1 <> U21-M1C2T1 Latenzzeit Daten : 60.2ns

U7-M0C3T1 <> U23-M1C3T1 Latenzzeit Daten : 60.0ns

U7-M0C3T1 <> U25-M1C4T1 Latenzzeit Daten : 60.4ns

U7-M0C3T1 <> U27-M1C5T1 Latenzzeit Daten : 59.9ns

U7-M0C3T1 <> U29-M1C6T1 Latenzzeit Daten : 60.2ns

U7-M0C3T1 <> U31-M1C7T1 Latenzzeit Daten : 60.0ns

U9-M0C4T1 <> U11-M0C5T1 Latenzzeit Daten : 17.9ns

U9-M0C4T1 <> U13-M0C6T1 Latenzzeit Daten : 16.9ns

U9-M0C4T1 <> U15-M0C7T1 Latenzzeit Daten : 17.8ns

U9-M0C4T1 <> U17-M1C0T1 Latenzzeit Daten : 59.9ns

U9-M0C4T1 <> U19-M1C1T1 Latenzzeit Daten : 60.0ns

U9-M0C4T1 <> U21-M1C2T1 Latenzzeit Daten : 60.4ns

U9-M0C4T1 <> U23-M1C3T1 Latenzzeit Daten : 60.2ns

U9-M0C4T1 <> U25-M1C4T1 Latenzzeit Daten : 60.1ns

U9-M0C4T1 <> U27-M1C5T1 Latenzzeit Daten : 60.1ns

U9-M0C4T1 <> U29-M1C6T1 Latenzzeit Daten : 60.5ns

U9-M0C4T1 <> U31-M1C7T1 Latenzzeit Daten : 60.3ns

U11-M0C5T1 <> U13-M0C6T1 Latenzzeit Daten : 17.8ns

U11-M0C5T1 <> U15-M0C7T1 Latenzzeit Daten : 17.4ns

U11-M0C5T1 <> U17-M1C0T1 Latenzzeit Daten : 59.8ns

U11-M0C5T1 <> U19-M1C1T1 Latenzzeit Daten : 60.0ns

U11-M0C5T1 <> U21-M1C2T1 Latenzzeit Daten : 60.2ns

U11-M0C5T1 <> U23-M1C3T1 Latenzzeit Daten : 60.1ns

U11-M0C5T1 <> U25-M1C4T1 Latenzzeit Daten : 60.1ns

U11-M0C5T1 <> U27-M1C5T1 Latenzzeit Daten : 60.0ns

U11-M0C5T1 <> U29-M1C6T1 Latenzzeit Daten : 60.2ns

U11-M0C5T1 <> U31-M1C7T1 Latenzzeit Daten : 59.9ns

U13-M0C6T1 <> U15-M0C7T1 Latenzzeit Daten : 17.7ns

U13-M0C6T1 <> U17-M1C0T1 Latenzzeit Daten : 60.2ns

U13-M0C6T1 <> U19-M1C1T1 Latenzzeit Daten : 59.9ns

U13-M0C6T1 <> U21-M1C2T1 Latenzzeit Daten : 60.1ns

U13-M0C6T1 <> U23-M1C3T1 Latenzzeit Daten : 60.0ns

U13-M0C6T1 <> U25-M1C4T1 Latenzzeit Daten : 60.1ns

U13-M0C6T1 <> U27-M1C5T1 Latenzzeit Daten : 60.0ns

U13-M0C6T1 <> U29-M1C6T1 Latenzzeit Daten : 60.2ns

U13-M0C6T1 <> U31-M1C7T1 Latenzzeit Daten : 60.1ns

U15-M0C7T1 <> U17-M1C0T1 Latenzzeit Daten : 59.7ns

U15-M0C7T1 <> U19-M1C1T1 Latenzzeit Daten : 59.9ns

U15-M0C7T1 <> U21-M1C2T1 Latenzzeit Daten : 60.0ns

U15-M0C7T1 <> U23-M1C3T1 Latenzzeit Daten : 59.7ns

U15-M0C7T1 <> U25-M1C4T1 Latenzzeit Daten : 60.0ns

U15-M0C7T1 <> U27-M1C5T1 Latenzzeit Daten : 59.6ns

U15-M0C7T1 <> U29-M1C6T1 Latenzzeit Daten : 60.0ns

U15-M0C7T1 <> U31-M1C7T1 Latenzzeit Daten : 59.7ns

U17-M1C0T1 <> U19-M1C1T1 Latenzzeit Daten : 18.2ns

U17-M1C0T1 <> U21-M1C2T1 Latenzzeit Daten : 18.1ns

U17-M1C0T1 <> U23-M1C3T1 Latenzzeit Daten : 18.1ns

U17-M1C0T1 <> U25-M1C4T1 Latenzzeit Daten : 17.9ns

U17-M1C0T1 <> U27-M1C5T1 Latenzzeit Daten : 18.2ns

U17-M1C0T1 <> U29-M1C6T1 Latenzzeit Daten : 17.9ns

U17-M1C0T1 <> U31-M1C7T1 Latenzzeit Daten : 18.0ns

U19-M1C1T1 <> U21-M1C2T1 Latenzzeit Daten : 18.1ns

U19-M1C1T1 <> U23-M1C3T1 Latenzzeit Daten : 18.0ns

U19-M1C1T1 <> U25-M1C4T1 Latenzzeit Daten : 18.2ns

U19-M1C1T1 <> U27-M1C5T1 Latenzzeit Daten : 17.3ns

U19-M1C1T1 <> U29-M1C6T1 Latenzzeit Daten : 18.2ns

U19-M1C1T1 <> U31-M1C7T1 Latenzzeit Daten : 17.6ns

U21-M1C2T1 <> U23-M1C3T1 Latenzzeit Daten : 18.1ns

U21-M1C2T1 <> U25-M1C4T1 Latenzzeit Daten : 17.3ns

U21-M1C2T1 <> U27-M1C5T1 Latenzzeit Daten : 18.1ns

U21-M1C2T1 <> U29-M1C6T1 Latenzzeit Daten : 17.4ns

U21-M1C2T1 <> U31-M1C7T1 Latenzzeit Daten : 18.0ns

U23-M1C3T1 <> U25-M1C4T1 Latenzzeit Daten : 18.9ns

U23-M1C3T1 <> U27-M1C5T1 Latenzzeit Daten : 16.6ns

U23-M1C3T1 <> U29-M1C6T1 Latenzzeit Daten : 19.2ns

U23-M1C3T1 <> U31-M1C7T1 Latenzzeit Daten : 17.4ns

U25-M1C4T1 <> U27-M1C5T1 Latenzzeit Daten : 17.9ns

U25-M1C4T1 <> U29-M1C6T1 Latenzzeit Daten : 16.9ns

U25-M1C4T1 <> U31-M1C7T1 Latenzzeit Daten : 17.8ns

U27-M1C5T1 <> U29-M1C6T1 Latenzzeit Daten : 17.7ns

U27-M1C5T1 <> U31-M1C7T1 Latenzzeit Daten : 17.6ns

U29-M1C6T1 <> U31-M1C7T1 Latenzzeit Daten : 17.8ns

Inter-Core Bandbreite @ 1x 64bytes : 20.69GB/s

Inter-Core Bandbreite @ 4x 64bytes : 33.2GB/s

Inter-Core Bandbreite @ 4x 256bytes : 129.28GB/s

Inter-Core Bandbreite @ 4x 1kB : 409.36GB/s

Inter-Core Bandbreite @ 4x 4kB : 567.89GB/s

Inter-Core Bandbreite @ 16x 4kB : 760.72GB/s

Inter-Core Bandbreite @ 4x 64kB : 1.1TB/s

Inter-Core Bandbreite @ 16x 64kB : 1.08TB/s

Inter-Core Bandbreite @ 8x 256kB : 831GB/s

Inter-Core Bandbreite @ 4x 1MB : 779.15GB/s

Inter-Core Bandbreite @ 16x 1MB : 34GB/s

Inter-Core Bandbreite @ 8x 4MB : 29.3GB/s

Leistungsteststatus

Ergebnis-ID : AMD Ryzen 9 7950X 16-Core Processor (2M 16C 32T 5.6GHz, 933MHz IMC, 16x 1MB L2, 2x 32MB L3)

Microcode : A60F12-1203

System : GigaByte X670 AORUS ELITE AX X670 MB

Kompatibel mit Plattform : x64

Threadanzahl : 32

Systemtakt : 10MHz

Speicherseitengröße : 2MB

Prozessor

Modell : AMD Ryzen 9 7950X 16-Core Processor

URL :

https://www.amd.com

Revision/Stepping : 61 / 2

Microcode : A60F12-1203

Aktuellste Version : A60F12-1206

Front Side Bus Geschwindigkeit : 100MHz

Nennleistung (TDP) : 170.00W

Prozessormodule

Module pro Prozessor : 2 Einheit(en)

Kerne pro Prozessor : 8 Einheit(en)

Threads pro Kern : 2 Einheit(en)

Geschwindigkeit : 5.6GHz

Unterstützte Geschwindigkeit(en) : 3GHz - 4.5GHz - 5.6GHz

Interner (L1D) Datencache : 16x 32kB, 8-Weg, Exklusiv, 64bytes Zeilengröße, 2 Thread(s)

Interner (L1I) Anweisungscache : 16x 32kB, 8-Weg, Exklusiv, 64bytes Zeilengröße, 2 Thread(s)

L2D-Datencache/Einheitscache : 16x 1MB, 8-Weg, Voll integriert, 64bytes Zeilengröße, 2 Thread(s)

L3D-Datencache/Einheitscache : 2x 32MB, 16-Weg, Exklusiv, 64bytes Zeilengröße, 16 Thread(s)

Spannungswert : 0.32V

Min/Max/Turbo-Spannung : 0.32V - 0.32V - 0.32V

Speichercontroller

Modell : AMD PCI Standard-Host-CPU-Brücke

Geschwindigkeit : 933MHz

Minimale/Maximale/Turbo Geschwindigkeit : 467MHz - 933MHz

Leistungstipps

Tipp 229 : Es ist ein Update für den CPU Mikrocode verfügbar. Prüfen Sie, ob ein neues System BIOS mit dem aktualisierten Mikrocode verfügbar ist.

Hinweis 241 : Dynamische Übertaktung/Turbo aktiviert. Die Leistung kann bei Aktivierung variieren.

Tipp 3 : Drücken Sie die Eingabetaste oder doppelklicken Sie auf einen Tipp, um mehr Informationen zu erfahren.

ist also noch ein weiter Weg dahin...

ist also noch ein weiter Weg dahin...