Bl4d3Runn3r

Enthusiast

Thread Starter

- Mitglied seit

- 28.12.2006

- Beiträge

- 4.709

Hallo,

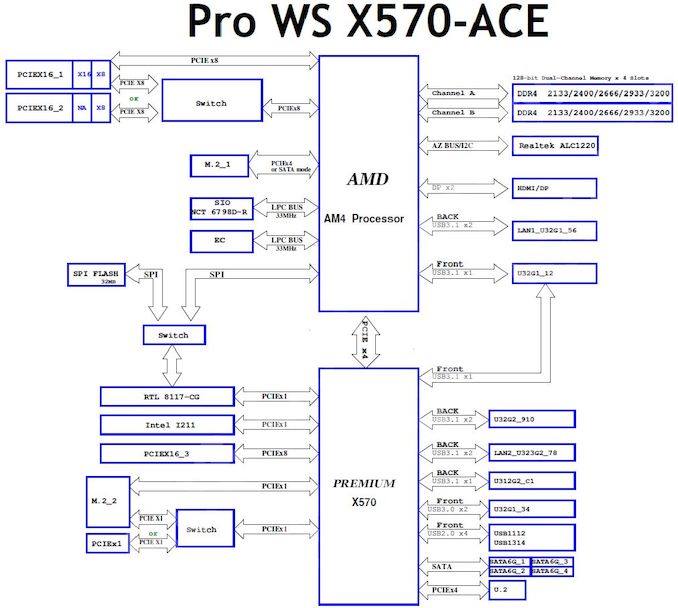

ich habe mich gefragt wie die PCIE Lane Verteilung bei Ryzen 3000 in Kombination mit X570 funktioniert. Ryzen 3000 hat ja 24 PCIE Lanes, die direkt ueber die CPU kommunizieren, richtig? X570 kommuniziert mit dem IO DIE der CPU mit PCIE Gen4 x4, hat aber selbst PCIE Gen4 x16!? Wie kann man denn dann die PCIE Gen4 x16 lanes nutzen, wenn X570 nur mit PCIE Gen4 x4 an der CPU haengt?

Ich verstehe das nicht so ganz.

ich habe mich gefragt wie die PCIE Lane Verteilung bei Ryzen 3000 in Kombination mit X570 funktioniert. Ryzen 3000 hat ja 24 PCIE Lanes, die direkt ueber die CPU kommunizieren, richtig? X570 kommuniziert mit dem IO DIE der CPU mit PCIE Gen4 x4, hat aber selbst PCIE Gen4 x16!? Wie kann man denn dann die PCIE Gen4 x16 lanes nutzen, wenn X570 nur mit PCIE Gen4 x4 an der CPU haengt?

Ich verstehe das nicht so ganz.