Werbung

Zur Computex hat Intel bisher nur Ankündigungen gemacht, die entweder eher in den Business-Bereich fallen (9th Gen vPro und Xeon E) oder deren Produkte erst später im Jahr folgen werden (neue X-Series-Prozessoren im Herbst und Core i9-9900KS im vierten Quartal). Der eigentliche Star der Show von Intel sind die Ice-Lake-U-Prozessoren. Mit diesen will Intel den Mythos der gescheiterten Fertigung in 10 nm endlich brechen. Wir fassen die technischen Details dazu einmal zusammen.

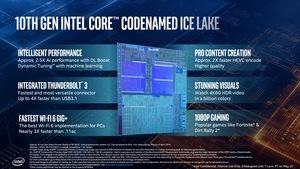

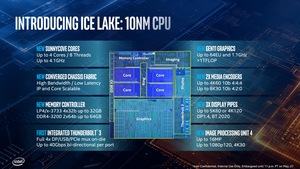

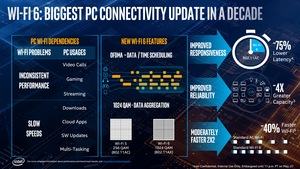

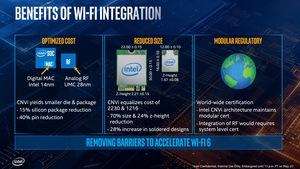

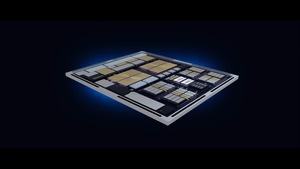

Die Ice-Lake-Prozessoren werden nicht nur in 10 nm gefertigt, sondern verwenden auch die neuen Sunny-Cove-Kerne sowie die ausgebaute Gen11-Grafikeinheit. Neben der neuen CPU-Architektur hat Intel Thunderbolt 3 und WiFi 6 in den dazugehörigen Chipsatz integriert.

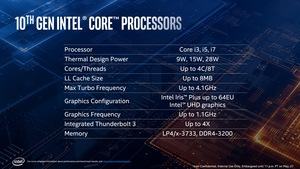

Auf technischer Ebene bieten die Prozessoren bis zu vier Kerne und können acht Threads gleichzeitig verarbeiten. Außerdem gibt es Varianten mit weniger Kernen und entsprechend sortiert Intel diese in die Leistungsklassen von 9, 15 und 28 W, bzw. in der i3-, i5- und i9-Serie an. Änderungen gibt es in der Cache-Struktur und der Takt ist mit bis zu 4,1 GHz relativ niedrig angesetzt. Schneller LPDDR4-Speicher soll der Plattform zu mehr Geschwindigkeit verhelfen. Auf die einzelnen Details gehen wir aber noch genauer ein.

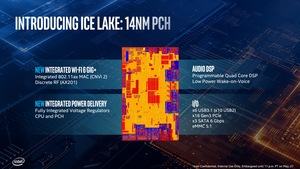

Doch auch wenn der eigentliche Prozessor der Ice-Lake-Plattform in 10 nm gefertigt wird, gilt dies nicht für den dazugehörigen Chipsatz (PCH). Dieser wird weiterhin in 14 nm gefertigt und beinhaltet das WiFi 6, eine Menge I/O und einen Audio-DSP.

Hinsichtlich der Fertigung noch wichtig ist die Tatsache, dass Intel sowohl für den Ice-Lake-CPU-Die als auch für den PCH auf eine integrierte Spannungsversorgung setzt. Diese Fully Integrated Voltage Regulators haben wir schon in anderen Intel-CPUs gesehen, sie sollen den Ice-Lake-U-Prozessoren zu einer besonders hohen Effizienz verhelfen.

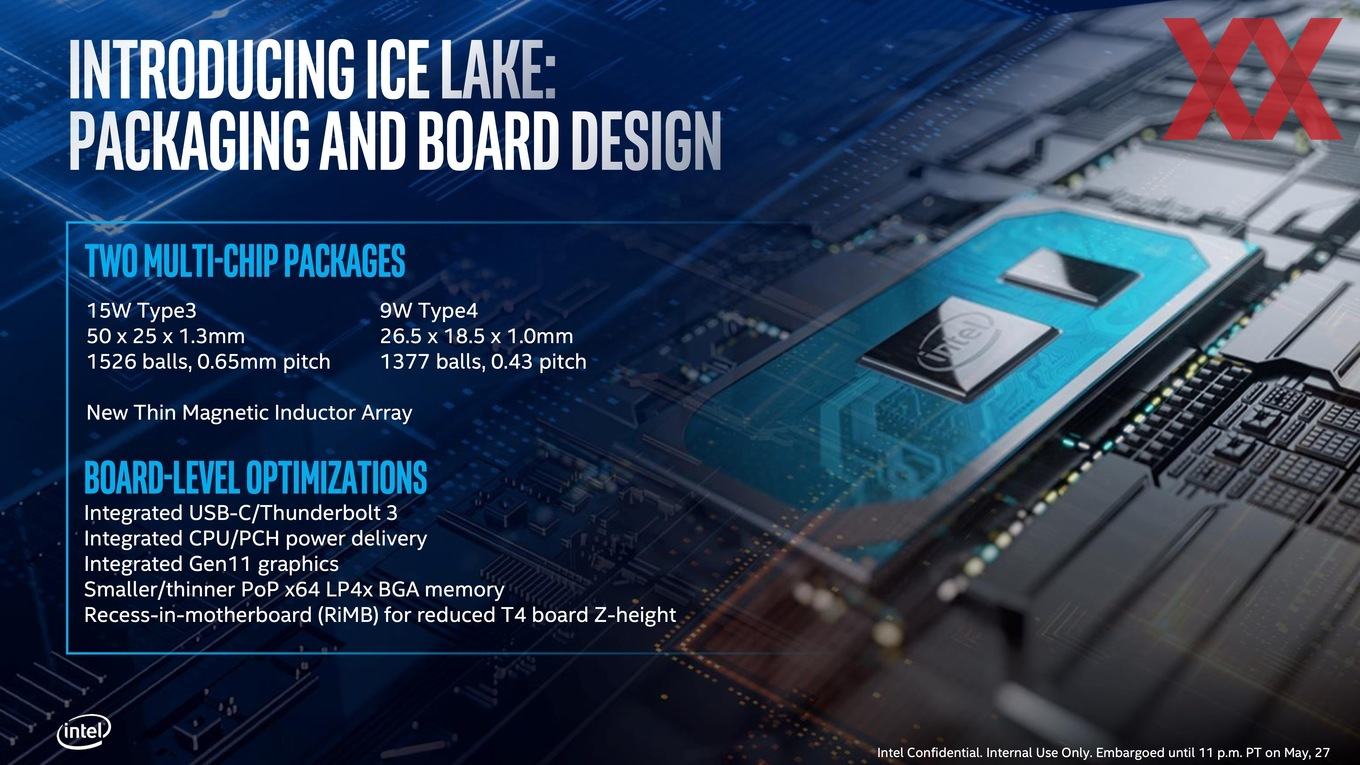

Es gibt mehrere Arten an Packages für Ice Lake-U. Eines ist der Type3 für die 15-W-Modelle. Dieses misst 50 x 25 x 1,3 mm und besitzt 1.526 BGA-Kontakte auf der Unterseite. Der Pitch-Abstand beträgt hier nur 0,65 mm. Das zweite Package hört auf den Namen Type4 und ist für die Modelle mit 9 W und weniger vorgesehen. Das Package misst hier 26,5 x 18,5 x 1 mm, kommt auf 1.377 BGA-Pins und einen Abstand von 0,43 mm. Das kleinere und vor allem dünnere Package soll zusammen mit dem PoP-LP4-Speicher deutlich flacher als zuvor sein und damit dünnere Notebooks ermöglichen.

Sunny-Cove-Architektur

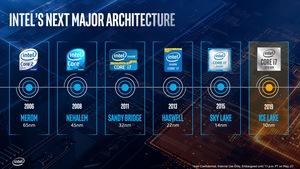

Die Sunny-Cove-Architektur bedeutet für Intel den ersten Wechsel in den grundlegenden Strukturen einer CPU-Architektur seit Skylake aus dem Jahre 2015. Vier Jahre hat Intel nun also kleinere Verbesserungen in Skylake einfließen lassen und bei aller Kritik daran hat Intel es dennoch geschafft, die Leistung im Vergleich zur ersten Generation der Prozessoren auf Basis der Skylake-Architektur bis zu den aktuellen Coffee-Lake-Refresh-Prozessoren deutlich zu steigern. Dies hängt außerdem mit den Verbesserungen der Fertigungstechnologien zusammen, denn auch wenn es Skylake auf 10 nm nur im homöopathischen Dosen in Form von Canon Lake gegeben hat, so sind die Optimierungen durch 14nm+, 14nm++ und 14nm+++ signifikant.

Doch Sunny Cove bringt nun den Wechsel auf eine völlig neue Architektur. Diese besitzt ein breiteres Front-End und ein tieferes Back-End.

Intel führt mit Sunny Cove eine 5-Wide-Out-of-Order-Architektur-Pipeline ein. Hier gibt es nun vier Unified Reservation Station (RS), was es Intel ermöglicht, die Instruktionen paralleler einfließen zu lassen, als bei Skylake. Womöglich auch um den Spectre-Mitigierungen entgegen zu wirken, hat Intel der AGU (Address Generation Unit) vier feste Ports zugewiesen. Jeweils zwei AGUs wird eine Load/Store-Unit zugewiesen. Für VEC- und INT-Berechnungen gibt es nun weitere Recheneinheiten in den jeweiligen Ports. All diese Maßnahmen sollen zur Beschleunigung der Architektur beitragen.

Weiterhin wird Sunny Cove neue ISA-Befehlssätze unterstützen. Dazu gehören Vector-AES und SHA-NI, aber auch AVX512. Bei den beiden erstgenannten handelt es sich um Algorithmen zur Hardwarebeschleunigung von Ver- und Entschlüsselungen. Generell soll der Fokus auf der Beschleunigung von Krypthografie-Algorithmen liegen, was wiederum die von Intel angesprochenen Optimierungen bei den speziellen Anwendungen betrifft.

Aufgrund der Erweiterung des Linear Adress Space auf 57 Bit, bzw. des Physical Adress Space auf 52 Bit wird ein Prozessor auf Basis der Sunny-Cove-Architektur bis zu 4 TB an Arbeitsspeicher pro Sockel ansprechen können.

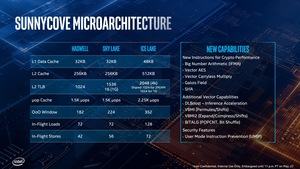

Änderungen gibt es auch in der Cache-Hierarchie. Der L1-Data-Cache wird um 50 % von 32 auf 48 kB vergrößert. Der L2-Cache gar auf 512 kB pro Kern verdoppelt. Der Translation Lookaside Buffer (TLB) wächst ebenfalls an, bietet zudem die Möglichkeit, größere Adresstabellen anzulegen. Auch der µOP-Cache wächst an.

Außerdem hat Intel die Branche Prediction hinsichtlich der Genauigkeit verbessert – interessanterweise ist genau hier (mindestens) eine der Lücken in der Skylake-Architektur vorhanden gewesen, die zu den Side-Channel-Attacken geführt hat.

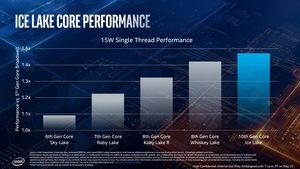

Dies alles soll dazu führen, dass Intel einen großen Sprung hinsichtlich der IPC-Leistung gemacht hat. Im Schnitt sollen es 18 % sein. Damit können sowohl AMD als auch Intel einen relativ großen Sprung machen – AMD kündigte für die Ryzen-Prozessoren der dritten Generation einen Anstieg der IPC-Leistung von 15 % an.

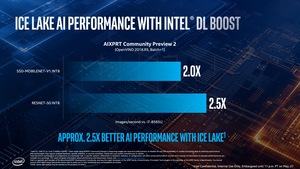

Die Sunny-Cove-Architektur bietet aber auch die Unterstützung einiger spezieller Befehlseinheiten, wie wir sie schon von der Cascade-Lake-Architektur kennen. Die Ice-Lake-Prozessoren sind die ersten Endkunden-CPUs von Intel, die AVX512 in allen Ausführungen und Ausbaustufen unterstützen. Im Vergleich zu Skylake will Intel die Leistung durch DL-Boost in AI-Anwendungen um den Faktor 2 bis 2,5 verbessert haben. Dies wird auch für die Ice-Lake-SP Servervarianten noch eine Rolle spielen. Diese werden aber erst im ersten Halbjahr 2020 erwartet.

Höherer Boost-Takt durch Dynamic Tuning 2.0

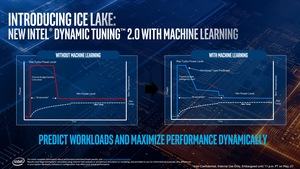

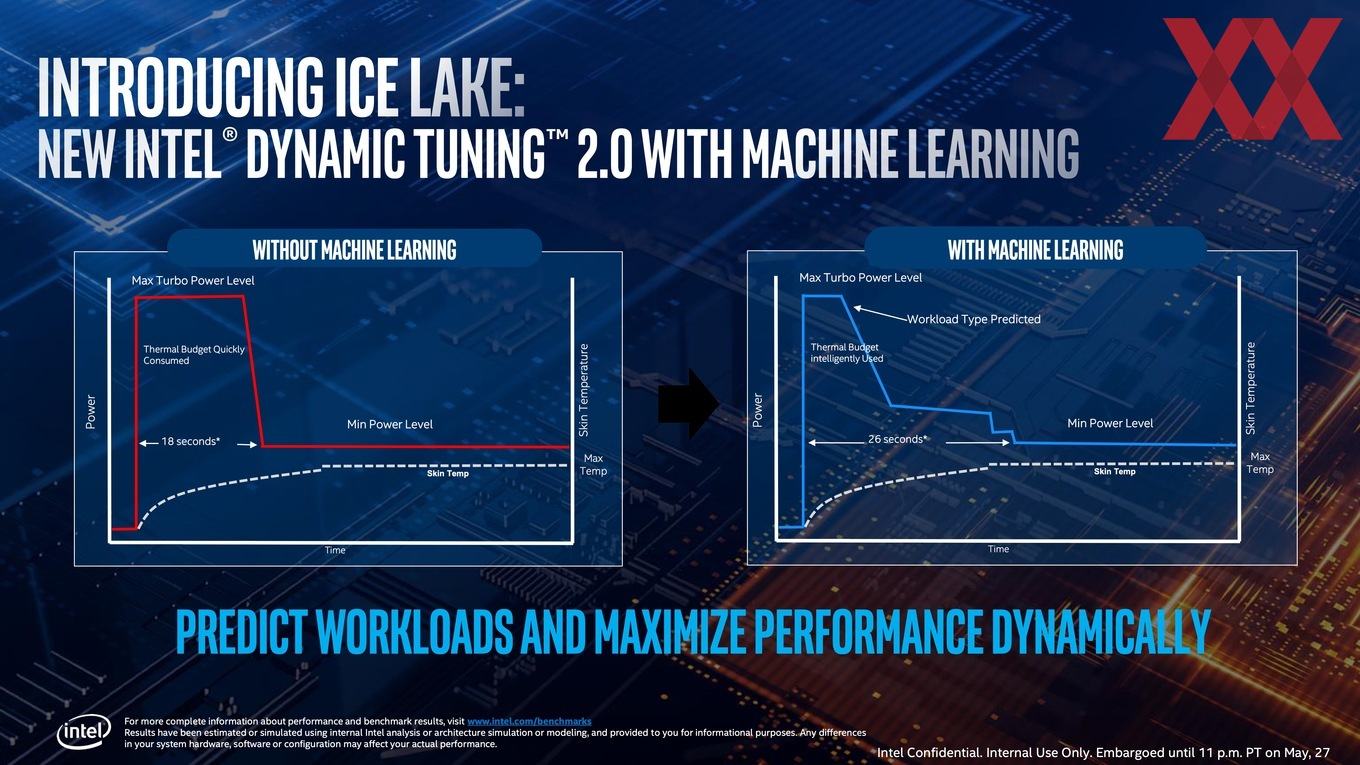

Dynamic Tuning 2.0 soll dabei helfen, dass die Ice-Lake-Prozessoren ihren Boost-Takt länger halten können und selbst wenn dieser gesenkt wird, soll er länger auf einem höheren Niveau verbleiben. Dazu will Intel die Last verschiedener Anwendungen über ein Machine-Learning-Modell analysiert haben und lässt die Prozessoren entsprechend darauf reagieren. Anstatt eines maximalen Turbo-Taktes von beispielsweise 18 s soll dieser dann über 26 s gehalten werden können.

Durch das Dynamic Tuning 2.0 sowie die Verbesserungen in der Architektur spricht Intel im Power-Budget von 15 W in einer Leistungssteigerung von fast 50 % gegenüber Broadwell.

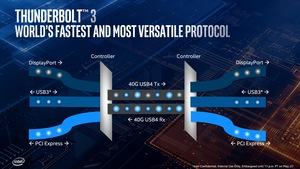

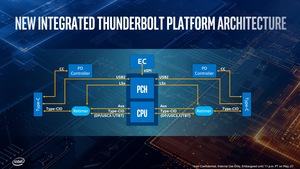

Thunderbolt 3 wird durch direkte Anbindung schneller

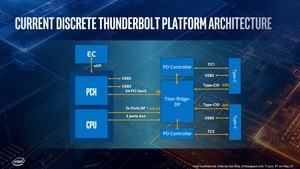

Die Ice-Lake-Prozessoren sind die ersten CPUs mit einem integrierten Thunderbolt-3-Controller. Bislang wurde Thunderbolt 3 über einen externen Controller-Chip realisiert. Der aktuelle Titan-Ridge-Controller wurde dabei über vier PCI-Express-3.0-Lanes angebunden. Wurden mehr als zwei Thunderbolt-Anschlüsse angebunden, konnten diese drei oder vier Anschlüsse nicht mehr gleichwertig in der zur Verfügung stehenden Bandbreite angesprochen werden.

Mit Ice Lake wird der Controller integriert und erreicht damit eine deutlich schnellere Anbindung. Somit sollen die theoretisch möglichen 40 GBit/s auch an möglichst vielen Anschlüssen zur Verfügung stehen. Auf der Computex zeigt Intel zahlreiche Demos, in denen ältere Thunderbolt-Lösungen mit der neuen verglichen wurden und zumindest in diesen Demos konnten Datenraten von mehreren Gigabyte pro Sekunde gezeigt werden. Dies hängt natürlich auch davon ab, wie schnell das angeschlossene Laufwerk ist.

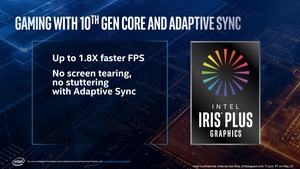

Iris Plus Graphics für 1080p-Gaming

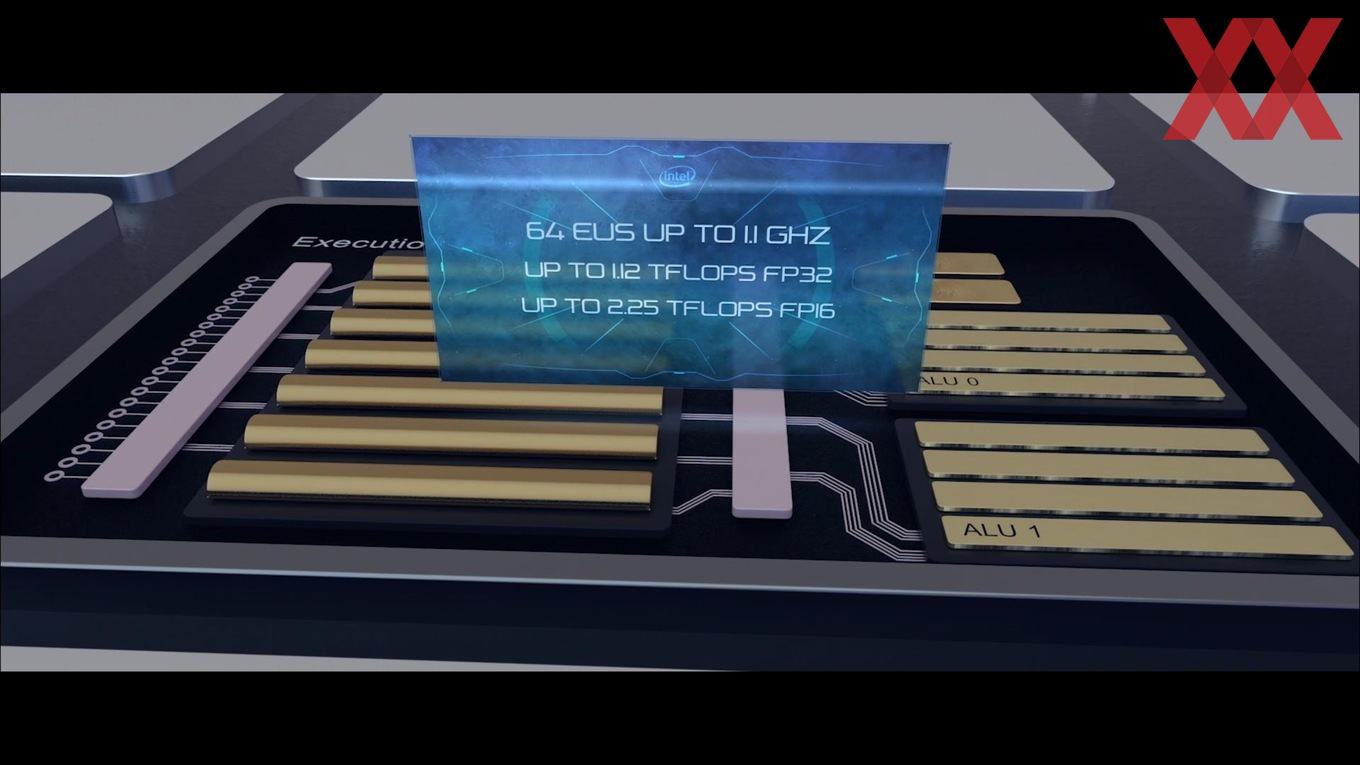

Die Gen11-Grafikeinheit der Ice-Lake-Prozessoren ist der Zwischenschritt zur ersten wirklich neuen GPU-Architektur, die als Xe im kommenden Jahr auf sich aufmerksam machen soll. Im Maximalausbau sieht die Architektur 64 Execution Units (EUs) vor. Neben den Änderungen in der Architektur bietet die Gen11-Grafikeinheit Funktionen wie das Coarse Pixel Shading (CPS) und Position Only Shading Tile Based Rendering (PTBR).

Die 64 EUs sollen mit einem maximalen Takt von 1,1 GHz arbeiten können. Dies sorgt für eine Rechenleistung von 1,12 TFLOPS bei FP32-Berechnungen und 2,25 TFLOPS bei FP16-Berechnungen.

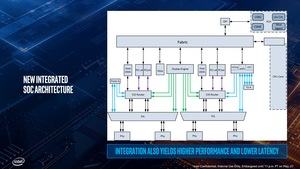

Die Gen11-Grafikeinheit wird per SoC Ring Interconnect an die restlichen Komponenten des Prozessors, bzw. des SoCs angebunden. Dabei ist es wichtig zu wissen, dass es mehrere Takt-Domains gibt, mit denen die einzelnen Komponenten arbeiten. Da wäre die des einzelnen CPU-Kerns, bzw. der Kerne (wenn mehrere vorhanden), eine Processor Graphics Clock Domain und eine Ring Interconnect Clock Domain.

Der SoC Ring Interconnect verbindet die Gen11-Grafikeinheit mit den CPU-Kernen, dem Last Level Cache (LLC) und dem System Agent (Speichercontroller, PCI-Express-Controller, Display-Controller, etc.).

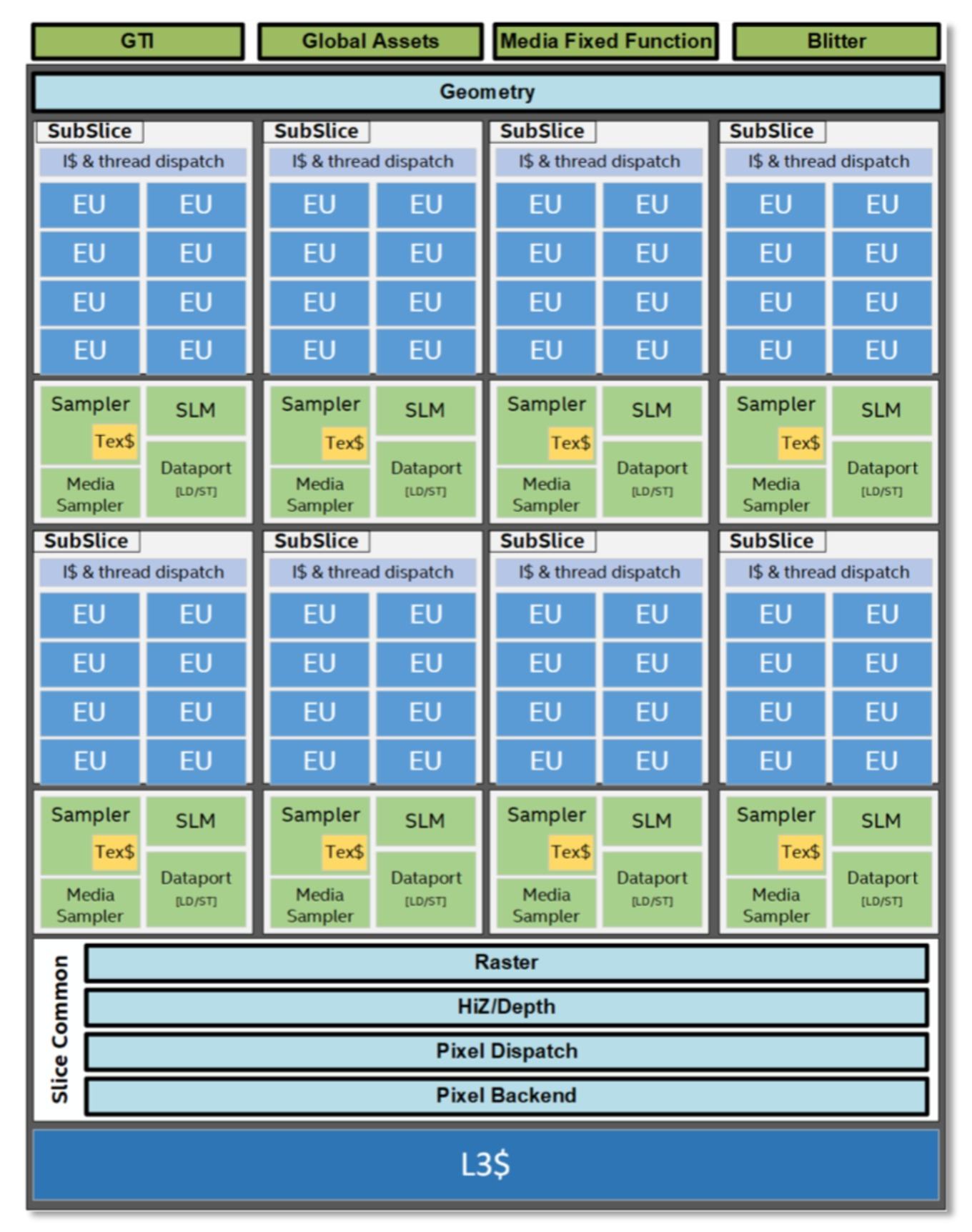

Die Gen11-Grafikeinheit besteht aus einem sogenannten Slice und dieses wiederum aus maximal acht Subslices. Die Sublices teilen sich den L3-Cache, das Pixel Backend, den Pixel Dispatcher sowie den Rasterizer und die Einheiten für den Z-Buffer und das Culling. Die meisten Prozessoren mit Gen11-Grafikeinheit werden laut Intel die Ausbaustufe mit acht Subslices und folglich 64 EUs verwenden. Denkbar sind jedoch auch kleinere Ausbaustufen der Gen11-Grafikeinheit.

Jedes Subslice beinhaltet eine Local Thread Dispatcher Unit und ihren eigenen Instruction Cache. Hinzu kommen eine 3D Texture Sampler Unit, eine Media Sampler Unit und eine Dataport Unit.

Kernbestandteil ist natürlich die einzelne Execution Unit. Diese ist im Grunde genommen eine Kombination aus Simultaneous Multi-Threading (SMT) und Fine-Grained Interleaved Multi-Threading (IMT). Der IMT-Anteil der Architektur sorgt dafür, dass die diversen Compute-Einheiten der EU ständig mit neuen Instruktionen gefüttert werden.

Jede EU besitzt zwei SIMD Floating-Point Units (ALUs). Obwohl sie ALUs genannt werden, können sie auch Integer-Berechnungen ausführen. Jede dieser ALUs kann bis zu vier 32 Bit Floating-Point-(oder Integer)-Operationen, oder bis zu acht 16-Bit-Floating-Point-Operationen ausführen. Effektiv kann jede EU 16 FP32-Berechnungen pro Takt (2 ALUs x SIMD-4 x 2 Ops (Add + Mul)) und 32 FP16-Berechnungen pro Tak (2 ALUs x SIMD-8 x 2 Ops (Add + Mul)) ausführen. Die EUs arbeiten Multi-Threaded und haben dazu ein 28 kB großes Register File (GRF) mit 32 Bytes pro Register.

| Gen9 | Gen11 | |

| Slices | 1 | 1 |

| Sublices | 3 | 8 |

| Execution Units | 24 (3x 8) | 64 (8x 8) |

| FLOPS pro Takt (FP32) | 384 | 1.024 |

| FLOPS pro Takt (FP64) | 768 | 2.048 |

| Register | 672 kB (3x 224 kB) | 1.792 kB (8x 224 kB) |

| Shared Local Memory | 192 kB (3x 64 kB) | 512 kB (8x 64 kB) |

| Pixel pro Takt | 8 | 16 |

| L3-Cache | 768 kB | 3.072 kB |

| GTI-Bandbreite | 64 / 32 Byte pro Takt | 64 / 64 Byte pro Takt |

| Last Level Cache | 2 bis 8 MB | TBD |

| DRAM-Unterstützung | 2x 64 LPDDR3/DDR4 | 4x 32 LPDDR4/DDR4 |

Im Vergleich zur Gen9-Grafikeinheit befindet sich der Shared Local Memory (SLM) in der Gen11-Grafikeinheit im Subslice. Die acht EUs eines Subslice können daher direkt auf den 64 kB großen SLM zugreifen und müssen nicht über den Dataport an den SLM, der zudem Bestandteil des L3-Caches ist, gehen. Die höhere Bandbreite und die geringeren Latenzen sollen der Gen11-Grafikeinheit in diesem Fall helfen.

Dem Dataport kommt eine besondere Bedeutung zu, da über diesen Zugriffe zum L3-Cache erfolgen. Intel hat den L3-Cache auf 3 MB vergrößert. Der Dataport kann 64 Bytes pro Cycle aus dem L3-Cache lesen oder in ihn schreiben. Um den Datentransfer möglichst effektiv zu gestalten, ist es möglich, zwei 32 Byte große Zugriffe in einen 64 Byte großen Cache zusammenzufassen. Zudem implementiert Intel neue Losless-Komprimierungsverfahren, die auch in der Kommunikation mit dem Systemspeicher eine Rolle spielen, denn auch wenn der L3-Cache auf 3 MB angewachsen ist, so müssen dennoch Daten aus dem Arbeitsspeicher des Prozessors gelesen und darin geschrieben werden.

Das gesamte Speichersystem der Gen11-Grafikeinheit ist auf niedrige Latenzen und hohe Bandbreiten hin optimiert worden. Unterstützt wird die Architektur durch die Unterstützung von LPDDR4.

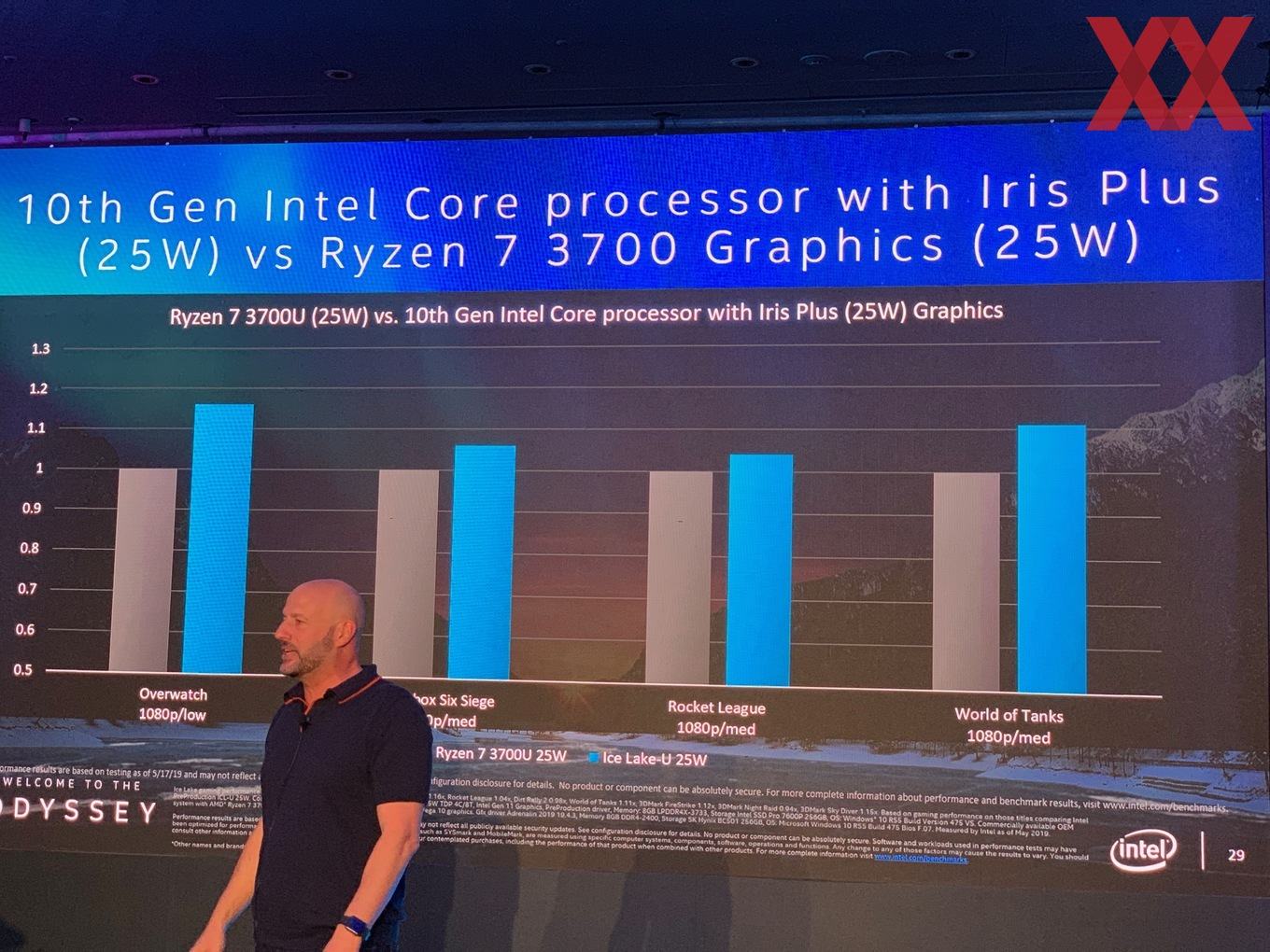

Durch die zahlreichen Verbesserungen in der Iris-Plus-Grafikeinheit verspricht sich Intel wieder auf Augenhöhe mit den APUs von AMD zu sein. 1080p-Gaming soll mit einem Ice-Lake-System gar kein Problem darstellen – zumindest je nach Spiel. Intel spricht hier beispielsweise von CS:GO, Rocket League, Dirt Rally 2.0 und Fortnite.

Als Iris Plus bezeichnet wird die Grafikeinheit bei allen Ice-Lake-Prozessoren mit 48 oder 64 EUs. Solche mit 32 EUs tragen den Zusatz UHD.

Die ersten Modelle

Bereits auf der Computex gibt es die ersten Modelle an Notebooks mit Ice Lake zu sehen. Intel startet vorerst mit sechs Varianten. Bekannt sind bisher nur die Daten zu den Ice-Lake-U-Modellen, während die Y-Varianten mit 9 W wohl etwas später folgen werden.

| Kerne/Threads | Basistakt | Boosttakt | Cache | TDP | |

| Core i7-1065G7 | 4 / 8 | 1,3 GHz | 3,9 GHz | 8 MB | 15 W |

| Core i5-1035G7 | 4 / 8 | 1,2 GHz | 3,7 GHz | 8 MB | 15 W |

| Core i5-1035G4 | 4 / 8 | 1,1 GHz | 3,7 GHz | 8 MB | 15 W |

| Core i5-1035G1 | 4 / 8 | 1,0 GHz | 3,7 GHz | 8 MB | 15 W |

| Core i5-1034G1 | 4 / 8 | 0,8 GHz | 3,6 GHz | 8 MB | 15 W |

| Core i3-1005G1 | 2 / 4 | 1,2 GHz | 3,4 GHz | 4 MB | 15 W |

Auch wenn Intel von einem maximalen Boost-Takt von 4,1 GHz spricht, sehen wir diesen bei den ersten Modellen noch nicht. Dies wird womöglich den Modellen mit mehr TDP-Spielraum vorbehalten bleiben. Bisher sind auch noch nicht alle diese Modelle seitens Intel bestätigt worden. Allerdings stehen auf der Messe zahlreiche Notebooks unterschiedlichster Konfiguration aus.