Werbung

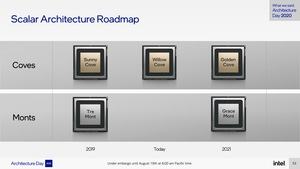

Als Performance-Hybrid-Design setzt Intel bei Alder Lake auf zwei CPU-Architekturen, die in Koexistenz ihren Dienst verrichten sollen. Die großen x86-Kerne hören auf den Namen Golden Cove. Golden Cove ist der Nachfolger von Willow Cove, wie sie bei den Tiger-Lake-Prozessoren in Enhanced 10 nm und bei Cypress Cove für die direkten Desktop-Vorgänger Rocket Lake eingesetzt wurden. Die kleineren Efficiency-Kerne hören auf den Namen Gracemont und sind direkte Nachfolger der Tremont-Kerne, die allerdings nur bei Atom-Prozessoren und bei Lakefield zum Einsatz kamen.

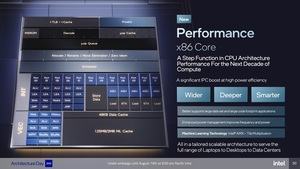

Performance-Kerne: Golden Cove

Golden Cove wird als Architektur nicht nur für Alder Lake und auf dem Desktop sowie für Notebooks seinen Einsatz finden, sondern auch für die Xeon-Prozessoren auf Basis von Sapphire Rapids, die ebenfalls noch 2021 vorgestellt werden sollen.

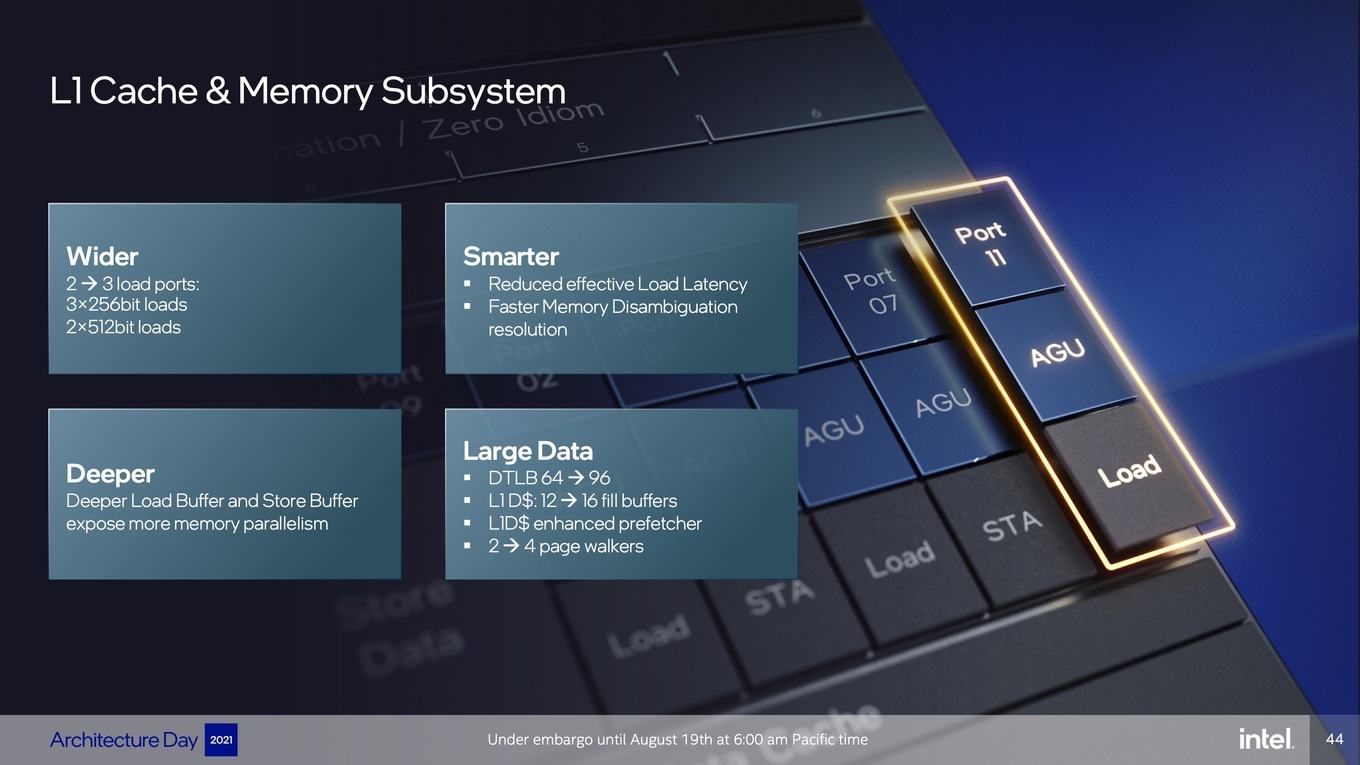

Intel stellt das Front End bei Golden Cove extrem breit auf. Es gibt wieder einen Micro-op-Cache mit deutlich mehr Einträgen, der zudem auch noch mehr Einträge abarbeiten kann. Eine 6-Wide-Allocation, eine clevere Branche Prediction und größere TLBs sorgen dafür, dass mehr Instruktionen aufgenommen und weitergegeben werden können.

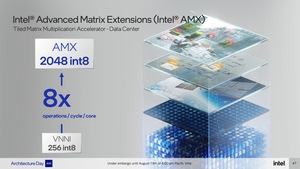

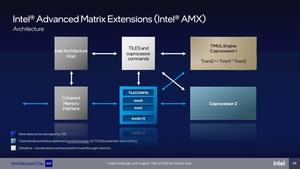

Über 12 Execution Ports wird das Front End gefüttert. Im Vergleich zu Willow Cove gibt es einen zusätzlichen Integer Port, der anders als die restlichen nicht mit Spezialaufgaben betraut ist, sondern exklusiv die Standard-Befehlssätze entgegennehmen soll. Die dazugehörigen Vektor-Einheiten beherrschen grundsätzlich den aktuellen AVX-512-Umfang und können neben FP16-Berechnungen auch per AMX die entsprechenden Matrixberechnungen beschleunigen. AMX ist aber von einer Unterstützung der Software abhängig, was dann aber auch zu einer Beschleunigung in der Berechnung um den Faktor acht sorgen soll – unter idealen Bedingungen.

AVX-512 wird für die Consumer-orientierten Alder-Lake-Prozessoren aber nicht zum Einsatz kommen. Die Performance-Kerne unterstützen es und verfügen über die entsprechenden Einheiten sowie die Umsetzung in Hardware, aufgrund der notwendigen Funktions-Parität zwischen den unterschiedlichen Kernen, muss hier ein kleinster gemeinsamer Nenner zum Einsatz kommen – da die Efficiency-Kerne ein AVX-512 nicht unterstützen, bliebt es auch auf den großen Kernen inaktiv. Da AVX-512 aber auch für Beschleunigungen der Vector Neural Network Instructions (AVX512 VNNI) verantwortlich war, hat Intel dies in AVX2 ausgelagert. AVX2 ist zugleich auch der kleinste gemeinsame Nenner zwischen den P- und E-Kernen. Die Xeon-Prozessoren auf Basis von Sapphire Rapids, bei denen ebenfalls Golden-Cove-Kerne zum Einsatz kommen, werden AVX-512 unterstützen.

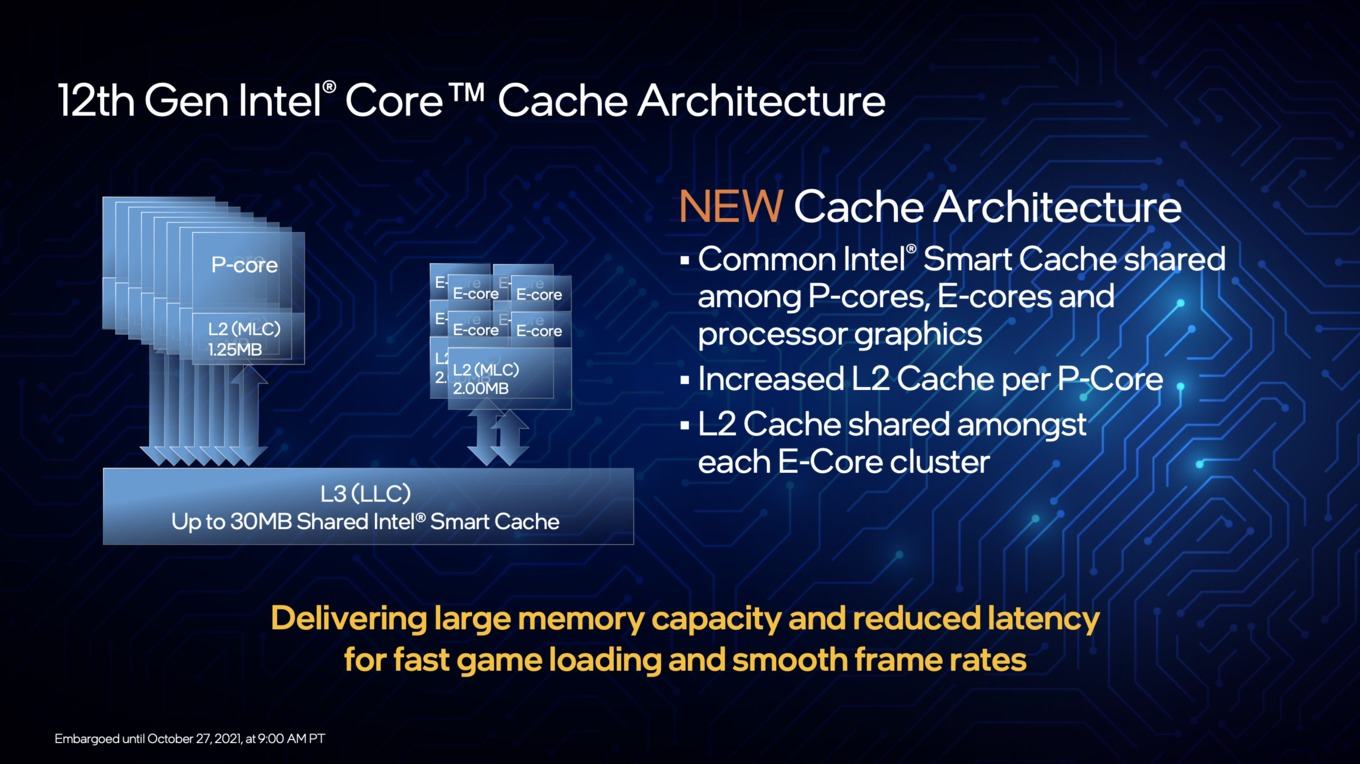

Eine weitere Unterscheidung zwischen dem Endkunden- und Servermarkt macht Intel bei den Cache-Kapazitäten. Bei Alder Lake bekommt jeder P-Kern 1,25 MB an L2-Cache, bei Sapphire Rapids werden es 2 MB sein. Dieser L2-Cache steht den Kernen exklusiv zur Verfügung. Bei acht Kernen haben wir also 8x 1,25 MB = 10 MB an L2-Cache zur Verfügung, bei sechs Kernen sind es dementsprechend 7,5 MB.

Die Performance-Kerne teilen sich einen gemeinsamen L3-Cache mit den Efficiency-Kernen. Dieser kann bis zu 30 MB groß sein. Dies ist aber nur bei der 8+8-Konfiguration der Fall. Der Core i7-12700K (8+4-Konfiguration) verfügt über 25 MB an L3-Cache. Der Core i5-12600K kommt auf 20 MB.

| Skylake | Sunny Cove | Cypress Cove | Willow Cove | Golden Cove | |

| Fertigung | 14 nm | 10 nm | 14 nm | 10 nm | 10 nm |

| L1-Data Cache | 32 KB pro Kern | 48 KB pro Kern | 48 KB pro Kern | 48 KB pro Kern | 48 KB pro Kern |

| L1-Instruction Cache | 32 KB pro Kern | 32 KB pro Kern | 32 KB pro Kern | 32 KB pro Kern | 32 KB pro Kern |

| L2-Cache | 256 kB pro Kern | 512 kB pro Kern | 512 kB pro Kern | 1,25 MB pro Kern | 1,25 MB MB pro Kern |

| L2-Cache TLB | 1.536 | 2.048 | 2.048 | 2.048 | 2.048 |

| L3-Cache | 2 MB pro Kern | 2 MB pro Kern | 2 MB pro Kern | 3 MB pro Kern | 3 MB pro Kern |

| µOp-Cache | 1.500K µOps | 2.250K µOps | 2.250K µOps | - | 4.000K µOps |

| OoO Window | 224 | 352 | 352 | - | 512 |

| In-Flight Loads | 72 | 128 | 128 | 128 | 144 |

| In-Flight Stores | 56 | 72 | 72 | 72 | 72 |

| Speichercontroller | DDR4-2933 | DDR4-3200 LPDDR4-3744 | DDR4-3200 | DDR4-3200 LPDDR4-3744 LPDDR5-5400 | DDR4-3200 DDR5-4800 |

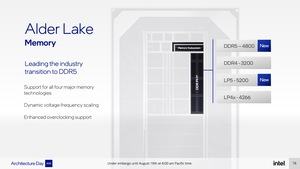

Obige Tabelle vergleicht die Endkunden-Versionen der letzten Core-Architekturen von Intel. Die Angaben der Cache-Kapazitäten entsprechen daher denen der Core-Prozessoren und nicht der Xeon-Modelle. Für Sunny Cove und Willow Cove kennen wir zudem die Unterstützung von LPDDR-Speicher. Da Alder Lake auch im Notebook zum Einsatz kommen wird, wird auch hier LPDDR4/5 unterstützt.

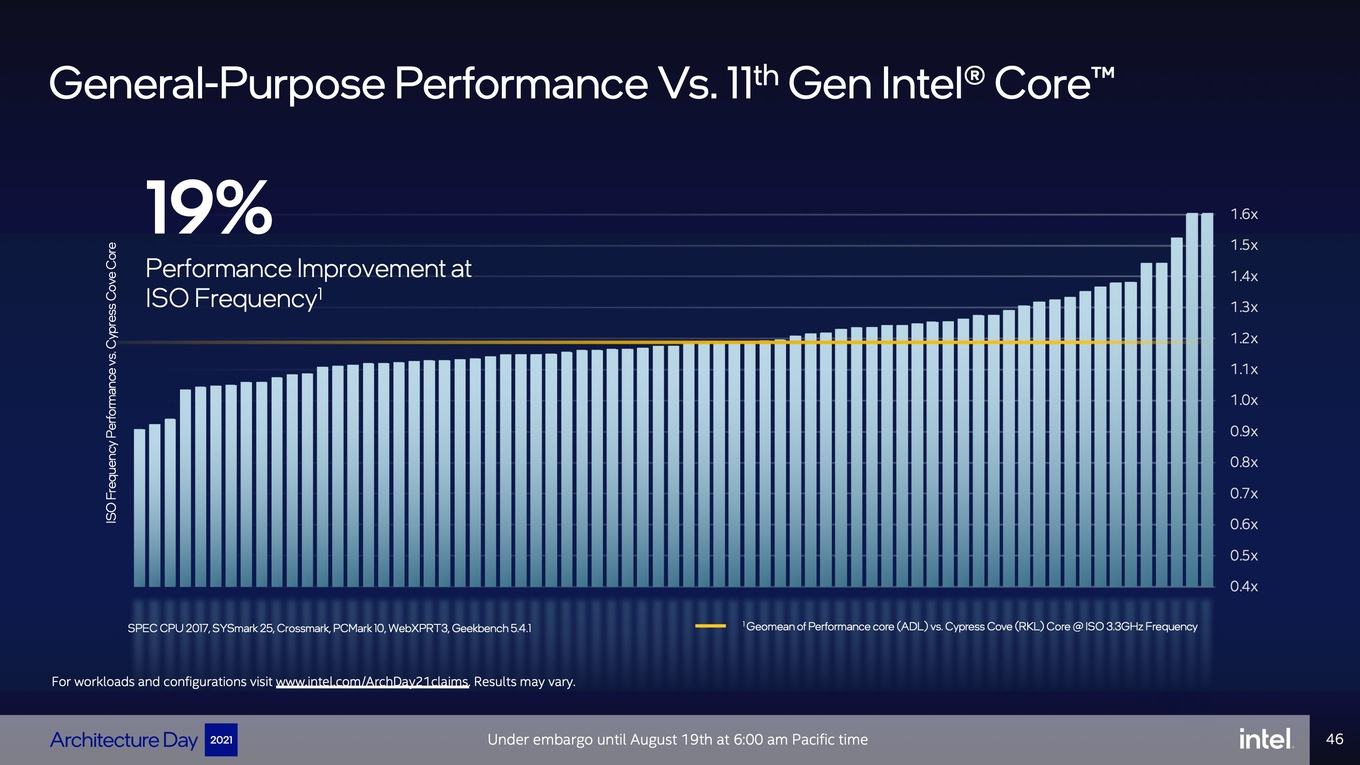

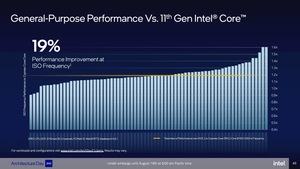

Intel spricht von einem IPC-Plus von 19 % für Golden Cove - taktbereinigt bei 3,3 GHz und im Vergleich zu Cypress Cove. Intel macht hier also einen deutlichen Sprung und vor allem gibt es auch Anwendungsbereiche, die noch einmal deutlich beschleunigt werden konnten, aber auch solche, bei denen der Unterschied geringer ist. Die 19 % entsprechen einem Durchschnittswert.

Aber es gibt nicht nur Verbesserungen in der Architektur, sondern auch der Fertigung und im Controlling der Kerne. So spricht Intel von einem neuen Powermanagement-Microcontroller, der die Spannung in Mikrosekunden anpassen kann und nicht mehr nur im Bereich von Millisekunden. Auch bei den Ryzen-Prozessoren spricht AMD gerne über solche Optimierungen, die dafür sorgen, dass die Kerne ihren Takt schneller anpassen können, was sie einerseits effizienter macht, aber auch die Latenzen verkürzt.

Efficiency-Kerne: Gracemont

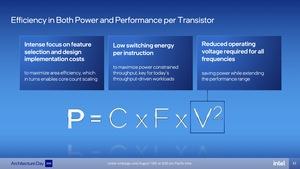

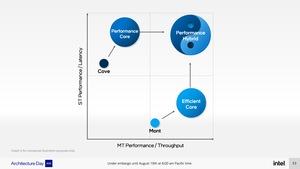

Zweite Komponente des Hybrid-Designs sind die Efficiency-Kerne auf Basis von Gracemont. Diese sollen hocheffizient ausgelegt sein und kommen als Produktfamilie sonst nur im Atom-Umfeld zum Einsatz. Gracemont ist die Nachfolgearchitektur von Tremont. Gracemont-Kerne sollen im x86-Umfeld die effizientesten sein, die jemals entwickelt wurden. Hinsichtlich der IPC-Leistung sollen sie auf Niveau der Skylake-Architektur liegen.

Viele kleine Kerne sollen Intel dabei helfen, hinsichtlich der Multi-Threaded-Leistung nicht den Anschluss zu verlieren. Vier Efficiency-Kerne sind so groß wie ein Performance-Kern und ein Cluster aus vier der sparsamen Kerne hat fast die gleiche Multi-Threaded-Leistung bei nur 1/4 der Leistungsaufnahme – so Intel.

Auch für Gracemont gibt es aus Sicht der Architektur vor allem Verbesserungen im Front End und der Branche Prediction. Die Effizienz wird in aktuellen Designs vor allem durch die Sprungvorhersage (Branche Prediction) bestimmt. Je besser diese ist, desto effizienter kann der Kern arbeiten, da fehlerhafte Vorhersagen Zeit und Energie kosten. Das dazugehörige Register fast mehr als 5.000 Einträge und über eine Historie sollen bereits verwendete Vorhersagen wiederverwendet werden können.

Sprachen wir bei Golden Cove schon über zwölf Execution Ports, sind es bei Gracemont sogar 17. Beim Vorgänger Tremont waren es zehn. Egal ob Integer, Floating Point oder Vektor – die Anzahl der Ausführungseinheiten pro Klasse verdoppelt sich fast. Hinsichtlich des ISA-Umfangs bleibt es für Gracemont bei AVX2, aber dies haben wir schon im Rahmen der Golden-Cove-Kerne besprochen.

Damit die kleinen Kerne auch schnell mit dem Speicher kommunizieren können, spendiert Intel diesen eine verdoppelte Load- und Storage-Pipeline, was sie auf Niveau von Golden Cove bringt. Beim Cache gibt es ebenfalls ein deutliches Update. Die Tremont-Vorgänger verfügten über 32 kB an L1-Data- und Instruction-Cache. Bei Gracemont sind es nun 64 kB an Instruction-Cache, aber weiterhin 32 kB an Data-Cache. Der L2-Cache wird zwischen vier Gracemont-Kernen aufgeteilt und beläuft sich auf 4 MB.

Alle Maßnahmen sollen wie gesagt dazu führen, die Gracemont-Kerne schnell und effizient zu machen. Laut Intel kommt ein Efficiency-Kern auf die gleiche Leistung wie ein Skylake-Kern, verbraucht dabei aber 40 % weniger Energie. Ein Cluster aus vier Gracemont-Kernen liefert mehr als 80 % an Leistung im Vergleich zu zwei Skylake-Kernen. Umgekehrt betrachtet müssen zwei Skylake-Kerne fünfmal mehr Energie aufwenden, um die gleiche Leistung wie vier Gracemont-Kerne zu kommen. Die Vorteile bezieht Intel hier natürlich auch aus der Fertigung in Intel 7 (10 nm).

Der LLC (Last Level Cache) alias L3-Cache ist bei Alder Lake bis z 30 MB groß. Sind aber nicht alle acht Performance- oder Efficiency-Kerne aktiv, bekommt man auch nicht den vollen L3-Cache. Der L2-Cache steht den Kernen exklusive zur Verfügung. Bei den Efficiency-Kernen teilen sich immer vier Kerne einen 2 MB fassenden L2-Cache.