Werbung

Zum Start der Raptor-Lake-Prozessoren hatten wir die Gelegenheit, sozusagen die Geburtsstätte dieser CPU-Generation zu besuchen. Was wenige wissen: Das Unternehmen Intel betreibt eine große Forschungs- und Entwicklungsabteilung in Israel sowie fertigt hier die aktuellen CPU-Generationen. Insgesamt hat Intel 12.000 Angestellte in Israel, die sich maßgeblich auf das Intel Development Center (IDC) und die Fab 28 in Kiryat Gat aufteilen. Besucht haben wir beide Niederlassungen, die maßgeblich an dem beteiligt sind, was Intel aktuell an Produkten an seine Kunden liefert.

Auf Einladung Intels konnten wir uns also das IDC, die Fab 28 und die Baustelle der Fab 38 anschauen. Der Besuch fand bereits im September statt, aber erst jetzt kommen wir dazu, einen kleinen Bericht zu verfassen. Dies liegt auch an den heiklen Details, die im Rahmen eines solches Besuches öffentlich werden könnten. Einfach so Fotos zu machen, ist in solchen Einrichtungen nicht möglich. Sensible Inhalte sollen verborgen bleiben und dennoch findet das geschulte Auge das ein oder andere Detail – auch dazu im nun folgenden Text etwas mehr.

Bereits im Ramen unseres Interviews mit Adi Yoaz (Chief Architect of the Performance Core & Intel Fellow) wurde deutlich, dass ohne seine Abteilungen in Israel in den vergangenen Jahren wenig bei Intel voran gegangen wäre. Nahezu sämtliche Core-Designs der vergangenen Jahre stammen aus Israel. Das Zusammenspiel - oder wie es auch gerne beschrieben wird, ein "Bälle zuwerfen" - mit einem zweiten Team in Portland, Oregon, funktionierte nicht mehr richtig und so entstanden viele, vor allem die aktuellsten CPU-Architekturen, in Israel. Den Anfang machte der Intel 8088, darauf folgte die MMX-Erweiterung für die Pentium-II-Prozessoren und zuletzt eben Banias, Marom, Yonah, Centrino, Sandy Bridge, Ivy Bridge, Coffee Lake, Ice Lake, Alder Lake und schlussendlich Raptor Lake.

Aufgrund dieser Entwicklung dürfte zumindest auch noch Meteor Lake aus den Federn der Ingenieure aus Israel stammen, denn in Portland soll zunächst ein neues Team aufgebaut werden, damit das Ping-Pong zwischen Oregon und Israel wieder stattfinden kann. Die Efficiency-Kerne werden übrigens im US-Bundesstaat Texas, genauer gesagt in Austin, entwickelt.

Im IDC wird das Wirklichkeit, was sich die Architekturen der Kern-Architekturen, SoC- und Plattform-Designer ausgedacht haben. Diese Design-Phase dauert bis zu 30 Monate vor Marktstart. 24 Monate vorher sollte das Design abgeschlossen sein und die Pre-Silicon Validation kann beginnen. Dabei wird das Design simuliert, ohne dass daraus bereits ein Chip geworden ist. Im IDC findet allerdings nicht die erste Fertigung des Designs in Form eines Chips statt. Dies geschieht in Arizona und dauert nach Einsenden des ersten Designs in etwa 3-4 Monate.

Erst danach stehen die ersten fertig belichtete Wafer zur Verfügung, aus denen dann Chips werden können. Von dort geht es zum Packaging und darauf folgen die sogenannten Bring-Ups im IDC. Hier werden die Prozessoren in einer A0-Revision auf spezielle Boards geschnallt und das erste Mal gebootet. Dabei geht es zunächst einmal darum, ob alle Bereiche des Prozessors korrekt angesprochen werden können, die Spannungen stimmen und die Funktionsblöcke überhaupt so arbeiten, wie dies die Designer vorgesehen haben.

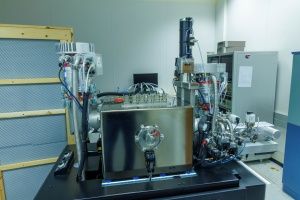

Fehler im Pre-Silicon-Design können natürlich noch behoben werden. Sobald die ersten Chips aus der Fertigung kommen, können diese Fehler aber nur in einer nächsten Revision behoben werden. Um eventuelle Fehler aber beheben zu können muss man wissen, wo das Problem genau liegt. In den Debug & Developement Labs können Fehler im Design auf Hardwareeben behoben werden. Das heißt die entsprechenden Bereiche im Chip werden per Ionenstrahl freigelegt und es können andere Routen aufgebracht werden. Beide Prozessschritte setzen natürlich größte Präzision voraus, denn schließlich reden wir von Reparaturarbeiten im Mikro- und Nanometer-Bereich. Aber so ist es möglich gewisse Fehler im Design zu beheben, dieses weiter zu testen, eventuell vorhandene Fehler zu sammeln und diese allesamt in einer neuen Revision zu beheben. Bei 14 Metalllayern und mehreren Milliarden Transistoren kann sowohl die Fehlersuche als auch das Beheben dieser Fehler natürlich extrem komplex sein.

Eigene Teams beschäftigen sich damit zunächst einmal genauer einzugrenzen, wo der Fehler ist, bevor dann ein anderes Team schaut, ob man diesen überhaupt, ohne eine weitere Revision abzuwarten beheben kann.

Was wir soeben beschrieben haben, ist aber nur die erste Ebene des Debugging. Bring-Up und die erste Phase der Post-Silicon Validation sind in Anbetracht der Vielfalt und Komplexität in der sich der Prozessor später bewähren muss, extrem schmal gehalten. Sobald die Prozessoren sozusagen aus dem Gröbsten heraus sind, geht es einen Schritt weiter. Hier geht es dann darum, die komplette Plattform zu testen. So unterstützten die Raptor-Lake-Prozessoren DDR4 und DDR5 sowie PCI-Express 5.0. Dies alles muss natürlich getestet werden – mit unzähligen Möglichkeiten an unterschiedlicher RAM-Bestückung und einer nicht weniger komplexen Vielfalt an PCIe-Geräten und vielem mehr. USB, die integrierte GPU, die dazugehörigen Videoausgänge, Temperaturabhängigkeiten, das Verhalten mit unterschiedlichen Ausbaustufen an Strom- und Spannungsversorgungen – man kann sich sicherlich vorstellen, wie komplex solche Tests werden können. Dies ist auch der Grund dafür, warum nicht ein paar Dutzend, sondern, mehrere hundert Teststationen im IDC stehen, auf denen die meisten dieser Kombinationen getestet und geprüft werden sollen.

Intel prüft hier aber nicht nur die Prozessoren für die eigenen Tests, sondern arbeitet im Vorfeld einer neuen Generation auch mit seinen Partnern zusammen. Bis zu 100.000 Prozessoren werden dazu an diese verschickt und ebenfalls zuvor von Intel auf die wichtigsten Merkmale geprüft. Diese Schritte finden natürlich erst statt, wenn man in der Entwicklung schon etwas weiter vorangeschritten ist. Ein A0-Silicon bekommt auch keiner der Partner zu Gesicht.

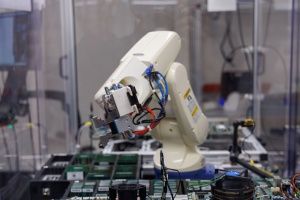

Ein weiterer Punkt ist natürlich, dass man im IDC nicht nur an einem bestimmten Design arbeitet und dieses testet. Im Falle von Alder Lake durchliefen natürlich neben den Desktop-Modellen auch die Mobile-Varianten diese Tests. Ein Teil der Arbeiten kann Intel automatisieren. So gibt es Teststationen, in denen die Prozessoren mit unterschiedlichen RAM-Modulen und Bestückungen getestet werden. Ein Roboter platziert dabei den Prozessor im Sockel und auch das Austauschen des RAMs geschieht automatisch. Nur so ist es überhaupt möglich, dass eine derartige Anzahl an Prozessoren in diesem Umfang validiert werden kann.

Schlussendlich sei auch noch erwähnt, dass die Tests unter kontrollierten Bedingungen stattfinden müssen. An allen Teststationen verliefen Rohr- und Schlauchleitungen, in denen Wasser mit einer definierten Temperatur oder Frischluft herangeschafft wurde. In speziellen Kühlern sorgte das Wasser dann für eine immer gleichbleibende Temperatur, während die Luft zum Beispiel dazu verwendet wird, Kondenswasser zu vermeiden, indem der Kühlblock immer mit trockener Luft umgeben ist.

Den Umfang des Testens und des Validierens drücken folgende Zahlen sicherlich am besten aus: Bis ein Prozessor wie Alder Lake das Licht der Welt erblickt, werden bis zu 250.000 Prozessoren und 15.000 Testboards benötigt. Über die Schritte der ES1 (Engineering Sample), ES2, QS (Qualifikation Sample), PRQ, PV dauert dies bis zu 15 Monate, bis die Prozessoren nach dem Bring-Up im Handel landen können. Bereits in der ES-Phase muss das finale Design erstellt und abgeliefert werden, damit die Fertigung stattfinden kann. In den QS-, PRQ- und PV-Versionen sollten daher keine größeren Schnitzer mehr zu finden sein.

Im Rahmen unseres Besuchs das IDC sahen wir Raptor Lake beispielsweise auch schon mit DLVR und auch ein Core i9-13900KS drehte bereits seine Runden.

Der Reinraum in der Fab 28

Einen noch sensibleren Bereich haben wir mit der Fab 28 betreten. Dies ist eine der größten Fertigungsstädten von Intel, die man weltweit betreibt. Weitere befinden sich Portland, im US-Bundesstaat Oregon sowie in Arizona. Neben Nordirland versteht sich Israel als zweite "europäische" Fertigung von Intel, in der Chips in Intel 7 (10 nm) hergestellt werden. Hier laufen die meisten Alder-Lake- und Raptor-Lake-Prozessoren vom Band. Über das Volumen der in der Fab 28 gefertigten Chips macht Intel keinerlei Angaben. Ungern sollen solche Details an die Öffentlichkeit gelangen. 24/7 laufen die Prozesse, 364 Tage im Jahr - nur an Jom Kippur steht die Fab sozusagen auf Standby.

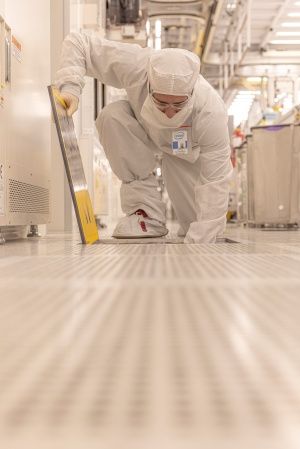

Bevor es aber in die eigentliche Fertigung ging, mussten wir uns zunächst einmal umziehen. Die sogenannten Bunny-Suits sollen den Reinraum vor Kontamination schützen. Jegliches Staubkörnchen, ja sogar Make-up und Haargel kann Verunreinigungen hervorrufen und dürfen daher im Vorfeld nicht aufgetragen bzw. verwendet werden. Auf 28 l an Luftvolumen darf sich in einem Reinraum der Kategorie 1 nur ein Staubkörnchen befinden. Über eine Schleuse geht es zunächst in einen Umkleideraum.

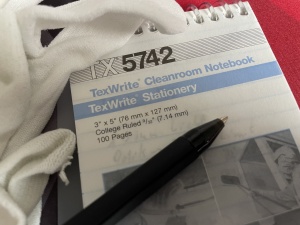

Der komplette Bunny-Suite besteht aus einem Überzieher für Kopf, Füße und spezielle antistatische Handschuhe. Darüber folgt ein Einteiler, in den hineingeschlüpft werden muss. Noch einmal Handschuhe darüber und selbst Papier und Stift müssen für den Einsatz im Reinraum zertifiziert sein. Über eine weitere Schleuse geht es dann in die eigentliche Fertigung im Reinraum.

Bis aus einem Wafer ein fertig belichteter Wafer wird, aus dem die Chips geschnitten werden, vergehen hunderte wenn nicht tausende einzelne Prozessschritte und mehrere Wochen bis Monate. In Containern, den Front Opening Universal Pods (FOUP), die an einem Schienensystem an der Decke fahren, werden die Wafer zu den einzelnen Prozessschritten gebracht. Dies geschieht mit bis zu 3 m/s. In einem FOUP befinden sich 25 Wafer. Mit diesen direkt in Kontakt kommt keiner der Mitarbeiter. Sie sind nur dazu da, um die Maschinen zu bedienen und zu warten. Die Industrie hat sich aktuell auf Wafer mit einem Durchmesser von 300 mm festgelegt und dabei wird es wohl auch noch einige Zeit bleiben. Zwar gibt es immer wieder Bestrebungen auf einen größeren Durchmesser von 450 mm wechseln zu wollen, das Problem ist aber, dass sämtliche Infrastruktur und die verfügbaren Maschinen auf 300 mm ausgelegt sind. Ein Henne-Ei-Problem, welches wohl nicht so schnell beseitigt sein wird. Natürlich wäre es besser größere Wafer zu verwenden, die Ausbeute würde vermeintlich steigen.

Doch auch wenn wir uns in einem Reinraum befinden: Auch hier kann es zu Verunreinigungen kommen. Jede Wafer wird auf solche untersucht und im Rahmen dieser Untersuchung wird dann auch gleich analysiert, ob es möglich ist, diese zu beseitigen. Die Überwachung dieser Verunreinigungen ist Aufgabe des DREAM-Teams. DREAM steht für Defect Remediation Engineering and Metrology. Eine stetige Überwachung der eventuell auftretenden Fehler in der Fertigung sollen eine schnelle Ursachenfindung und Behebung ermöglichen. "Every Die wants to live" ist das Motto der Fab 28 in Israel und diesem hat man sich verschrieben.

Die Fab 28 umfasst eine Reinraumfläche von 4-5 Fußballfeldern – auch hier will man keine genauen Zahlen preisgeben. Zum Vergleich: Die geplanten Mega-Fabs in Magdeburg und Ohio sind in der ersten Ausbaustufe mit jeweils sechs Fußballfeldern an Reinraumfläche geplant. Neben den Reinräumen bedarf es aber auch noch viel Infrastruktur. So Umfasst das Gebäude mehrere Etagen, von denen nur die zentrale Etage den Reinraum beherbergt. Darüber und darunter liegen mehreren Ebenen, die der Versorgung des Reinraums mit Wasser, Energie, sowie der notwendigen Chemikalien und und Gase dienen. Externe Gebäudeteile bereiten das Wasser auf oder beherbergen Notstromversorgungssysteme.

Wie auf einem Wafer ein Chip entsteht, darauf sind wir noch gar nicht eingegangen. In einer Handling-Maschine wird auf die Wafer ein Fotolack aufgebracht. Dazu dreht sich der Wafer und eine bestimmte Menge wird aufgetragen. Die Fliehkraft sorgt dafür, dass sich der Lack gleichmäßig verteilt.

Danach gehen die Wafer in die Belichtungseinheit. Hier befindet sich eine Laserquelle mit einem Laser mit einer Wellenlänge von 193 nm. Eine sogenannte Kondenser-Linse bündelt das Licht, führt es durch eine Maske und darauf erfolgt die Projektion auf den Wafer. Der Fotolack reagiert an den Stellen, an denen Licht auf ihn trifft. Diese Stellen können per Trocken- oder Nass-Ätzen behandelt werden. Dort wo Material entfernt wurde, können das Metall oder andere Materialien eingebracht werden. Schicht für Schicht entstehen so die Strukturen, die letztendlich zu den Transistoren und dem Routing innerhalb des Chips werden.

Die fertigen Wafer werden nicht in Israel zu Chips verarbeitet. Intel hat auf der Welt verteilt einige Packaging-Fabs, in denen via Diamantsäge zwischen den Chips geschnitten wird und diese vereinzelt werden.

Überwacht wird der Reinraum-Prozess über das Remote Operation Center (ROC). Es handelt sich sozusagen um das Gehirn und die Steuereinheit des gesamten Prozesses. Im Idealfall sind die Fertigungsstraßen zu 100 % ausgelastet. Diesen Idealfall erreicht man aber natürlich nur in der Theorie, da es immer wieder zu Ausfällen einzelner Maschinen kommen kann. Auch im ROC sind 24/7 und an 364 Tagen im Jahr Mitarbeiter anwesend. Wie im Reinraum fährt Intel hier ein 12-Stunden-Schichtsystem. Kommt es an einer Maschine zu Problemen, wird ein Techniker dorthin geschickt. Die Maschinen sind aber nicht mit Zahlen oder einer Zeichenfolge benannt, sondern recht einfach über Piktogramme mit Tiersymbolen. Somit wird in der Kommunikation spöö zwischen ROC und den Technikern verhindert werden, dass es zu Verwechselungen kommt.

Gleich neben der Fab 28 entsteht die Fab 38. Auch in Israel investiert Intel kräftig. Die neue Fab soll ebenfalls 300 mm Wafer belichten und höhere Reinräume für den Einsatz der zukünftigen HighNA-Maschinen bieten. Welche Fertigungsgröße Intel in der Fab 38 verwenden wird, wollte man allerdings nicht verraten. Man verwies nur auf den konzernweiten Plan ab der zweiten Jahreshälfte 2022 bereits mit Intel 4 beginnen zu wollen, bevor dann in der zweiten Jahreshälfte 2023 die Fertigung in Intel 3 folgen soll. Der große Schritt auf Intel 20A soll dann im ersten Halbjahr 2024 erfolgen und Intel 18A ist für die zweite Jahreshälfte 2024 vorgesehen. Alle das wird für die Fab 38 in Israel allerdings keinerlei Rolle mehr spielen, denn sie wird es später fertiggestellt.

Die neuesten Fertigungsgrößen und Technologien werden in Hillsboro bei Portland, im US-Bundesstaat Oregon, ins Leben gerufen. Dort steht die Fab D1X, die aktuell für 1,5 Milliarden US-Dollar erweitert wird. Hier wird und werden auch die ersten HighNA-Belichtungsmaschienen um Einsatz kommen. D1X ist der Standort für die Entwicklung neuer Prozesstechnologien für Intel, die dann in anderen Fabs, wie beispielsweise die Fab 28 oder später Fab 38 in Israel, überführt werden.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen