Werbung

Durch die Bank arbeiten die Halbleiterfertiger an einer Umsetzung für zukünftige Fertigungstechnologien. EUV wird ab 7 nm eine Rolle spielen, aber die Herausforderungen sind nicht nur in der reinen Belichtung zu suchen, sondern auch in den verwendeten Materialien zur Dotierung und in der Ausführung der Transistoren selbst. Ein Unternehmen namens Unisantis hat zusammen mit Imec eine neue SRAM-Zelle vorgestellt, die Surrounding Gate Transistoren verwendet.

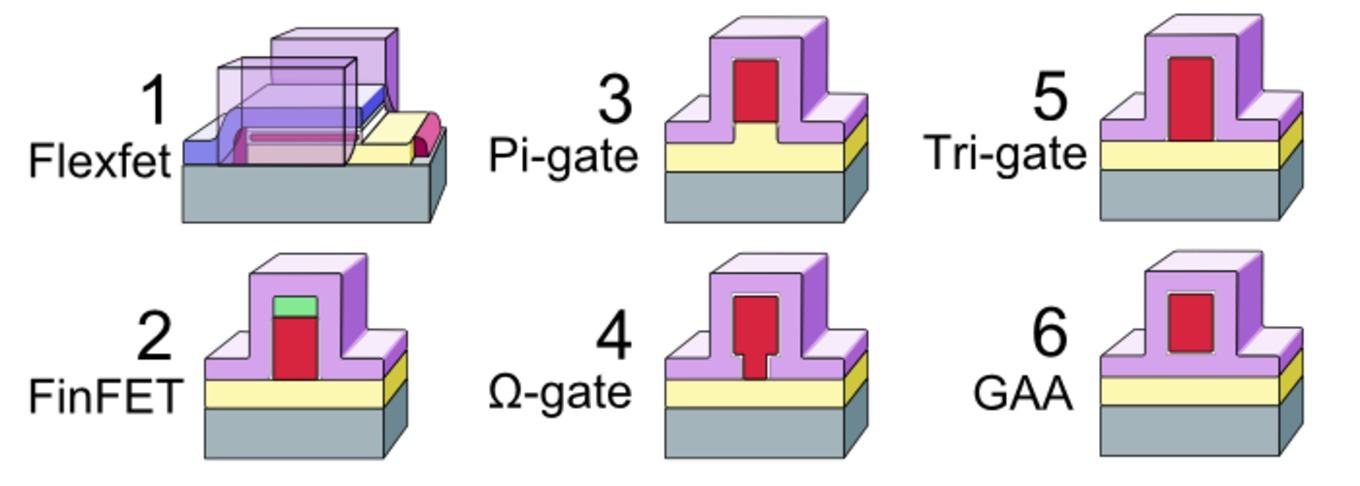

Planare Transistoren sind im Grunde in zwei Dimensionen aufgebaut, mit den aktuell verwendeten FinFET-Transistoren ist eine dritte Ebene hinzugekommen, aber den vom Grundsatz her perfekten Transistor gibt es aktuell noch nicht. Vor gut 30 Jahren wurden von einem der Gründer von Unisantis das Konzept zu einem vollständig umschlossenen Transistor entworfen – der Surrounding Gate Transistor oder kurz GAA für Gate-All-Around.

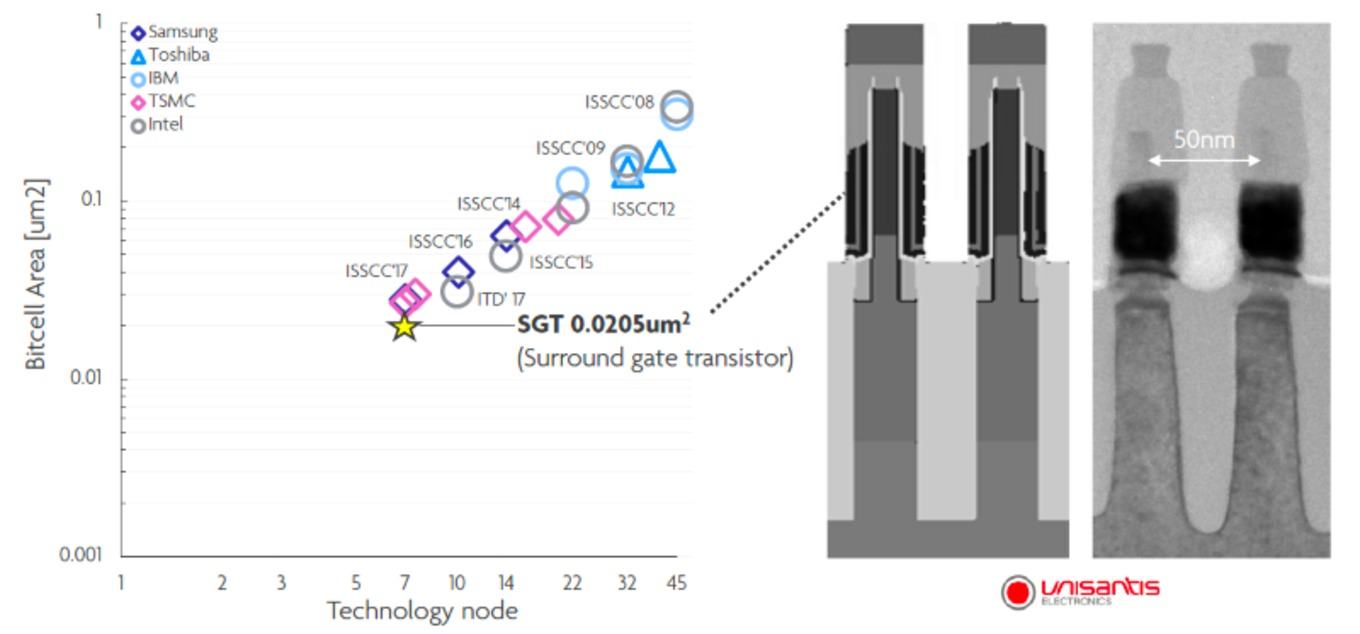

Da das Gate hier vollständig umschlossen ist, ist auch von einem Nanowire die Rede. An einer solchen Technologie arbeiten alle Halbleiterunternehmen, ob Samsung, TSMC, Intel oder IBM. Der Abstand zwischen den GAA beträgt dabei 50 nm. Die Transistoren sind dazu ausgelegt, in einem SRAM zu arbeiten, der in 5 nm gefertigt wird. Für den Einsatz in Logiken eines Prozessors eignen sich diese Transistoren derzeit noch nicht. Bis in die 5-nm-Fertigung hinein wird FinFET die Wahl bei der Fertigung der Transistoren sein, mit der Fertigung in 5 nm wird der Übergang auf die GAA-Transistoren erfolgen, die dann spätestens ab 3 nm unabdingbar sein sollen.

Im Februar stellte Samsung eine 6T-256-MBit-SRAM-Zelle mit einer Fläche von 0,026 mm² vor. Gefertigt hat Samsung diese in 7 nm unter Zuhilfenahme von EUV. Die SRAM-Zellen von Unisantis sollen nur noch 0,0205 mm² bis 0,0184 mm² groß sein und damit um ein Vielfaches kleiner.

Nun wird es in den kommenden Jahren darum gehen, die Technik aus dem Labor in die Praxis zu überführen. Die Halbleiterhersteller kämpfen aber an mehreren Fronten, die allesamt dazu führen, dass die Fertigung immer kleinerer Transistoren auch immer aufwändiger wird. Derzeit kämpft Intel mit Problemen bei der Fertigung in 10 nm, während 7 nm bei Samsung, TSMC und auch Intel selbst keine Probleme machen sollen.