News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

Transistor

-

TSMC 2024 Technology Symposium: N2-Familie enthält NanoFlex für mehr Zellflexibilität

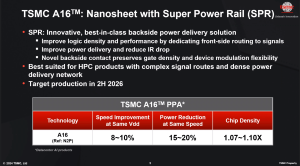

Neben der Vorstellung der ersten Umsetzung eines Back Side Power Delivery Network (BSPDN) in der A16-Fertigung verkündet TSMC laut Anandtech auf dem 2024 Technology Symposium deutliche Verbesserungen für die geplanten N2-Fertigungsschritte, die mittels NanoFlex-Technologie deutlich effizienter werden sollen. Alle bisher geplanten N2-Fertigungsschritte (N2, N2P, N2X) werden NanoFlex unterstützen. Dabei handelt es sich um eine Technologie,... [mehr]

Neben der Vorstellung der ersten Umsetzung eines Back Side Power Delivery Network (BSPDN) in der A16-Fertigung verkündet TSMC laut Anandtech auf dem 2024 Technology Symposium deutliche Verbesserungen für die geplanten N2-Fertigungsschritte, die mittels NanoFlex-Technologie deutlich effizienter werden sollen. Alle bisher geplanten N2-Fertigungsschritte (N2, N2P, N2X) werden NanoFlex unterstützen. Dabei handelt es sich um eine Technologie,... [mehr] -

IEDM 2023: Intel, TSMC und andere arbeiten an Transistoren in 2 nm und weniger

Die Forschung an neuen Technologien für die rückseitige Spannungsversorgung der Transistoren ist auch eine Notwendigkeit aus der Weiterentwicklung der Transistor-Technologien. Genau wie PowerVia als Technik sollen uns bei Intel im kommenden Jahr die ersten RibbonFET erwarten. Neben Intel präsentiert aber auch TSMC aus dem 2023 IEEE International Electron Devices Meeting (IEDM 2023) seine zukünftigen Ansätze im Bereich der... [mehr]

Die Forschung an neuen Technologien für die rückseitige Spannungsversorgung der Transistoren ist auch eine Notwendigkeit aus der Weiterentwicklung der Transistor-Technologien. Genau wie PowerVia als Technik sollen uns bei Intel im kommenden Jahr die ersten RibbonFET erwarten. Neben Intel präsentiert aber auch TSMC aus dem 2023 IEEE International Electron Devices Meeting (IEDM 2023) seine zukünftigen Ansätze im Bereich der... [mehr] -

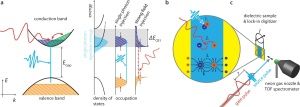

1 PHz sind das Limit für die Schaltgeschwindigkeit von Transistoren

Vor allem bei den Prozessoren ist der Takt ein Merkmal, auf das viele Nutzer und auch wir im Rahmen der Tests achten. Für das Marketing ist die Angabe einer Taktfrequenz besonders wichtig und daher verwundert es auch nicht, dass die Hersteller gerne damit werben – seien es die 5 GHz die ein Ryzen 9 6980 erreicht oder die 5,5 GHz für zwei Kerne des Core i9-12900KS. Ein deutsch-österreichisches Physikteam der TU Graz hat nun die physikalische... [mehr]

Vor allem bei den Prozessoren ist der Takt ein Merkmal, auf das viele Nutzer und auch wir im Rahmen der Tests achten. Für das Marketing ist die Angabe einer Taktfrequenz besonders wichtig und daher verwundert es auch nicht, dass die Hersteller gerne damit werben – seien es die 5 GHz die ein Ryzen 9 6980 erreicht oder die 5,5 GHz für zwei Kerne des Core i9-12900KS. Ein deutsch-österreichisches Physikteam der TU Graz hat nun die physikalische... [mehr] -

IEDM 2021: Intel über Forschung, Fertigung in 2025 und darüber hinaus

Im Sommer präsentierte Intel nicht nur seine IDM-2.0-Strategie und benannte seine Fertigungsgrößen um, sondern gab außerdem einen Ausblick auf das, was uns ab 2024/25 erwarten wird. Neue Entwicklungen im Bereich der Materialforschung bilden meist die Basis für all das, was dann im einzelnen Transistor, über gestapelte Transistoren, im Aufbau des CMOS-Designs bis hin zum Packaging zum Einsatz kommt. Auf dem International Electron Devices... [mehr]

Im Sommer präsentierte Intel nicht nur seine IDM-2.0-Strategie und benannte seine Fertigungsgrößen um, sondern gab außerdem einen Ausblick auf das, was uns ab 2024/25 erwarten wird. Neue Entwicklungen im Bereich der Materialforschung bilden meist die Basis für all das, was dann im einzelnen Transistor, über gestapelte Transistoren, im Aufbau des CMOS-Designs bis hin zum Packaging zum Einsatz kommt. Auf dem International Electron Devices... [mehr] -

Was in AMDs Ryzen steckt: Ein 7-nm-Transistor untersucht

Mittels eines Rasterelektronenmikroskop schaute sich Roman Hartung an der Hochschule Heilbronn schon einen Ryzen 9 3950X und Core i9-10900K an, um eventuelle Größenunterschiede in der 7-nm- und 14-nm-Fertigung zu ergründen. Nun besuchte er das deutsche Unternehmen Kleindiek, die sich auf das sogenannte Nanoprobing spezialisiert haben und hier mit nahezu allen großen Chipherstellern und Auftragsfertigern zusammenarbeiten. Ziel... [mehr]

Mittels eines Rasterelektronenmikroskop schaute sich Roman Hartung an der Hochschule Heilbronn schon einen Ryzen 9 3950X und Core i9-10900K an, um eventuelle Größenunterschiede in der 7-nm- und 14-nm-Fertigung zu ergründen. Nun besuchte er das deutsche Unternehmen Kleindiek, die sich auf das sogenannte Nanoprobing spezialisiert haben und hier mit nahezu allen großen Chipherstellern und Auftragsfertigern zusammenarbeiten. Ziel... [mehr] -

IBM zeigte erste in 2 nm gefertigte Chips

IBM ist offenbar ein Durchbruch in der Fertigung von Transistoren gelungen. Alle großen Halbleiterhersteller sind auf der Suche nach Technologien, die es ermöglichen, Transistoren immer kleiner zu fertigen und dichter zu packen. Die Fertigung in 2 nm ermöglicht eine um 45 % höhere Leistung im Vergleich zur Fertigung in 7 nm – oder aber die Leistungsaufnahme kann um 75 % reduziert werden. Wohlgemerkt sprechen wir hier von... [mehr]

IBM ist offenbar ein Durchbruch in der Fertigung von Transistoren gelungen. Alle großen Halbleiterhersteller sind auf der Suche nach Technologien, die es ermöglichen, Transistoren immer kleiner zu fertigen und dichter zu packen. Die Fertigung in 2 nm ermöglicht eine um 45 % höhere Leistung im Vergleich zur Fertigung in 7 nm – oder aber die Leistungsaufnahme kann um 75 % reduziert werden. Wohlgemerkt sprechen wir hier von... [mehr] -

IEDM 2020: Intel will durch gestapelte Transistoren deren Dichte verdoppeln

Auf dem diesjährigen IEEE International Electron Devices Meeting (IEDM) präsentierte Intel verschiedene Weiter- und Neuentwicklungen aus dem Bereich der Fertigungstechnologien. Eine der wichtigsten Forschungen betrifft die sogenannte Self-Aligned 3D Stacked Multi-Ribbon CMOS Transistoren – selbstausrichtende, gestapelte Transistoren, welche Intel theoretisch in die Lage versetzen sollen, die Transistordichte zu verdoppeln. Die... [mehr]

Auf dem diesjährigen IEEE International Electron Devices Meeting (IEDM) präsentierte Intel verschiedene Weiter- und Neuentwicklungen aus dem Bereich der Fertigungstechnologien. Eine der wichtigsten Forschungen betrifft die sogenannte Self-Aligned 3D Stacked Multi-Ribbon CMOS Transistoren – selbstausrichtende, gestapelte Transistoren, welche Intel theoretisch in die Lage versetzen sollen, die Transistordichte zu verdoppeln. Die... [mehr] -

GAA-Transistor als Nanowire für Transistoren in 5 nm und kleiner

Durch die Bank arbeiten die Halbleiterfertiger an einer Umsetzung für zukünftige Fertigungstechnologien. EUV wird ab 7 nm eine Rolle spielen, aber die Herausforderungen sind nicht nur in der reinen Belichtung zu suchen, sondern auch in den verwendeten Materialien zur Dotierung und in der Ausführung der Transistoren selbst. Ein Unternehmen namens Unisantis hat zusammen mit Imec eine neue SRAM-Zelle vorgestellt, die Surrounding Gate... [mehr]

Durch die Bank arbeiten die Halbleiterfertiger an einer Umsetzung für zukünftige Fertigungstechnologien. EUV wird ab 7 nm eine Rolle spielen, aber die Herausforderungen sind nicht nur in der reinen Belichtung zu suchen, sondern auch in den verwendeten Materialien zur Dotierung und in der Ausführung der Transistoren selbst. Ein Unternehmen namens Unisantis hat zusammen mit Imec eine neue SRAM-Zelle vorgestellt, die Surrounding Gate... [mehr]