Werbung

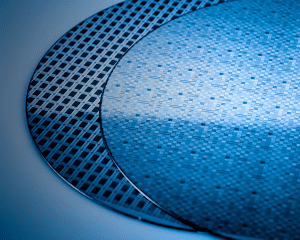

Marvell ist einerseits direkter Hersteller von Chips für Netzwerk-, Automotive und Storage-Anwendungen, man ist aber auch Anbieter von IP (Intellectual Property) für solche Chips. Entsprechend arbeitet man direkt und indirekt mit Auftragsfertigern wie TSMC zusammen und verkündet nun, dass man gemeinsam mit dem Taiwanisches Chiphersteller eine Technologie-Plattform entwickeln wird, die auf eine Fertigung in 2 nm ausgelegt ist.

Bisher nutzt Marvell bereits die Fertigung in 5 und 3 nm bei TSMC. Mit der Fertigung in 2 nm will das Unternehmen die Leistung und Effizienz seiner Lösungen weiter verbessern. Dies gilt dann eben nicht nur für die eigenen Chips und Controller, sondern auch für die IP in Form von SerDes, Prozessor-Subsystemen, Verschlüsselungs-Engines, SoC-Fabrics, Chip-to-Chip-Interconnects und eine Reihe von physikalischen Layern für hohe Datenübertragungsraten.

Die Notwendigkeit nach immer schnelleren und zugleich effizienteren Interconnects und einer entsprechenden Netzwerk-Infrastruktur ergibt sich aus der Tatsache, dass schnelle KI- und HPC-Beschleuniger auch auf eine ebenso schnelle Anbindung angewiesen sind. Zugleich darf der Platzbedarf auf den Chips für solche IP (Interconnects und direkte Netzwerk-Anbindung) nicht weiter steigen. Eine Auslagerung per Chiplet ist auch nur dann sinnvoll, wenn die Chips damit weiter skalieren können.

Hand in Hand mit den modernsten Fertigungstechnologien zu gehen ist also sinnvoll. Aus diesem Grund arbeiten Marvell und TSMC zusammen, um vermutlich ab 2025 die ersten Chips in 2 nm fertigen zu können bzw. per Design-Kit die IP von Marvell auf eine Fertigung in 2 nm vorzubereiten.