Werbung

Der Bedarf nach immer größerem und schnellerem Grafikspeicher wird sowohl bei AMD als auch bei NVIDIA bereits in der nächsten GPU-Generation eine wichtige Rolle spielen. SK Hynix sprach sogar bereits mehrfach über eine enge Zusammenarbeit mit AMD und so wird eine mögliche Radeon R9 390X mit High-Bandwidth-Memory erwartet. Auch einige technische Details zu HBM sind bereits bekannt und wurden bei uns schon ausführlich behandelt.

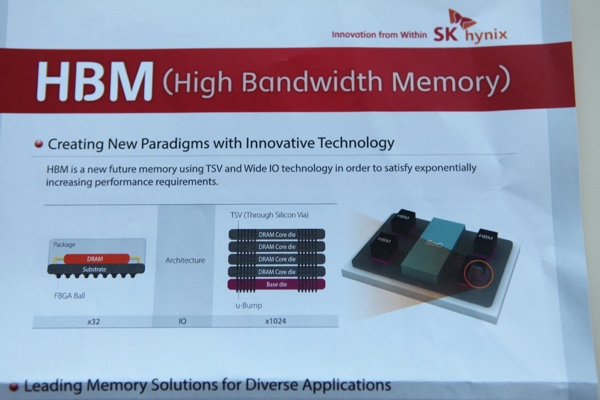

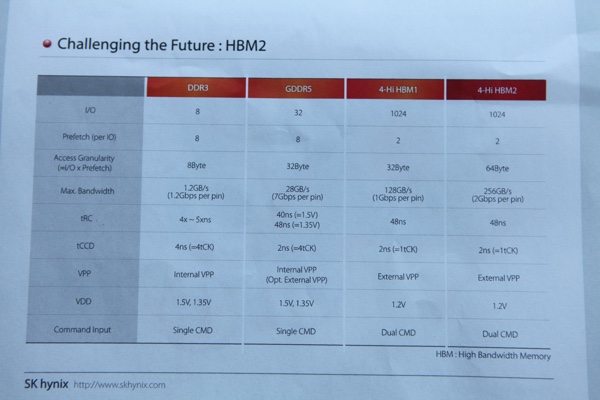

Beim HBM wird der DRAM-Speicher nicht mehr neben der/dem GPU/CPU/SoC auf dem PCB untergebracht, sondern direkt auf der/dem GPU/CPU/SoC. Dazu werden zusätzliche Silizium-Layer auf dem jeweiligen Chip angebracht, sogenannte Through Silicon Vias (TSVs) verbinden beide Komponenten. In der ersten Generation von HBM nit vier Layern sollen Speicherbandbreiten von 128 GB pro Sekunde erreicht werden. Die Speicherkapazität liegt bei maximal 4 GB. Auf der aktuell stattfindenden GPU Technology Conference stellt auch SK Hynix seine aktuellen Entwicklungen aus. Darunter ist unter anderem auch der GDDR5-Speicher, der auf der GeForce GTX Titan X zum Einsatz kommt (Hardwareluxx-Artikel).

In einer ersten Ausbaustufe will SK Hynix 2 GBit pro Core-Die-Layer verbauen. Dies entspricht einem Gesamt-Speicherausbau von 1 GB für ein Chip-on-Wafer, die jeweils mit einem 128 Bit breiten Speicherinterface angebunden sind. Theoretisch denkbare wäre der Einsatz mehrerer dieser Chips auf einer GPU. Eine mögliche Konfiguration wären vier Chips, was einem Speicherausbau von 4 GB entspräche, die über ein insgesamt 512 GB pro Sekunde breites Speicherinterface angebunden wären.

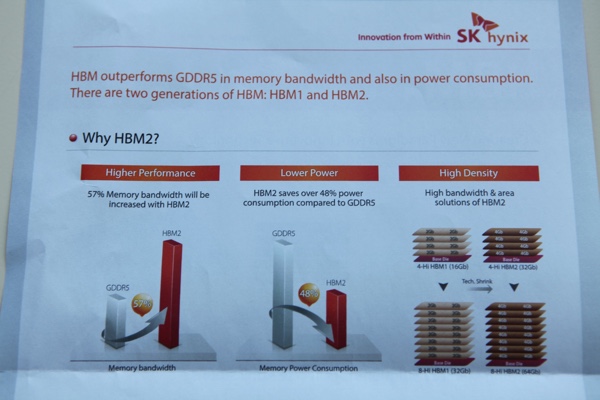

Hier werden auch gleich die Vorteile von HBM deutlich, denn 512 Bit erreicht aktuell nur die "Hawaii"-GPU von AMD und deren Architektur kann als extrem komplex bezeichnet werden, was unter anderem dem komplizierten Speicherinterface anzurechnen ist. Ein weiterer Vorteil ist die geringe Leitungsaufnahme. Aktuell wird schneller GDDR5-Speicher mit 1,5 Volt betrieben. HBM gibt sich mit 1,2 Volt genügsamer, zudem fließen hier wesentlich geringere Ströme.

Die nun aufgetauchten technischen Daten von HBM2 zeigen für die zweite Ausbaustufe von SK Hynix 8 GBit pro Core-Die-Layer. Diese können in vier oder gar acht Lagen gestapelt werden, so dass der Speicherausbau pro Chip-on-Wafer bei 4 bzw. 8 GB liegt. Die Speicherbandbreite verdoppelt sich auf 256 GB pro Sekunde. Es bleibt bei der relativ geringen Spannung von 1,2 Volt. Das Ausstellen von SK Hynix auf der GTC 2015 ist wohl der deutlichste Hinweis, dass der 3D Memory der "Pascal"-GPU von SK Hynix stammen wird, was im Zusammenhang mit HBM2 auch Sinn machen würde.