Werbung

Die Anbindung von Speicher spielt für aktuelle CPUs und GPUs eine immer wichtigere Rolle. Nicht ohne Grund wachsen die Caches immer weiter an und die Hersteller wie AMD und NVIDIA lassen sich im GPU-Bereich immer mehr einfallen, um die zur Verfügung stehende Speicherbandbreite besser nutzen zu können. Dazu gehören zunächst einmal Software-Mechanismen, die mittels Speicherkomprimierung die übertragenen Datenmengen reduzieren. NVIDIA präsentierte auf der GTC den "Maxwell"-Nachfolger "Pascal", der unter anderem 3D-Memory oder auch Stacked Memory einsetzen soll.

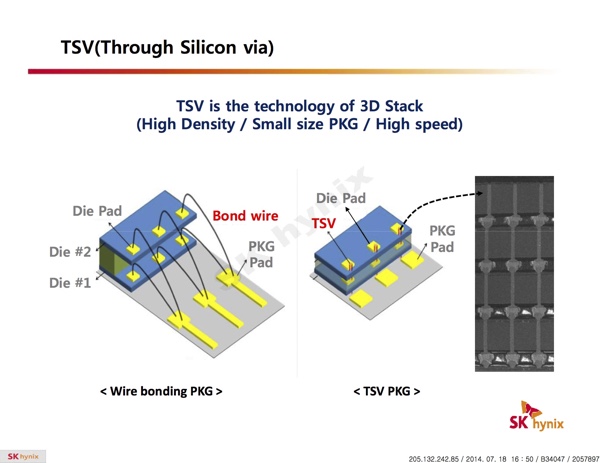

Auch AMD werden Arbeiten an einer besseren und vor allem schnelleren Anbindung des Grafikspeichers nachgesagt. Dabei arbeitet man mit SK Hynix zusammen. Nun ist eine Präsentation aufgetaucht, welche die Pläne für den sogenannten High Bandwith Memory (HBM) darlegt. Beim HBM wird der DRAM-Speicher nicht mehr neben der/dem GPU/CPU/SoC auf dem PCB untergebracht, sondern direkt auf der/dem GPU/CPU/SoC. Dazu werden zusätzliche Silizium-Layer auf dem jeweiligen Chip angebracht, sogenannte Through Silicon Vias (TSVs) verbinden beide Komponenten. Ähnliche Techniken werden heute bereits bei den modernen SoCs eingesetzt. So besitzt die PlayStation Vita einen 128 MB großen RAM im selben Package wie der SoC. Hier spricht man aber noch nicht von Staket Memory, 3D Memory oder TSV, da ein separater Chip im Package untergebracht ist.

Externe Bond Wires wären theoretisch auch in der Lage, unterschiedliche Lagen miteinander bzw. mit einem Package zu verbinden, allerdings sind diese je nach Fertigungsgröße nur noch schwer bis gar nicht realisierbar und zudem auch noch anfällig gegen elektromagnetische Störungen untereinander. TSVs sparen Platz und sind deutlich weniger anfällig.

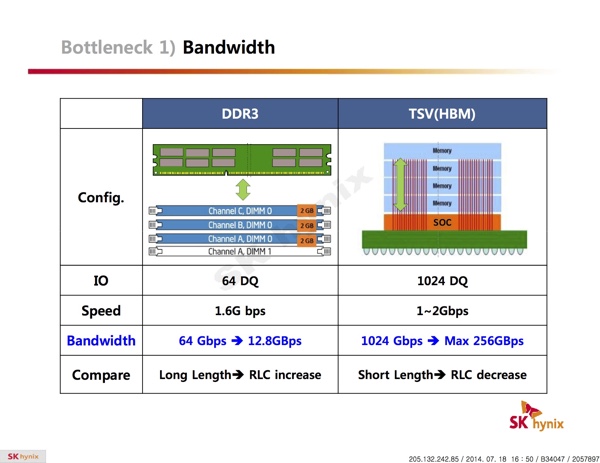

Die Möglichkeit höhere Frequenzen beim Speicherinterface zu verwenden und dieses auch noch deutlich breiter gestalten zu können, hat natürlich einen positiven Einfluss auf die Speicherbandbreite insgesamt. SK Hynix vergleicht einen DDR3-Speicher gegen per TSV angebundenen HBM. Bei vergleichbarem Speichertakt erhöht sich die Bandbreite von 12,8 auf 256 GB pro Sekunde - natürlich ist dies abhängig von der jeweiligen DDR-Konfiguration mit Dual- oder Quad-Channel-Betrieb. Allerdings werden mit 256 GB pro Sekunde offenbar bereits in der ersten Generation Speicherbandbreiten erreicht, die wir aktuell von modernen GPUs mit 256 Bit breitem Speicherinterface und schnellem GDDR5-Speicher kennen.

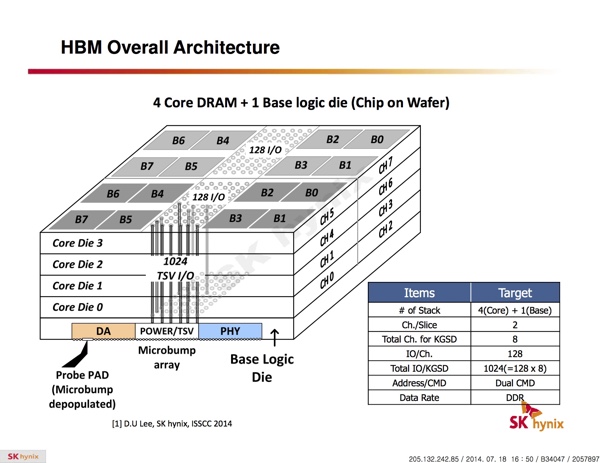

Erstmals im Detail zu sehen ist auch der Aufbau eines HBM. Dieser besteht aus fünf Layern, die auf dem Chip sitzen. Der unterste Layer (Base Logic Die) dient dabei der Anbindung an den Chip und führt die TSVs sowie die Versorgung des Speichers. In einer ersten Ausbaustufe befinden sich darüber vier sogenannte Core-Die-Layer. Jeder dieser vier Core-Die-Layer teilt sich wiederum in zwei Blöcke zu noch einmal vier Speicher-Blöcken auf. Die beiden Speicherblöcke einer jeden Core-Die-Layer sind über ein 128-I/O-Verbindungen angebunden. Aus 4 x 2 x 128 ergeben sich 1.024 I/O-Kontakte bzw. TSVs des Speichers, was letztendlich einem 128 Bit breiten Speicherinterface entspricht.

In einer ersten Ausbaustufe will SK Hynix 2 GBit pro Core-Die-Layer verbauen. Dies entspricht einem Gesamt-Speicherausbau von 1 GB für ein Chip-on-Wafer, die jeweils mit einem 128 Bit breiten Speicherinterface angebunden sind. Theoretisch denkbare wäre der Einsatz mehrerer dieser Chips auf einer GPU. Eine mögliche Konfiguration wären vier Chips, was einem Speicherausbau von 4 GB entspräche, die über ein insgesamt 512 GB pro Sekunde breites Speicherinterface angebunden wären. Hier werden auch gleich die Vorteile von HBM deutlich, denn 512 Bit erreicht aktuell nur die "Hawaii"-GPU von AMD und deren Architektur kann als extrem komplex bezeichnet werden, was unter anderem dem komplizierten Speicherinterface anzurechnen ist. Ein weiterer Vorteil ist die geringe Leitungsaufnahme. Aktuell wird schneller GDDR5-Speicher mit 1,5 Volt betrieben. HBM gibt sich mit 1,2 Volt genügsamer, zudem fließen hier wesentlich geringere Ströme.

Für die zweite Ausbaustufe sieht SK Hynix 8 GBit pro Core-Die-Layer vor. Diese können in vier oder gar acht Lagen gestapelt werden, so dass der Speicherausbau pro Chip-on-Wafer bei 4 bzw. 8 GB liegt. Die Speicherbandbreite verdoppelt sich auf 256 GB pro Sekunde. Auch hier sind dann natürlich mehrere dieser HBM-Module auf einem Chip denkbar, was die Kapazität und Anbindung weiter erhöht.

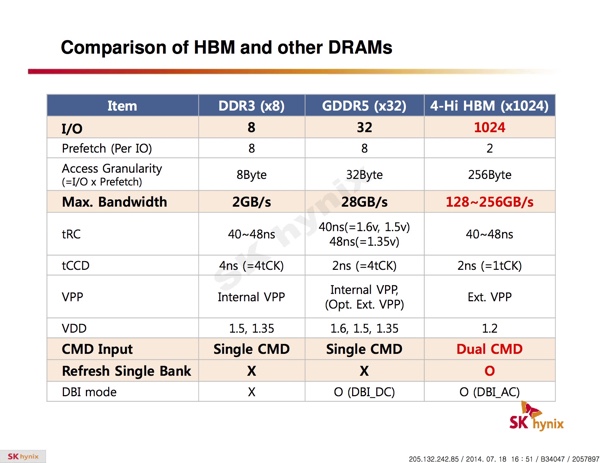

Im Vergleich zu DDR- und GDDR-Speicher werden noch einmal die Vorteile herausgestellt. Die zur Verfügung stehende Bandbreite wird deutlich gesteigert und damit eines der wichtigsten Probleme aktueller Architekturen deutlich reduziert. Keinerlei Vorteile besitzt HBM im Hinblick auf die Latenzen. Dafür aber wird die Leistungsaufnahme deutlich geringer sein.

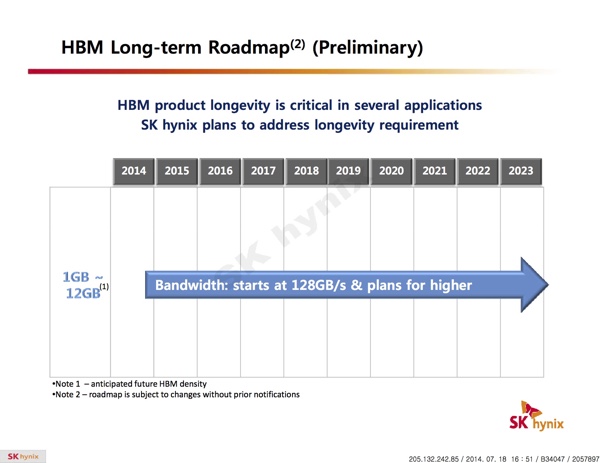

Noch etwas schwer tut sich SK Hynix bei der Roadmap für zukünftige Ausbaustufen. Allerdings sollen noch in diesem Jahr erste Produkte mit HBM der ersten Generation auf den Markt kommen. Bereits für das kommende Jahr sieht SK Hynix erste Produkte mit Speicher in acht Layern vor. Hier bietet sich nun dank der Zusammenarbeit mit AMD unweigerlich der Einsatz auf den kommenden GPUs an. Gerüchte dazu gibt es bereits vielfach und daher haben wir nun auch einmal versucht die Technik und Vorteile besser herauszustreichen, denn unweigerlich werden wir uns damit zukünftig beschäftigen müssen. Auch NVIDIA verfolgt, wie bereits in der Einleitung angesprochen, ähnliche Pläne.