Werbung

Samsung hat eine neue Art High Bandwidth Memory (HBM) vorgestellt, der nicht nur ein einfacher Speicher ist, sondern der eine Processing-in-Memory (PIM) Architektur enthält. Es handelt sich laut Samsung um den ersten HBM, der über eine solche Art der integrierten Recheneinheiten verfügt.

Noch ist nicht bekannt, wie genau die integrierten Recheneinheiten funktionieren, bzw. welche Rechenleistung diese erreichen. Samsung nennt keinerlei Leistungsdaten. Höchstwahrscheinlich handelt es sich um Optimierungen der Daten selbst, um parallele Zugriffe und das Speichermanagement zu optimieren. Wohl aber soll der HBM-PIM sowohl für das Inferencing mit niedriger Genauigkeit als auch das Training mit hoher Genauigkeit geeignet sein. Der Vorteil von integrierten Recheneinheiten liegt in der hohen Bandbreite und den geringen Latenzen, die so erreicht werden können.

Kwangil Park, Senior Vice President der Memory-Sparte: "Our groundbreaking HBM-PIM is the industry’s first programmable PIM solution tailored for diverse AI-driven workloads such as HPC, training and inference. We plan to build upon this breakthrough by further collaborating with AI solution providers for even more advanced PIM-powered applications."

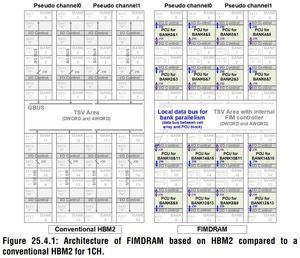

Ein HBM-Chip besteht aus mehreren Ebenen. Der Logic-Die bildet die Basis und stellt die Verbindung zum Speicherinterface her. Darüber befinden sich bis zu acht DRAM Dies – der eigentliche Speicher. TSVs und Microbumps stellen die Verbindungen zu den einzelnen Ebenen her. Samsungs HBM-PIM sieht eine AI-Engine in jeder Speicherbank vor.

Im Vergleich zu bestehenden HBM2-Aquabolt-Lösungen sollen die AI-Engines die doppelte Leistung bei um 70 % reduzierter Leistungsaufnahme erreichen. Unklar ist allerdings, welche Vergleiche Samsung hier heranzieht. Laut Samsung soll HBM-PIM zu bestehenden Hardwarelösungen kompatibel sein.

Auf der International Solid-State Circuits Virtual Conference (ISSCC) am 22. Februar will Samsung weitere Details zum HBM-PIM verkünden. Mit einigen Partnern arbeiten Samsung bereits zusammen. In der zweiten Jahreshälfte 2021 erwartet man die Validierung der ersten Umsetzungen.

Update: Weitere Details

Doch etwas früher als gedacht sind nun weitere Details zum HBM-PIM bekannt geworden, die auch einige der noch offenen Fragen klären. TomsHardware hat einige Ausschnitte aus der Präsentation von Samsung, die Auskunft über die Funktionsweise des HBM-PIM geben.

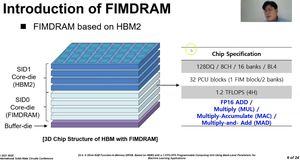

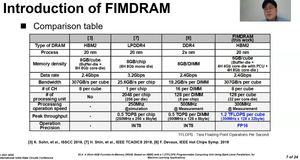

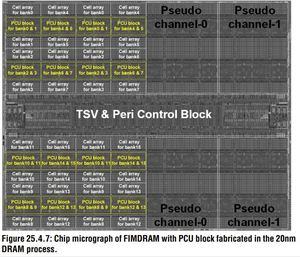

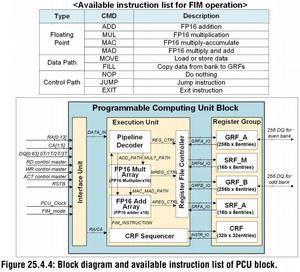

So verwendet Samsung für den HBM-PIM einen Puffer Die, vier Lagen des Speichers mitsamt der Recheneinheiten und weitere vier Lagen klassischen HBM-Speichers. In den FIMDRAM-Layern befinden sich jeweils 32 der Rechenkerne, die mit einem Takt von 300 MHz arbeiten. Diese können jeweils eine Fließkommaoperation mit 16 Bit ausführen. Die Rechenleistung eines kompletten Speicherchips mit vier FIMDRAM-Layern beträgt also 4 x 32 x 32 Byte x 300 MHz = 1,2 TFLOPS.

Die HBM-DIM-Speicherchips kommen allerdings nicht auf die gleiche Kapazität, wie die vergleichbaren reinen HBM-Chips. Samsung nennt eine Kapazität von 6 GB, da nur vier der acht Layer komplett aus Speicher bestehen und die weiteren vier FIMDRAM-Layer nur noch zur Hälfte, denn der Rest wird von den Recheneinheiten belegt.

Anders als zunächst vermutet nimmt Samsung im HBM-PIM nicht einfach nur ein AI-Speichermanagement vor, sondern bietet hier tatsächlich eine gewisse Rechenleistung. Zum Vergleich: Der A100 GPU-Beschleuniger von NVIDIA kommt auf eine Rechenleistung von 78 TFLOPS für FP16-Berechnungen. Mit den Tensor Cores und Sparsity sind es sogar 312 bzw. 624 TFLOPS. Der HBM-PIM spielt also nur für sehr spezielle Lösungen eine entscheidende Rolle. Wenn es nur auf die Rechenleistung ankommt, dürfte der Einsatz dieses Speichers wohl kaum einen Sinn machen.