News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

HBM

-

12-Layer HBM4: SK Hynix liefert die ersten Samples aus

Aktuell stürzt sich der Markt auf alles an HBM3(E)-Chips, was von den Herstellern ausgeliefert werden kann. Zusammen mit dem Packaging ist dies einer der größten Flaschenhälse in der Chipfertigung aktuell. Vor allem NVIDIA ist einer der größten Kunden – sowohl in der Fertigung als auch der Verarbeitung der Chips – sprich dem Packaging. SK Hynix hat nun angekündigt, dass man die ersten Samples eines HBM4 mit zwölf Layern an seine Kunden... [mehr]

Aktuell stürzt sich der Markt auf alles an HBM3(E)-Chips, was von den Herstellern ausgeliefert werden kann. Zusammen mit dem Packaging ist dies einer der größten Flaschenhälse in der Chipfertigung aktuell. Vor allem NVIDIA ist einer der größten Kunden – sowohl in der Fertigung als auch der Verarbeitung der Chips – sprich dem Packaging. SK Hynix hat nun angekündigt, dass man die ersten Samples eines HBM4 mit zwölf Layern an seine Kunden... [mehr] -

Known good dies: HBM soll strengeren Tests unterzogen werden

Dem High Bandwidth Memory oder kurz HBM kommt im Zusammenhang mit den KI-Beschleunigern derzeit eine extrem wichtige Bedeutung zu und gleichzeitig sind Engpässe in der Fertigung und dem Packaging noch immmer ein Flaschenhals. Sk Hynix gilt als einer der wichtigsten Zulieferer in diesem Bereich und ist damit für NVIDIA einer der wichtigsten Partner. Bei Samsung hat man offenbar Probleme in der Validierung bei NVIDIA, was immer wieder Thema in... [mehr]

Dem High Bandwidth Memory oder kurz HBM kommt im Zusammenhang mit den KI-Beschleunigern derzeit eine extrem wichtige Bedeutung zu und gleichzeitig sind Engpässe in der Fertigung und dem Packaging noch immmer ein Flaschenhals. Sk Hynix gilt als einer der wichtigsten Zulieferer in diesem Bereich und ist damit für NVIDIA einer der wichtigsten Partner. Bei Samsung hat man offenbar Probleme in der Validierung bei NVIDIA, was immer wieder Thema in... [mehr] -

Mehr GPU-Stapelspeicher: SanDisk stellt High Bandwidth Flash vor

Auf seinem Investor Day hat SanDisk Pläne zu einem neuen Speicher vorgestellt, der direkt auf dem Package mit GPUs und KI-Beschleunigern eingesetzt werden soll, aber eine deutlich höhere Kapazität als der bisher eingesetzter HBM bietet. Der High Bandwidth Flash (HBF) setzt dabei anstatt auf gestapelte DRAM-Chips wie bei HBM auf NAND-Flash, der auf viele parallele Zugriffe optimiert ist. Der große Vorteil von HBF: Ein einzelner Chip soll mit 16... [mehr]

Auf seinem Investor Day hat SanDisk Pläne zu einem neuen Speicher vorgestellt, der direkt auf dem Package mit GPUs und KI-Beschleunigern eingesetzt werden soll, aber eine deutlich höhere Kapazität als der bisher eingesetzter HBM bietet. Der High Bandwidth Flash (HBF) setzt dabei anstatt auf gestapelte DRAM-Chips wie bei HBM auf NAND-Flash, der auf viele parallele Zugriffe optimiert ist. Der große Vorteil von HBF: Ein einzelner Chip soll mit 16... [mehr] -

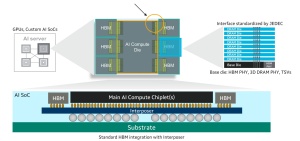

Schneller und weniger Chipfläche: Marvell präsentiert cHBM

Auf seinem Analyst Day 2024 hat Marvell eine Initiative vorgestellt, welche Custom-HBM-Chips für den Einsatz auf Beschleunigern vorsieht, sodass einige der Nachteile der Standard-Varianten beseitigt werden. Marvell hat zusammen mit Micron, Samsung und SK hynix, den drei großen HBM-Herstellern, an dieser Lösung gearbeitet. Nahezu alle KI- und HPC-Beschleuniger nutzen aktuell High Bandwidth Memory oder kurz HBM. Der aktuell verwendete... [mehr]

Auf seinem Analyst Day 2024 hat Marvell eine Initiative vorgestellt, welche Custom-HBM-Chips für den Einsatz auf Beschleunigern vorsieht, sodass einige der Nachteile der Standard-Varianten beseitigt werden. Marvell hat zusammen mit Micron, Samsung und SK hynix, den drei großen HBM-Herstellern, an dieser Lösung gearbeitet. Nahezu alle KI- und HPC-Beschleuniger nutzen aktuell High Bandwidth Memory oder kurz HBM. Der aktuell verwendete... [mehr] -

Azure HBv5: AMD und Microsoft haben EPYC-CPU mit HBM entwickelt

Microsoft hat auf der Ignite-Konferenz eine neue Cloud-Instanz namens Azure HBv5 vorgestellt, die auf einem neuen Custom-EPYC-Prozessoren basiert, den man gemeinsam mit AMD entwickelt hat. Der EPYC-Prozessor verwendet Zen-4-Kerne und kombiniert diese mit HBM3. Die VMs von Azura sollen damit auf Anwendungen ausgelegt sein, die auf eine besonders hohe Speicherbandbreite angewiesen sind, deren Datenmenge aber größer war, als der L3-Cache der... [mehr]

Microsoft hat auf der Ignite-Konferenz eine neue Cloud-Instanz namens Azure HBv5 vorgestellt, die auf einem neuen Custom-EPYC-Prozessoren basiert, den man gemeinsam mit AMD entwickelt hat. Der EPYC-Prozessor verwendet Zen-4-Kerne und kombiniert diese mit HBM3. Die VMs von Azura sollen damit auf Anwendungen ausgelegt sein, die auf eine besonders hohe Speicherbandbreite angewiesen sind, deren Datenmenge aber größer war, als der L3-Cache der... [mehr] -

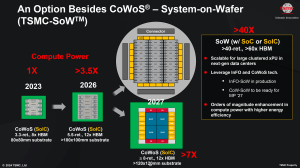

CoW-SoW: TSMC will komplette Systeme auf Wafern mit HBM fertigen

Bereits in der vergangenen Woche sind wir auf die zukünftigen Entwicklungen bei TSMC in der Fertigung eingegangen. So wird der weltweit größte Auftragsfertiger die rückseitige Versorgung bei den Chips erst mit der Fertigung in A16 in Produktion bringen und der 2-nm-Prozess soll durch NanoFlex effizienter werden. Doch es gibt auch Neuigkeiten aus anderen Bereichen. In den letzten zwei Jahren spielte vor allem das Packaging eine zunehmend... [mehr]

Bereits in der vergangenen Woche sind wir auf die zukünftigen Entwicklungen bei TSMC in der Fertigung eingegangen. So wird der weltweit größte Auftragsfertiger die rückseitige Versorgung bei den Chips erst mit der Fertigung in A16 in Produktion bringen und der 2-nm-Prozess soll durch NanoFlex effizienter werden. Doch es gibt auch Neuigkeiten aus anderen Bereichen. In den letzten zwei Jahren spielte vor allem das Packaging eine zunehmend... [mehr] -

Advanced Packaging für HBM: Sk hynix investiert fast vier Milliarden US-Dollar im US-Bundesstaat Indiana

Intel, Samsung, TSMC und nun auch Sk hynix. Der Südkoreanische Speicherhersteller will in West Lafayette im US-Bundesstaat Indiana fast vier Milliarden US-Dollar in eine Fabrik für Advanced Packaging sowie eine Forschungs- und Entwicklungsabteilung investieren. Die genaue Summe der Investition beläuft sich auf 3,87 Milliarden US-Dollar. Hauptsächlich soll hier das Packaging von High Bandwidth Memory oder kurz HBM stattfinden. Der... [mehr]

Intel, Samsung, TSMC und nun auch Sk hynix. Der Südkoreanische Speicherhersteller will in West Lafayette im US-Bundesstaat Indiana fast vier Milliarden US-Dollar in eine Fabrik für Advanced Packaging sowie eine Forschungs- und Entwicklungsabteilung investieren. Die genaue Summe der Investition beläuft sich auf 3,87 Milliarden US-Dollar. Hauptsächlich soll hier das Packaging von High Bandwidth Memory oder kurz HBM stattfinden. Der... [mehr] -

Zwei riesige Chips plus 12x HBM: Broadcom zeigt gigantisches Chip-Package

Riesige Chips sind bei Broadcom nichts neues. Mit dem Tomahawk 5 bietet man beispielsweise einen Switch-Chip für 64x 800GbE, 128x 400GbE oder 256x 200GbE, also insgesamt 51,2 TBit/s an und bedient damit die Anforderungen an schnelle Netzwerkverbindungen im Datacenter. Für schnelle Direktverbindungen in den Servern hat man mit Jericho-3 die entsprechenden Rack-Lösungen parat. Broadcom stellt aber auch Custom-Silicon her und zeigte nun... [mehr]

Riesige Chips sind bei Broadcom nichts neues. Mit dem Tomahawk 5 bietet man beispielsweise einen Switch-Chip für 64x 800GbE, 128x 400GbE oder 256x 200GbE, also insgesamt 51,2 TBit/s an und bedient damit die Anforderungen an schnelle Netzwerkverbindungen im Datacenter. Für schnelle Direktverbindungen in den Servern hat man mit Jericho-3 die entsprechenden Rack-Lösungen parat. Broadcom stellt aber auch Custom-Silicon her und zeigte nun... [mehr] -

465 Milliarden Megaprojekt: Grundsteinlegung im Frühjahr 2025

Anfang des Jahres wurde bekannt, dass sich in Südkorea ein riesigen Chip-Cluster in Planung befindet, in das bis 2047 bis zu 465 Milliarden US-Dollar investiert werden sollen. Insgesamt sollen 32 Chipwerke und fünf Forschungseinrichtungen entstehen. Nun sind die ersten Pläne bekanntgeworden, bzw. ältere Pläne von Sk hynix wurden erneut konkretisiert und mit einer Grundsteinlegung ist im März 2025 zu rechnen. Dies geht aus einem Bericht... [mehr]

Anfang des Jahres wurde bekannt, dass sich in Südkorea ein riesigen Chip-Cluster in Planung befindet, in das bis 2047 bis zu 465 Milliarden US-Dollar investiert werden sollen. Insgesamt sollen 32 Chipwerke und fünf Forschungseinrichtungen entstehen. Nun sind die ersten Pläne bekanntgeworden, bzw. ältere Pläne von Sk hynix wurden erneut konkretisiert und mit einer Grundsteinlegung ist im März 2025 zu rechnen. Dies geht aus einem Bericht... [mehr] -

2 TB/s über breiteres Speicherinterface: Samsung will HBM4 schon 2025 einführen

Auch wenn HBM (High Bandwidth Memory) bei Endkundenhardware kaum mehr eine Rolle spielt, so ist dieser schnelle Speichertyp aus dem Datacenter und hier der Beschleunigerhardware kaum mehr wegzudenken. Entsprechend schritt die Entwicklung in den vergangenen 24 Monaten schnell voran. Nachdem die ersten Beschleuniger mit HBM3 in diesem Jahr ausgeliefert wurden und werden sollen, soll im kommenden Jahr bereits HBM3E zum Einsatz kommen. In der unten... [mehr]

Auch wenn HBM (High Bandwidth Memory) bei Endkundenhardware kaum mehr eine Rolle spielt, so ist dieser schnelle Speichertyp aus dem Datacenter und hier der Beschleunigerhardware kaum mehr wegzudenken. Entsprechend schritt die Entwicklung in den vergangenen 24 Monaten schnell voran. Nachdem die ersten Beschleuniger mit HBM3 in diesem Jahr ausgeliefert wurden und werden sollen, soll im kommenden Jahr bereits HBM3E zum Einsatz kommen. In der unten... [mehr] -

Sk hynix und Samsung: Speicher mit In-Memory-AI wird konkreter

Sk hynix und Samsung arbeiten bereits seit geraumer Zeit daran, den Speicher und den AI-Beschleuniger dichter zusammen zu bringen. Bei Sk hynix nennt sich die entsprechende Technologie AiM (Accelerator in Memory), bei Samsung Processing-in-Memory (PIM). Beide Ansätze sind nicht neu, rücken auf der diesjährigen HotChips 2023 aber näher an einen möglichen Praxiseinsatz. So sieht Sk hynix zu einem GDDR6-AiM einen Prototypen vor,... [mehr]

Sk hynix und Samsung arbeiten bereits seit geraumer Zeit daran, den Speicher und den AI-Beschleuniger dichter zusammen zu bringen. Bei Sk hynix nennt sich die entsprechende Technologie AiM (Accelerator in Memory), bei Samsung Processing-in-Memory (PIM). Beide Ansätze sind nicht neu, rücken auf der diesjährigen HotChips 2023 aber näher an einen möglichen Praxiseinsatz. So sieht Sk hynix zu einem GDDR6-AiM einen Prototypen vor,... [mehr] -

HBM4 von Sk hynix: 2026 soll es mit 32 GB losgehen

Aktuell werden die ersten AI-Beschleuniger mit HBM3 bestückt. Dazu gehören NVIDIAs H100, aber auch der Radeon Instinct MI300A und MI300X von AMD. Lieferanten des schnellen Speichers sind Samsung und Sk hynix – beides in Südkorea ansässige Unternehmen. Laut BusinessKorea hat Sk hynix auf einem Investoren-Event seine Bestrebungen bestätigt, diesen Speicherbereich in diesem und dem kommenden Jahr weiter auszubauen. Zwar macht der HBM... [mehr]

Aktuell werden die ersten AI-Beschleuniger mit HBM3 bestückt. Dazu gehören NVIDIAs H100, aber auch der Radeon Instinct MI300A und MI300X von AMD. Lieferanten des schnellen Speichers sind Samsung und Sk hynix – beides in Südkorea ansässige Unternehmen. Laut BusinessKorea hat Sk hynix auf einem Investoren-Event seine Bestrebungen bestätigt, diesen Speicherbereich in diesem und dem kommenden Jahr weiter auszubauen. Zwar macht der HBM... [mehr] -

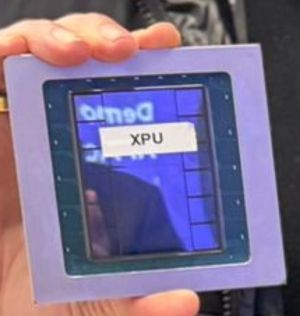

Nach vielen Verspätungen nun offiziell: Sapphire Rapids kommt mit vielen Beschleunigern

Heute ist es so weit. Die vierte Xeon-Generation alias Sapphire Rapids geht offiziell an den Start. Ursprünglich im Mai 2019 angekündigt und für 2021 vorgesehen, feiert die neue Xeon-Generation keinen "harten" Start, sondern wird fließend in den kommenden Wochen und Monaten ihren Weg in den Markt finden. Ihre Basis bilden Golden-Cove-Kerne, die in Intel 7 gefertigt werden und vielen Neuerungen bieten. Wir werden alles... [mehr]

Heute ist es so weit. Die vierte Xeon-Generation alias Sapphire Rapids geht offiziell an den Start. Ursprünglich im Mai 2019 angekündigt und für 2021 vorgesehen, feiert die neue Xeon-Generation keinen "harten" Start, sondern wird fließend in den kommenden Wochen und Monaten ihren Weg in den Markt finden. Ihre Basis bilden Golden-Cove-Kerne, die in Intel 7 gefertigt werden und vielen Neuerungen bieten. Wir werden alles... [mehr] -

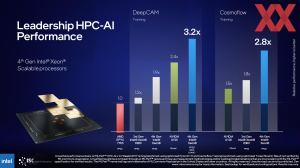

Intel nennt weitere Leistungsdaten zu Sapphire Rapids HBM und Ponte Vecchio

In der gestrigen Keynote stellte Intel den Nachfolger des Ponte-Vecchio-Beschleuniger Rialto Bridge offiziell vor. Mit 160 Xe-Cores ausgestattet, fokussiert sich Intel hier in Form eines Ticks vor allem auf moderate Verbesserungen – auch wenn wir potentiell von 30+ % sprechen. Auf dem Stand und auch als Teil der Keynote veröffentlichte Intel einige neue Benchmarks zu Sapphire Rapids, der nächsten Xeon-Generation, mit HBM und auch erstmals... [mehr]

In der gestrigen Keynote stellte Intel den Nachfolger des Ponte-Vecchio-Beschleuniger Rialto Bridge offiziell vor. Mit 160 Xe-Cores ausgestattet, fokussiert sich Intel hier in Form eines Ticks vor allem auf moderate Verbesserungen – auch wenn wir potentiell von 30+ % sprechen. Auf dem Stand und auch als Teil der Keynote veröffentlichte Intel einige neue Benchmarks zu Sapphire Rapids, der nächsten Xeon-Generation, mit HBM und auch erstmals... [mehr] -

Offiziell: Sapphire Rapids bekommt HBM-Speicher und Xe-HPC-Formfaktoren (Update)

Auf der ISC High Performance gibt Intel weitere Details zu den zukünftigen HPC-Hardware-Lösungen bekannt. So bestätigt Intel unter anderem, dass die vierte Generation der Xeon-Prozessoren ebenfalls mit High Bandwidth Memory bestückt werden wird. Genauer gesagt wird es Modelle geben, die HBM verwenden werden und solche, bei denen dies nicht der Fall sein wird. Intel dürfte damit auf den Trend zu immer größeren Caches reagieren, den AMD... [mehr]

Auf der ISC High Performance gibt Intel weitere Details zu den zukünftigen HPC-Hardware-Lösungen bekannt. So bestätigt Intel unter anderem, dass die vierte Generation der Xeon-Prozessoren ebenfalls mit High Bandwidth Memory bestückt werden wird. Genauer gesagt wird es Modelle geben, die HBM verwenden werden und solche, bei denen dies nicht der Fall sein wird. Intel dürfte damit auf den Trend zu immer größeren Caches reagieren, den AMD... [mehr] -

Samsung I-Cube4: Chiplets auf dünnem Interposer werden effizienter

Nachdem IBM heute den ersten im 2-nm-Prozess gefertigten Chip angekündigt hat, folgt eine weitere Ankündigung aus der Halbleiterfertigung. Samsung kündigt mit Interposer-Cube4 (I-Cube4) die nächste Generation der 2.5D-Integration für die Kombination verschiedener Chiplets auf einem Package an. Im Vergleich zu I-Cube2 hat Samsung vor allem einige Änderungen in der Interposer-Technik vorgenommen. Die I-Cube-IP von... [mehr]

Nachdem IBM heute den ersten im 2-nm-Prozess gefertigten Chip angekündigt hat, folgt eine weitere Ankündigung aus der Halbleiterfertigung. Samsung kündigt mit Interposer-Cube4 (I-Cube4) die nächste Generation der 2.5D-Integration für die Kombination verschiedener Chiplets auf einem Package an. Im Vergleich zu I-Cube2 hat Samsung vor allem einige Änderungen in der Interposer-Technik vorgenommen. Die I-Cube-IP von... [mehr] -

Samsung HBM-PIM: Schneller Speicher bekommt eingebaute AI-Engine (Update)

Samsung hat eine neue Art High Bandwidth Memory (HBM) vorgestellt, der nicht nur ein einfacher Speicher ist, sondern der eine Processing-in-Memory (PIM) Architektur enthält. Es handelt sich laut Samsung um den ersten HBM, der über eine solche Art der integrierten Recheneinheiten verfügt. Noch ist nicht bekannt, wie genau die integrierten Recheneinheiten funktionieren, bzw. welche Rechenleistung diese erreichen. Samsung nennt keinerlei... [mehr]

Samsung hat eine neue Art High Bandwidth Memory (HBM) vorgestellt, der nicht nur ein einfacher Speicher ist, sondern der eine Processing-in-Memory (PIM) Architektur enthält. Es handelt sich laut Samsung um den ersten HBM, der über eine solche Art der integrierten Recheneinheiten verfügt. Noch ist nicht bekannt, wie genau die integrierten Recheneinheiten funktionieren, bzw. welche Rechenleistung diese erreichen. Samsung nennt keinerlei... [mehr] -

CoWoS: TSMCs 1.700-mm²-Interposer nimmt 5-nm-Chips auf

TSMC hat gemeinsam mit Broadcom die eigenen Interposer- und Interconnect-Technologie CoWoS (Chip-on-Wafer-on-Substrate) in die Produktionsreife gebracht und wird in dieser Zusammenarbeit wohl bald konkrete Produkte ankündigen. Die Besonderheit in der Zusammenarbeit liegt in der Größe des gemeinsam entwickelten Interposers. Dieser kommt auf eine Fläche von 1.700 mm² und soll neben in 5 nm (N5) gefertigten Chips schnellen HBM... [mehr]

TSMC hat gemeinsam mit Broadcom die eigenen Interposer- und Interconnect-Technologie CoWoS (Chip-on-Wafer-on-Substrate) in die Produktionsreife gebracht und wird in dieser Zusammenarbeit wohl bald konkrete Produkte ankündigen. Die Besonderheit in der Zusammenarbeit liegt in der Größe des gemeinsam entwickelten Interposers. Dieser kommt auf eine Fläche von 1.700 mm² und soll neben in 5 nm (N5) gefertigten Chips schnellen HBM... [mehr] -

Für 3DS DRAM und HBM: SK Hynix lizensiert DBI Ultra Interconnect

Der zunehmende Bedarf an 2,5- und 3D-Packaging-Technologien geht an SK Hynix nicht vorbei. Dazu hat man sich nun bei der Xperi Corporation bedient und mit dem eher unbekannten Technologie-Unternehmen ein Lizenzabkommen geschlossen, welches die DBI Ultra getaufte Interconnect-Technik umfasst. Entwickelt wurde die Technik jedoch nicht von Xperi selbst, sondern von Invensas. DBI Ultra soll es ermöglichen, bis zu 16 Speicherlayer... [mehr]

Der zunehmende Bedarf an 2,5- und 3D-Packaging-Technologien geht an SK Hynix nicht vorbei. Dazu hat man sich nun bei der Xperi Corporation bedient und mit dem eher unbekannten Technologie-Unternehmen ein Lizenzabkommen geschlossen, welches die DBI Ultra getaufte Interconnect-Technik umfasst. Entwickelt wurde die Technik jedoch nicht von Xperi selbst, sondern von Invensas. DBI Ultra soll es ermöglichen, bis zu 16 Speicherlayer... [mehr] -

JEDEC spezifiziert HBM2-Standard auf bis zu 3,2 GBit/s

Die Entwicklung des High Bandwidth Memory ist in den vergangenen Jahres ins Stocken geraten. Einige Versuche, den Speicherstandard in das Consumer-Segment zu bringen, allen voran durch AMD (Radeon R9 Fury X, Radeon RX Vega 56 und 64 und die Radeon VII), haben nicht die Durchdringung erreicht, die durch die Hersteller erwartet wurde. Stattdessen verblieb HBM ein Speicherstandard für Datacenter-Anwendungen und einige... [mehr]

Die Entwicklung des High Bandwidth Memory ist in den vergangenen Jahres ins Stocken geraten. Einige Versuche, den Speicherstandard in das Consumer-Segment zu bringen, allen voran durch AMD (Radeon R9 Fury X, Radeon RX Vega 56 und 64 und die Radeon VII), haben nicht die Durchdringung erreicht, die durch die Hersteller erwartet wurde. Stattdessen verblieb HBM ein Speicherstandard für Datacenter-Anwendungen und einige... [mehr] -

SK Hynix stellt schnellsten HBM2E mit 460 GB/s und 16 GB vor

SK Hynix hat eine neue HBM-Speichervariante vorgestellt, die ab 2020 im Zusammenspiel mit zahlreichen Beschleunigern jeglicher Art zum Einsatz kommen soll. HBM2E ist als Übergangsvariante bis zur dritten Generation des High Bandwidth Memory angedacht, denn die Entwicklungskurve bei der HBM-Speichertechnologie ist etwas abgeflacht und hat sich nicht derart entwickelt, wie dies noch vor wenigen Jahren prognostiziert wurde. Bereits im... [mehr]

SK Hynix hat eine neue HBM-Speichervariante vorgestellt, die ab 2020 im Zusammenspiel mit zahlreichen Beschleunigern jeglicher Art zum Einsatz kommen soll. HBM2E ist als Übergangsvariante bis zur dritten Generation des High Bandwidth Memory angedacht, denn die Entwicklungskurve bei der HBM-Speichertechnologie ist etwas abgeflacht und hat sich nicht derart entwickelt, wie dies noch vor wenigen Jahren prognostiziert wurde. Bereits im... [mehr] -

PCIe 5.0, HBM und Transceiver: Intel noch 2019 mit ersten Agilex-FPGAs

Neben den neuen Xeon-Prozessoren (Xeon D-1600 und Xeon Scalable der 2. Generation) stellt Intel auch neue Hardware in anderen Bereichen vor. Seit einigen Jahren arbeitet Intel hier unter dem Codenamen Falcon Mesa ein einem FPGA-Design, welches die aktuelle Produktstrategie von Intel wohl sehr gut repräsentiert. Über alle Präsentationen und Vorstellungen der jüngeren Vergangenheit hinweg wird deutlich, dass der Chipgigant... [mehr]

Neben den neuen Xeon-Prozessoren (Xeon D-1600 und Xeon Scalable der 2. Generation) stellt Intel auch neue Hardware in anderen Bereichen vor. Seit einigen Jahren arbeitet Intel hier unter dem Codenamen Falcon Mesa ein einem FPGA-Design, welches die aktuelle Produktstrategie von Intel wohl sehr gut repräsentiert. Über alle Präsentationen und Vorstellungen der jüngeren Vergangenheit hinweg wird deutlich, dass der Chipgigant... [mehr] -

JEDEC spezifiziert HBM mit 12 Speicherlayern und 24 GB pro Chip

High Bandwidth Memory ist der Speicher der Wahl, wenn die Anbindung des Speichers eine entscheidende Rolle spielt. Die Speicherbandbreite über jeweils ein 1.024 Bit breites Speicherinterface pro HBM-Chip erreicht hier bis zu 1 TB/s, während mit GDDR6 und einem 384 Bit breitem Speicherinterface bei den aktuellen Workstation-Lösungen bis zu 672 GB/s erreicht werden. HBM der zweiten Generation erreicht derzeit eine Kapazität von 8 GB pro... [mehr]

High Bandwidth Memory ist der Speicher der Wahl, wenn die Anbindung des Speichers eine entscheidende Rolle spielt. Die Speicherbandbreite über jeweils ein 1.024 Bit breites Speicherinterface pro HBM-Chip erreicht hier bis zu 1 TB/s, während mit GDDR6 und einem 384 Bit breitem Speicherinterface bei den aktuellen Workstation-Lösungen bis zu 672 GB/s erreicht werden. HBM der zweiten Generation erreicht derzeit eine Kapazität von 8 GB pro... [mehr] -

Zweite Generation HBM2 von SK Hynix und Samsung sind kein Kompromiss mehr

Vor etwa zwei Jahren begannen Samsung und SK Hynix mit der Risc-Production von High Bandwidth Memory der zweiten Generation. Seit Sommer wird dieser in der Massenfertigung produziert und NVIDIA verbaut diesen auf der Tesla P100, Quadro GP100, Tesla V100 und Titan V. Im Endkunden-Bereich ist AMD mit der Radeon RX Vega 56 und 64 der bisher einzige Abnehmer. Vor einigen Wochen kündigte Samsung die 2. Generation des HBM2 namens... [mehr]

Vor etwa zwei Jahren begannen Samsung und SK Hynix mit der Risc-Production von High Bandwidth Memory der zweiten Generation. Seit Sommer wird dieser in der Massenfertigung produziert und NVIDIA verbaut diesen auf der Tesla P100, Quadro GP100, Tesla V100 und Titan V. Im Endkunden-Bereich ist AMD mit der Radeon RX Vega 56 und 64 der bisher einzige Abnehmer. Vor einigen Wochen kündigte Samsung die 2. Generation des HBM2 namens... [mehr] -

NVIDIA präsentiert Drive PX Pegasus: 2x Xavier SoC + 2x Next-Gen GPU für 320 TFLOPS

Auf der Keynote der GTC Europe in München hat NVIDIA ein neues Compute-Modul für den Automotive-Bereich vorgestellt. Das Drive PX Modul namens Pegasus verwendet dabei bis zu zwei Xavier-SoCs und zwei dedizierte GPUs auf Basis der nächsten Grafik-Architektur, die bisher noch keinen Namen hat. Drive PX Pegasus soll dabei die Rechenleistung für das Level 5 des autonomen Fahrens, und ist zusätzlich als ASIL D (Automotive Safety Integrity Level D),... [mehr]

Auf der Keynote der GTC Europe in München hat NVIDIA ein neues Compute-Modul für den Automotive-Bereich vorgestellt. Das Drive PX Modul namens Pegasus verwendet dabei bis zu zwei Xavier-SoCs und zwei dedizierte GPUs auf Basis der nächsten Grafik-Architektur, die bisher noch keinen Namen hat. Drive PX Pegasus soll dabei die Rechenleistung für das Level 5 des autonomen Fahrens, und ist zusätzlich als ASIL D (Automotive Safety Integrity Level D),... [mehr] -

AMD Vega: HBM2 von SK Hynix mit nur 4 GB und 204,8 GB/s pro Chip

SK Hynix hat seinen Produktkatalog für die nächsten Quartale aktualisiert und führt dort neben neuem 3D-NAND v5 mit 50 GBit/s und LPDDR4X auch sein aktuelles Angebot an High Bandwidth Memory der 2. Generation auf. SK Hynix war enger Partner von AMD für die Entwicklung von HBM. Als erster Grafikkarten-Hersteller setzte AMD mit der Radeon-R9-Fury-Serie auf die 1. Generation des schnellen Speichers und öffnete damit der aktuellen Entwicklung Tür... [mehr]

SK Hynix hat seinen Produktkatalog für die nächsten Quartale aktualisiert und führt dort neben neuem 3D-NAND v5 mit 50 GBit/s und LPDDR4X auch sein aktuelles Angebot an High Bandwidth Memory der 2. Generation auf. SK Hynix war enger Partner von AMD für die Entwicklung von HBM. Als erster Grafikkarten-Hersteller setzte AMD mit der Radeon-R9-Fury-Serie auf die 1. Generation des schnellen Speichers und öffnete damit der aktuellen Entwicklung Tür... [mehr] -

AMDs Vega 10 mit HBM2 soll doch noch in diesem Jahr erscheinen – nur für den professionellen Bereich

Wenn AMD eines inzwischen klar kommuniziert hat, dann die Tatsache, dass wir in diesem Jahr keine High-End-Grafikkarten mit Vega-GPU mehr sehen werden. Allerdings sollten wir dabei zumindest eine Einschränkung machen, denn Raja Koduri, Chef der Radeon Technologies Group, sprach zuletzt dennoch von interessanten Neuerscheinungen, ohne dabei konkreter zu werden. Zuletzt tauchten auch einige technischen Daten zu den verschiedenen GPUs wie Vega 10,... [mehr]

Wenn AMD eines inzwischen klar kommuniziert hat, dann die Tatsache, dass wir in diesem Jahr keine High-End-Grafikkarten mit Vega-GPU mehr sehen werden. Allerdings sollten wir dabei zumindest eine Einschränkung machen, denn Raja Koduri, Chef der Radeon Technologies Group, sprach zuletzt dennoch von interessanten Neuerscheinungen, ohne dabei konkreter zu werden. Zuletzt tauchten auch einige technischen Daten zu den verschiedenen GPUs wie Vega 10,... [mehr] -

Preis der Radeon R9 Fury X fällt auf 399 Euro

Unter High-End wird bei den Grafikkarten schon längst keine solche für einen Preis von unter 400 Euro verstanden. Die vor mehr als einem Jahr vorgestellte AMD Radeon R9 Fury, noch immer das High-End-Modell mit Fiji-GPU und High Bandwidth Memory der ersten Generation, ist ab sofort für 399 Euro zu haben. Dieser Preisverfall ist allerdings keine neue Entwicklung, sondern deutete sich über die vergangenen Wochen und Monate an. Derzeit bieten... [mehr]

Unter High-End wird bei den Grafikkarten schon längst keine solche für einen Preis von unter 400 Euro verstanden. Die vor mehr als einem Jahr vorgestellte AMD Radeon R9 Fury, noch immer das High-End-Modell mit Fiji-GPU und High Bandwidth Memory der ersten Generation, ist ab sofort für 399 Euro zu haben. Dieser Preisverfall ist allerdings keine neue Entwicklung, sondern deutete sich über die vergangenen Wochen und Monate an. Derzeit bieten... [mehr] -

NVIDIA veröffentlicht Die-Shot zur GP100-GPU

Bei der Präsentation neuer Hardware und vor allem neuer Chips durch Hersteller wie AMD, NVIDIA oder Intel ist in den vergangenen Jahren vor allem eines auffällig: Nicht immer reden die Hersteller gerne über jedes Detail der Entwicklung und ungern wird Journalisten oder der Konkurrenz die Möglichkeit geboten, sich diese Details selbst zu erarbeiten. So wurden die beliebten Die-Shots von CPUs und GPUs in jüngster Vergangenheit lieber gegen ein... [mehr]

Bei der Präsentation neuer Hardware und vor allem neuer Chips durch Hersteller wie AMD, NVIDIA oder Intel ist in den vergangenen Jahren vor allem eines auffällig: Nicht immer reden die Hersteller gerne über jedes Detail der Entwicklung und ungern wird Journalisten oder der Konkurrenz die Möglichkeit geboten, sich diese Details selbst zu erarbeiten. So wurden die beliebten Die-Shots von CPUs und GPUs in jüngster Vergangenheit lieber gegen ein... [mehr]