Werbung

Erst kürzlich veröffentlichte die JEDEC die Spezifikationen für High Bandwidth Memory der 2. Generation für einen maximalen Speicherausbau von 32 GB bei einer Speicherbandbreite von bis zu 1.024 GB pro Sekunde. Doch auch HBM2 wird noch einige Zeit den High-End-Grafikkarten vorbehalten bleiben und so wird uns GDDR5-Speicher noch eine Weile begleiten. Bereits im vergangenen Jahr hat die JEDEC auch den von Micron vorangetriebenen GDDR5X-Speicher genauer ausgeführt. Da es mehr als wahrscheinlich ist, dass uns dieser im Jahr 2016 auf einigen Karten erwarten wird, schauen wir uns die technischen Daten zu GDDR5X einmal etwas genauer an.

Zunächst einmal schaute es danach aus, als seien sich GDDR5 und GDDR5X sehr ähnlich - dem ist auch so. Allerdings gibt es einige Einschränkungen. So verfügen die GDDR5-Speicherchips über 190 anstatt 170 Kontakte im BGA. So einfach können die Hersteller damit nicht von GDDR5 auf GDDR5X wechseln. Die Abmessungen der Speicherchips spielen mit 14 x 10 mm wohl kaum eine Rolle.

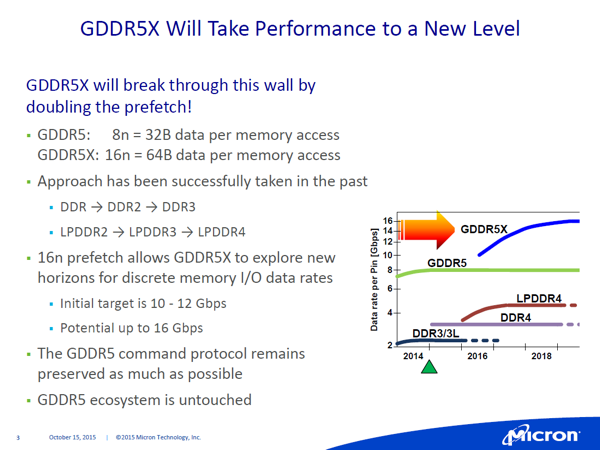

Wohl größter Unterschied zwischen GDDR5 und GDDR5X ist der doppelt so große Prefetch bei den Speicherzugriffen von acht auf 16 Datenwörtern. Am Takt der Speicherchips tut sich mit 1.250 bis 2.000 MHz hingegen wenig. Durch die Erhöhung des Prefetch ist der Speichercontroller selbst aber theoretisch doppelt so schnell und macht damit eine höhere Speicherdichte der Chips möglich. Pro Chip kommt weiterhin ein 32 Bit breiter Controller zum Einsatz, was 2 GB pro Speicherchip möglich macht. Da immer ein Zusammenhang zwischen Breite des Speichercontrollers und Speicherausbau besteht, ändern sich die theoretisch möglichen Kennzahlen. Ein 256 Bit breites Speicherinterface kann damit theoretisch 16 GB an GDDR5X-Speicher ansprechen. Bei 384 Bit (NVIDIA GM200) und 512 Bit (AMD Hawaii) wären sogar 24 oder sogar 32 GB möglich.

Briefing von Micron zu GDDR5X

Die Datenraten pro Speicherchip liegen aktuell bei 8 GBit/s bei GDDR5-Varianten mit 2.000 MHz. Micron arbeitet in der aktuellen Ausführung von GDDR5X mit 10 bis 12 GBit/s, plant aber mit bis zu 16 GBit/s. Laut Micron sorgen die geringen Unterschiede zwischen GDDR5 und GDDR5X dafür, dass nur wenige Änderungen beim Design der Speichercontroller vorgenommen werden müssen, was AMD und NVIDIA sicherlich entgegen kommt.

Ein paar Rechenbeispiele dazu: Besitzt eine GPU aktuell ein Speicherinterface mit 256 Bit, so steigert der Einsatz von GDDR5X bei 12 GBit/s die Speicherbandbreite von 256 auf 384 GB/s (bei einem angenommenen Chiptakt von 2.000 MHz). Bei 16 GBit/s wäre sogar eine Verdopplung auf 512 GB/s möglich und damit läge man schon auf Niveau der aktuellen HBM-Generation. An dieser Stelle muss aber auch erwähnt werden, dass ein GDDR5X mit 16 GBit/s derzeit noch nicht realisierbar ist.

Allerdings sind dies zunächst einmal nur theoretische Werte, denn in der Spezifikationen ins solche extremen Beispiele nicht erwähnt. Hier sind folgende Standardkonfigurationen erwähnt:

- 4 Gb = 128 Mb x 32 ( 8 Mb x 32 x 16 banks) / 256 Mb x 16 (16 Mb x 16 x 16 banks)

- 6 Gb = 192 Mb x 32 (12 Mb x 32 x 16 banks) / 384 Mb x 16 (24 Mb x 16 x 16 banks)

- 8 Gb = 256 Mb x 32 (16 Mb x 32 x 16 banks) / 512 Mb x 16 (32 Mb x 16 x 16 banks)

- 12 Gb = 384 Mb x 32 (24 Mb x 32 x 16 banks) / 768 Mb x 16 (48 Mb x 16 x 16 banks)

- 16 Gb = 512 Mb x 32 (32 Mb x 32 x 16 banks) / 1 Gb x 16 (64 Mb x 16 x 16 banks)

In den Spezifikationen werden auch noch folgende Funktionen des GDDR5X erwähnt:

- Single ended interface for command, address and data

- Differential clock input CK_t/CK_c for ADD/CMD

- Two differential clock inputs WCK_t/WCK_c, each associated with two data bytes (DQ, DBI_n, EDC) Single Data Rate (SDR) commands (CK)

- Double Data Rate (DDR) addresses (CK)

- QDR and DDR operating modes: • QDR mode: Quad Data Rate (QDR) data (WCK); 16n prefetch architecture with 512 bit per array read or write access; burst length 16 • DDR mode: Double Data Rate (DDR) data (WCK); 8n prefetch architecture with 256 bit per array read or write access; burst length 8

- 16 internal banks

- 4bankgroupsfortCCDL =3tCK and4tCK

- Programmable read latency: 5 to 36 tCK; programmable write latency: 1 to 7 tCK

- Write data mask function via address bus (single/double/quad byte mask)

- Data bus inversion (DBI) & address bus inversion (ABI)

- Input/output PLL/DLL

- Address training: address input monitoring via DQ/DBI_n/EDC pins

- WCK2CK clock training with phase information via EDC pins

- Data read and write training via READ FIFO (depth = 6)

- Read FIFO pattern preload by LDFF command

- Direct write data load to READ FIFO via WRTR command

- Consecutive read of READ FIFO via RDTR command

- Read/write EDC on/off mode

- Programmable EDC hold pattern for CDR

- Read/write data transmission integrity secured by cyclic redundancy check (CRC-8) Programmable CRC read latency = 1 to 4 tCK; programmable CRC write

- latency = 7 to 14 tCK Low Power modes

- RDQS mode on EDC pins

- On-chip temperature sensor with read-out

- Auto & self refresh modes

- Auto precharge option for each burst access

- Temperature sensor controlled self refresh rate

- Optional digital tRAS lockout

- On-die termination (ODT) for all high-speed inputs

- Pseudo open drain (POD-135) compatible outputs

- ODT and output driver strength auto-calibration with external resistor ZQ pin (120 ?) Programmable termination and driver strength offsets

- Internal VREF for data inputs with programmable levels

- Selectable external or internal VREF for address / command inputs

- Vendor ID for device identification

- Mirror function with MF pin

- IEEE 1149.1 compliant boundary scan

- 1.35 V supply voltage for device operation (VDD) and I/O interface (VDDQ)

- 1.8 V pump voltage (VPP)

- 190 ball BGA package

Aktuell gibt es noch keine Angaben darüber, welcher Hersteller, ob nun AMD oder NVIDIA auf GDDR5X von Micron setzen werden und welche Auswirkungen dies haben wird.