Werbung

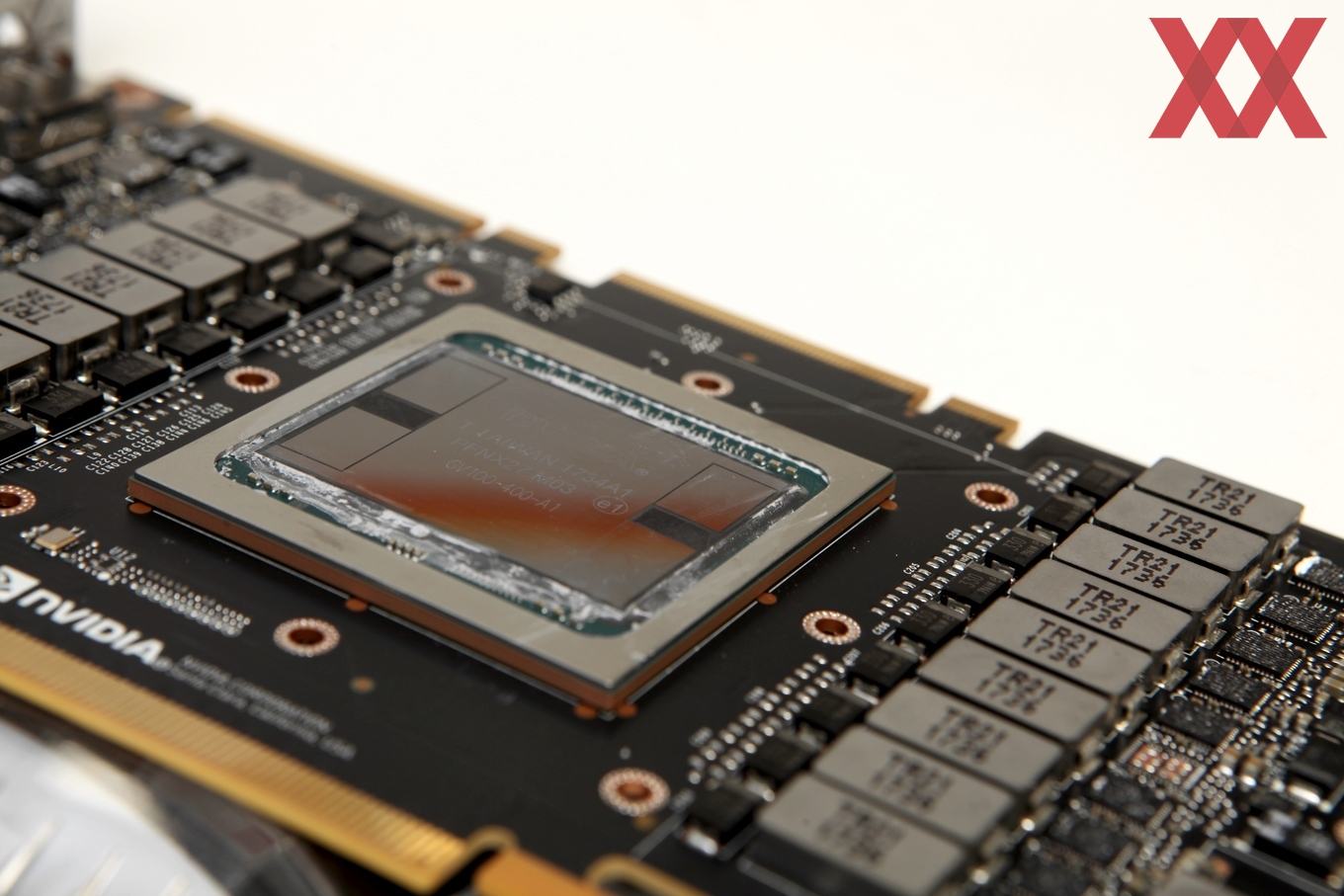

High Bandwidth Memory ist der Speicher der Wahl, wenn die Anbindung des Speichers eine entscheidende Rolle spielt. Die Speicherbandbreite über jeweils ein 1.024 Bit breites Speicherinterface pro HBM-Chip erreicht hier bis zu 1 TB/s, während mit GDDR6 und einem 384 Bit breitem Speicherinterface bei den aktuellen Workstation-Lösungen bis zu 672 GB/s erreicht werden.

HBM der zweiten Generation erreicht derzeit eine Kapazität von 8 GB pro HBM-Speicherchip. Dazu werden neun Layer verwendet – ein I/O-Die und acht Speicher-Dies (diese mit jeweils 1 GB pro Layer). Bei einer derzeit maximalen Anbindung von vier dieser Chips über jeweils 1.024 Bit ist derzeit eine Kapazität von bis zu 32 GB möglich. Diese 32 GB sind für einige Anwendungen zu wenig und so wurde bereits länger über eine Erweiterung des JEDEC-Standards für HBM nachgedacht. Als JESD235B ist dieser nun veröffentlicht worden.

Der Standard JESD235B sieht nun sogenannte 12-High-Stacks vor. Dabei bestehen die Chips aus zwölf Speicher-Dies und einem I/O-Die und kommen damit insgesamt auf 13 Layer. Hinzu kommt eine Datendichte von bis zu 2 GB pro Layer. Damit lassen sich Speicherkapazitäten von 24 GB pro HBM-Speicherchip realisieren. Die Pressemitteilung der JEDEC spricht davon, dass Hardware die auf einen solchen Speicher setzt nun einen Speicherausbau von bis zu 24 GB umsetzen könnte. Üblicherweise werden zwei oder vier HBM-Speicherstacks an eine GPU angebunden. Bei bis zu 24 GB pro HBM-Speicherchip wären damit nicht mehr wie aktuell "nur" bis zu 32 GB möglich, sondern satte 96 GB.

Ein einzelner HBM-Speicherchip kommt auf eine Datenrate von 307,2 GB/s. Bei vier Speicherchips sprechen wir also von einer Gesamtspeicherbandbreite von 1,2 TB/s. Diese Geschwindigkeiten werden aktuell bereits mit HBM2-Speicher erreicht. Allerdings nicht bei Speicher mit 12-Speicherlayern und einer Kapazität von 2 GB pro Layer.

Um die höhere Bandbreite zu erreichen, ist für das schnellere HBM2 das TSV-Design (Through Silicon Via’s) verbessert worden. Die TSVs kommen zur Verbindung der einzelnen Speicherdies und dem I/O-Die zum Einsatz. Jeder der Layer ist mit dem darüber- und darunterliegenden Layer über mehr als 5.000 TSVs verbunden. Entsprechend komplex ist die Fertigung von HBM – speziell mit mehr und mehr Layern. Um die Abwärme zwischen den Layern abführen zu können, werden Thermal Bumbs zwischen den einzelnen Schichten eingesetzt.

Die JEDEC veröffentlicht keinerlei Informationen über Verfügbarkeit oder konkreten Einsatz des HBM mit größerer Kapazität. Keiner der HBM-Hersteller hat sich bisher zu Speichervarianten mit mehr als acht Speicherlayern geäußert.