Werbung

Zur Supercomputing 2019 stellt Intel seine groben Hardwarestrukturen für 2021 vor. Sowohl im Bereich der Prozessoren, als auch bei den General Purpose GPUs gibt es neue Details zu berichten. Aber wie gesagt, wir sprechen hier von 2021, also bis wir konkrete Hardware sehen, wird es noch mehr als 12 Monate dauern. Für Endkunden bleiben damit viele Fragen offen.

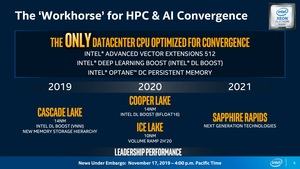

Auf Seiten der Xeon-Prozessoren nennt Intel den bereits bekannten Zeitplan. 2020 sollen demnach die Xeon-Prozessoren auf Basis von Cooper Lake erscheinen, die sich vor allem im Hinblick auf die Unterstützung von DL-Boost und hier vor allem von Bfloat16 hervortun. Cooper Lake wird die einzige Architektur sein, die Bfloat16 in dieser Form unterstützen wird. Abseits davon bleibt dies einigen AI-Beschleunigern vorbehalten. Die Xeon-Prozessoren auf Basis von Cooper Lake werden weiterhin in 14 nm gefertigt werde. Daneben hat Intel bisher nur bestätigt, dass diese Prozessoren bis zu 56 Kerne bieten werden.

Parallel dazu wird Intel ab der zweiten Jahreshälfte die in 10 nm gefertigten Xeon-Prozessoren auf Basis von Ice Lake anbieten. Auch hier spielt DL-Boost eine Rolle, allerdings gehört Bfloat16 nicht zu den unterstützen Befehlssätzen. Ob und in welcher Form Intel die Sunny-Cove-Kerne sinnvoll im Serverumfeld einsetzen kann, ist eine der großen Fragen.

Für 2021 ist dann Sapphire Rapids geplant. Auf welche Kerne Intel hier setzt und in welcher Fertigungsgröße diese hergestellt werden, sind nur die wichtigsten Fragen. Auf dem Memory Technology Day wurde zumindest etwas zur Unterstützung der kommenden Optane-Generationen hinsichtlich der Speicherlösungen verraten.

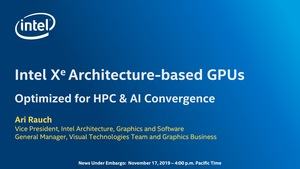

Intel wagt Ausblick auf Xe für HPC und AI

Das große Thema der kommenden Jahre ist bei Intel aber sicherlich die Entwicklung im Bereich der GPUs bzw. GP-GPUs, die im Datacenter für HPC- und AI-Anwendungen vorgesehen sind.

Intel will hier durch gleich mehrere Maßnahmen den Weg an die Spitze finden. Die Ponte Vecchio getaufte GPU soll zahlreiche technologische Meilensteine in sich vereinen. Zum einen wird sie der erste in 7 nm gefertigte Chip von Intel sein – dies hat man bereits vor einigen Monaten verraten. Zum anderen wird hier aber auch Intels Packaging-Technologie Foveros bzw. eine weitere Iteration davon zum Einsatz kommen. Per Xe-Link, dem Interconnect auf Basis von Compute Express Link, sollen mehrere GPUs zusammengeschaltet werden können.

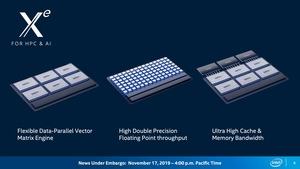

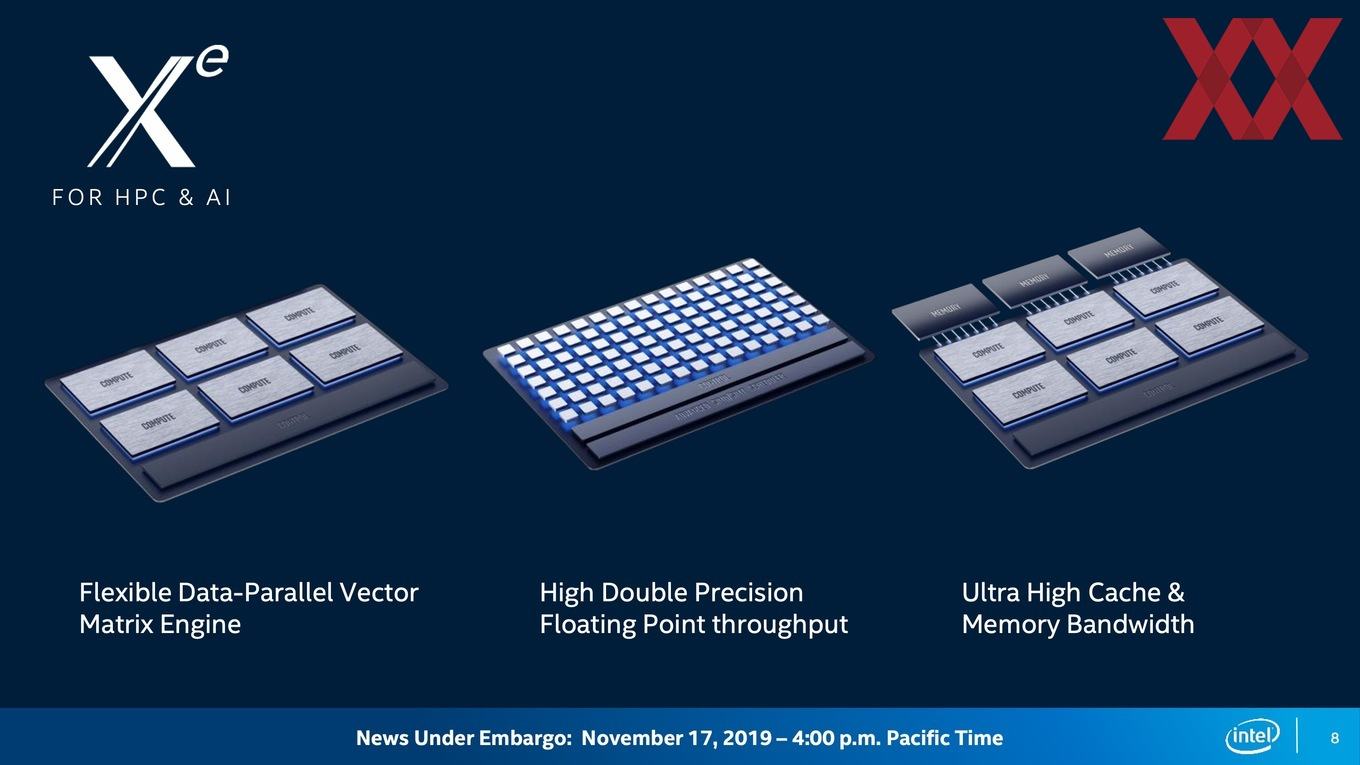

Über drei Punkte will Intel zum aktuellen Zeitpunkt bereits sprechen:

- eine Matrix-Engine kann möglichst viele Vektor-Berechnungen gleichzeitig ausführen

- die Rechenleistung für Berechnungen mit doppelter Genauigkeit (FP64) soll hoch sein

- sowohl die Caches als auch weiterer Speicher verfügen über eine extrem hohe Bandbreite

Allerdings bleibt Intel hier einige Fakten schuldig – wohl auch weil es noch Monate bis zum offiziellen Start sind.

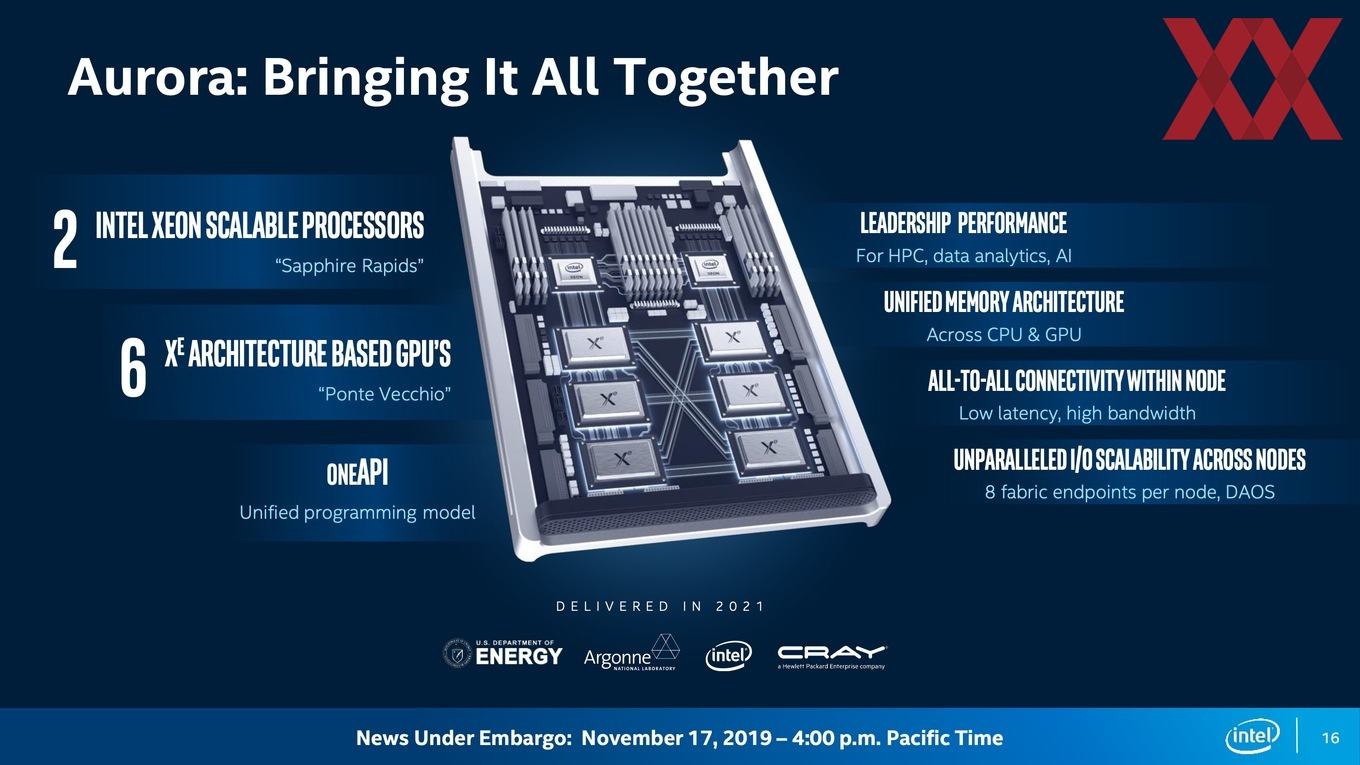

Eines der ersten Einsatzgebiete der neuen Xeon-Prozessoren auf Basis von Sapphire Rapids und der Xe-GPUs auf Basis von Ponte Vecchio wird der Supercomputer Aurora sein. Dieser wird ab 2021 dem Argonne National Laboratory in Chicago zur Verfügung stehen.

Pro Node plant Intel den Einsatz von zwei Xeon-Prozessoren. Hinzu kommen sechs der neuen Xe-GPUs. Untereinander verbunden sind alle wichtigen Komponenten über den CXL-Interconnect. Intel spricht von acht Fabric Endpoints – zwei Xeon-Prozessoren und sechs Xe-GPUs. Den Speicher sollen sich alle Komponenten untereinander teilen können.

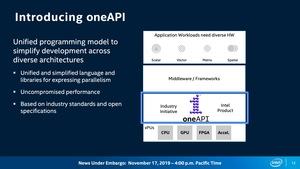

Um die Ressourcen der Hardware nutzen zu können plant Intel schon eine längere Zeit mit der OneAPI. In einem gesonderten Artikel haben wir die Ziele dieser Initiative bereits genauer beleuchtet.

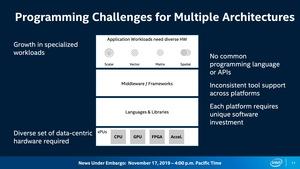

OneAPI soll die eine Lösung für alle und alles sein – damit sind aber nicht nur Entwickler gemeint. Letztendlich soll auch der Endkunde, egal ob Spieler, Workstation-Nutzer oder Datacenter-Betreiber, davon profitieren. Intel stellt über die One API optimierte Anwendungen, aber auch Middleware zur Verfügung. Im besten Fall soll dies auf Basis von Open Source geschehen. Eine derartige Auslegung hat aber durchaus auch ihre Hürden, schließlich soll höchstunterschiedliche Hardware angesprochen werden. Intel bietet ja nicht nur Prozessoren für diverse Märkte an, sondern auch integrierte und bald auch dedizierte Grafikeinheiten. Hinzu kommen AI-Beschleuniger (Matrixberechnungen) und FPGAs (spatiale Berechnungen).

Intel bereitet also alles auf den nächsten Schritt vor. Neben den Xeon-Prozessoren bilden die Xe-GPUs eine weitere Hardware-Ebene, die Chancen einräumt, die sich in Form von Hardware zunächst einmal aber auch manifestieren muss.

Update:

Auf der Keynote hat Intel weitere Details verraten, die nicht Teil des Pre-Briefings waren und die wir daher nachreichen wollen:

So nennt die eigentlichen Compute-Einheiten weiterhin Execution Units (EU), wie bei den aktuellen Grafikeinheiten aus eigenem Hause. Diese beinhalten allerdings keine klassische Shader-Pepeline, sondern sind auf Vektorberechnungen spezialisiert. Eine Flexibilität zu aktuellen Design-Ansätzen bleibt aber erhalten und so spricht Intel über die Möglochkeit Single Instruction Multiple Thread (SIMT) wie im Design eines Prozessors ebenso ausführen zu können wie Single Instruction Multiple Data (SIMD) wie dies bei den GPUs der Fall ist. SIMT und SIMD zusammen soll die maximale Leistung aus den Xe-Design herauskitzeln können.

An Datentypen unterstützt werden unter anderem INT8, BF16 und FP16. Auch auch FP32 und FP64 sollen für HCP-Anwendungen eine Rolle spielen. Die FP64-Rechenleistung will Intel im Vergleich zum aktuellen Design um den Faktor 40 erhöht haben.

Eine wichtige Rolle kommt dabei wie immer auch dem Fabric zu. Der Xe Memory Fabric (XEMF) soll mehrere tausend der neuen Xe-EUs miteinander verbinden können. Zwischen den einzelnen Chiplets wird es einen RAMBO-Cache geben. Dieser soll laut Intel nicht nur als Silizium-Komponente groß sein, sondern auch von der Speicherkapazität. Der RAMBO-Cache ist als Unified Cache allen CPUs und GPUs im System zugänglich. An externem Speicher verwendet Intel HBM – welcher Generation und mit welcher Geschwindigkeit wollte man nicht verraten.

Um den RAMBO-Cache im gesamten System zugänglich zu machen hat Intel einen weiteren Chip entwickelt, der zwischen den CXL-Links sitzt. Er wird als Xe Link bezeichnet. Mit dem CXL-Interconnect verbunden sind im AURORA-Supercomputer jeweils acht Xe-GPUs und zwei Xeon-Prozessoren.

Der physikalische Aufbau der "Ponte Vecchio"-Xe-GPU sieht wie folgt aus: Acht Compute-Chiplets mit den EUs befinden sich zusammen mit dem HBM in einem Package. Die EMIB-Technologie (Embedded Multi Die Interconnect Bridge) wird verwendet, um den HBM anzubinden. Die FOVEROS-Technik hingegen kommt zur Ein- und Anbindung des RAMBO-Cache zum Einsatz. Die acht Xe-Chiplets sind aber nur die eine Hälfte einer "Ponte Vecchio"-Xe-GPU. Die zweite Hälfte besteht aus weiteren acht Chiplets samt HBM.