Werbung

Im Januar zeigte Intel erstmals einen aktuellen Entwicklungsstand für die nächste Generation der GPU-Architektur alias Xe. Als integrierte Lösung sollen die kommenden Tiger-Lake-Prozessoren damit ausgestattet sein. In einer ersten Umsetzung präsentierte Intel ein Software Development Vehicle (SDV) der DG1 (Discret Graphics).

Zunächst einmal peilt Intel einen Leistungssbereich für das Gaming in 1080p an. Spätere Lösungen sollen dann zur größeren Konkurrenz für AMD und NVIDIA werden. Doch mit den 75 W des SDV der ersten Generation wird Intel damit sicherlich nicht auskommen.

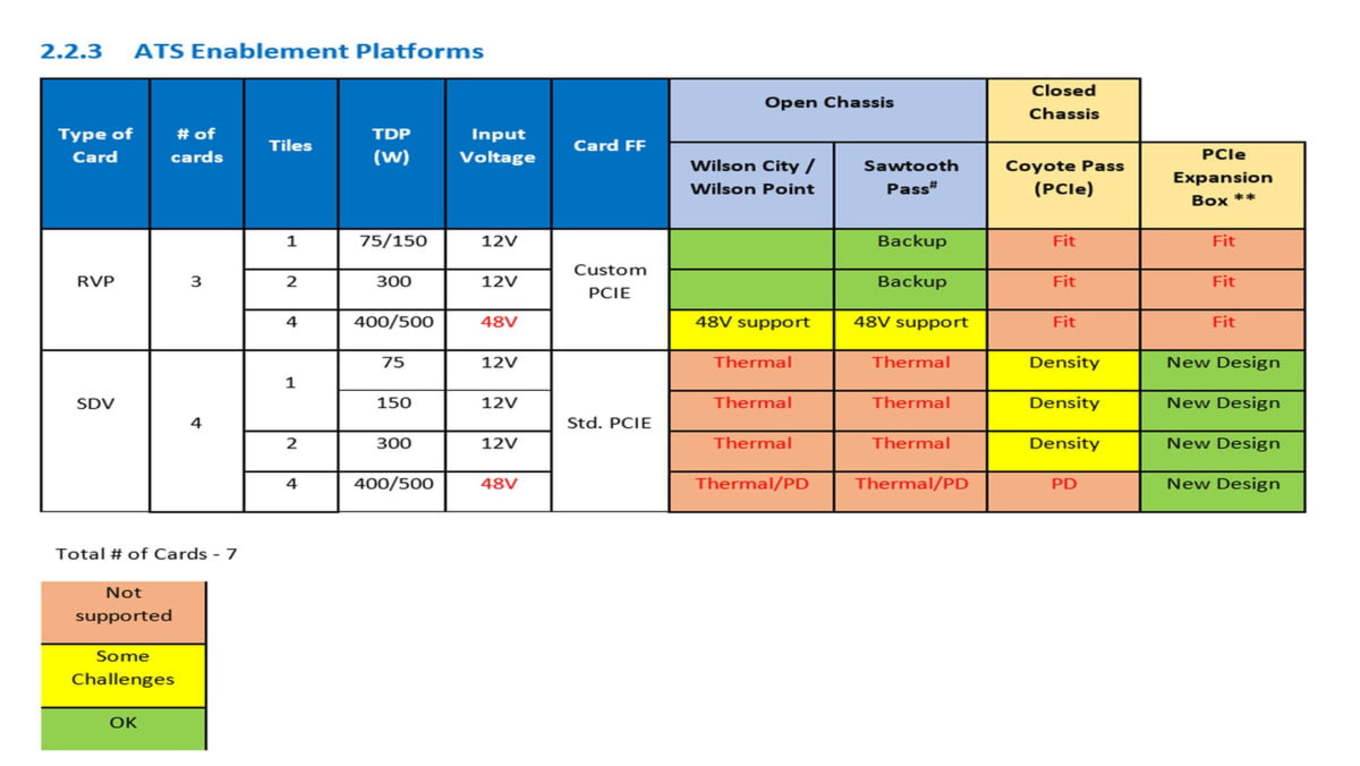

Ein auf 2019 datiertes internes Dokument von Intel, welches von Digital Trends veröffentlicht wurde, scheint sich mit der Stromversorgung und dem Design zukünftiger Lösungen zu beschäftigen. Aufgeführt werden offenbar SDV (Software Development Vehicle) und RVP (Reference Validation Platform) in verschiedenen Ausbaustufen. Diese sind offenbar als Standard-PCI-Express-Karte (im Falle des RVP für DG1 bereits geschehen) und als Custom-Design geplant. Mitte November 2019 zeigte Intel mit der "Ponte Vecchio" Xe-GPU eine erstes Konzept-GPU mit Fertigung in 7 nm sowie dem Einsatz von Foveros und CXL, welches sicherlich als Custom-Design laufen wird.

Eine Thermal Design Power von 75, 150 und 300 W liegt noch im Bereich dessen, was wir von aktuellen Lösungen kennen – sowohl im Desktop-, als auch im Serverbereich. Schon etwas anders sieht dies für die aufgeführte TDP von 400 und 500 W aus. Hier kennen wir eigentlich nur Intels aktuelle Cascade-Lake-AP-Prozessoren, wie den Xeon Platinum 9282, der 56 Kerne als MCM-Design mit einer TDP von 400 W vereint. Auch NVIDIA hat die Tesla V100 in der SMX2-Variante bereits auf bis zu 450 W getrimmt. Interessant ist an dieser Stelle auch die Versorgung über 48 anstatt 12 V, um die Ströme die zur Versorgung fließen müssen, zu reduzieren. Eine Versorgung mit 48 V kennen wir ebenfalls nur aus dem Datacenter.

Bekannt ist bereits, dass Intel an verschiedenen Designs der Xe-Architektur arbeitet, die unterschiedlich ausgelegt sind. Xe-LP wird für die DG1 zum Einsatz kommen und fokussiert sich auf eine möglichst hohe Effizienz bzw. einen geringen Verbrauch (75 und 150 W?). Xe-HP hingegen ist das, was wir womöglich also leistungsstarke Desktop-Karte erwarten dürfen (bis zu 300 W?). Natürlich zielt Intel hier auch auf den Workstation-Einsatz ab. Xe-HPC hingegen wird auf das Datacenter ausgelegt sein (400 bzw. 500 W?).

Die Anzahl der geplanten Karten und verwendeten Tiles ist sicherlich eine der interessantesten Informationen in diesem Dokument. Offenbar plant Intel bereits Chiplet-Designs mit bis zu vier Tiles ein. 75 und 150 W werden mit einem Tile abgedeckt, zwei Tiles benötigen bereits bis zu 300 W und 400 bzw. 500 W sollen von vier Tiles abgedeckt werden.

Aktuell wissen wir aber noch nicht einmal, wie viele EUs ein Chip des Xe-LP-Designs beinhaltet. Dementsprechend ist es schwer abzuschätzen, auf wie viele EUs wir bei zwei oder vier Tiles kommen. Denkbar wären 128 EUs für ein Tile und dementsprechend 512 EUs bei vier Tiles.

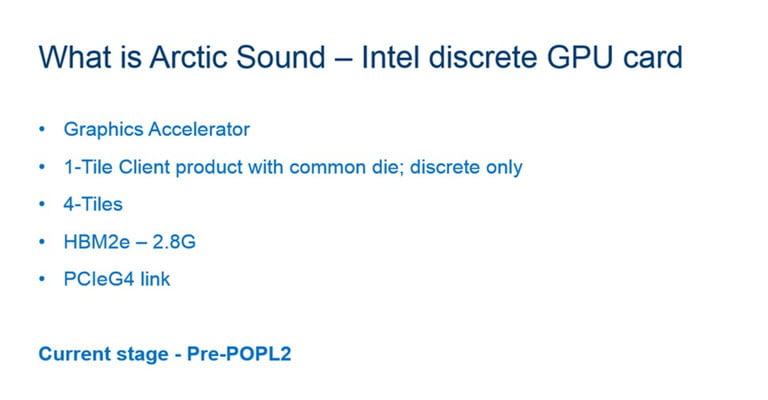

Arctic Sound: 1-4 Tiles, HBM2E und PCI-Express 4.0

Ein weiterer Screenshot aus dem Dokument offenbart Arctic Sound als diskrete Grafiklösung mit HBM2E-Speicher (dessen Einsatz für die "Ponte Vecchio" Xe-GPU bereits bestätigt ist) und einer Konfiguration aus ein bis vier Tiles. Außerdem sollen die Arctic-Sound-Chips PCI-Express 4.0 unterstützen.

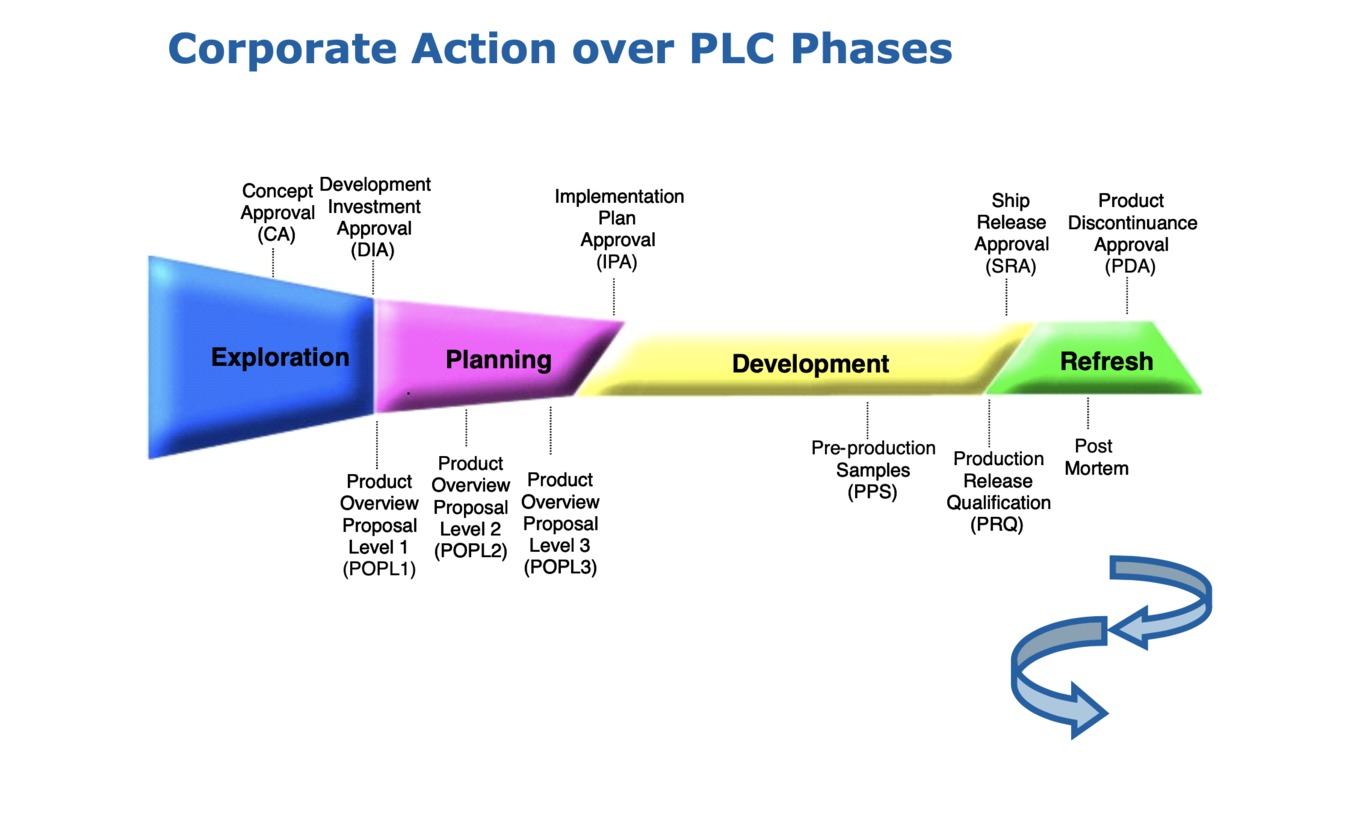

Arctic Sound befand sich zur Entstehung des Dokuments (Frühjahr 2019) in der Pre-POPL2-Phase (Product Overview Proposal Level 2). Die Grafik zeigt Intels eigene Abfolge in der Entwicklung und sollte in dieser Form noch Gültigkeit haben. Demnach befand sich Arctic Sound zum damaligen Zeitpunkt noch in einer Phase vor der eigentlichen Entwicklung der Chips.

Weitere Details gibt es bis auf die angesprochene Präsentation des SDV für DG1 und im Zusammenhang mit den Tiger-Lake-Prozessoren aktuell nicht. Die Informationslage ist ingesamt noch sehr dünn. Es dürften aber auch noch einige Monate vergehen, bis wir die erste Umsetzung der Xe-GPUs sehen werden. So lange es keine Bestätigung zur Echtheit des Dokumentes gibt, sollte auch dies mit Vorsicht genossen werden.

Update:

@_rogame hat einige interessante Einträge im Zusammenhang mit der HPC-Lösung Ponte Vecchio (PVC) gefunden. Die Möglichkeit Berechnungen in BFloat16 ausführen zu können, ist weniger überraschend (BF_CVT: Konvertierung von Fließkomma zu BFloat16).

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

Noch einmal bestätigt wird die Unterstützung von Raytracing durch Ponte Vecchio.