Werbung

NVIDIA hat auf der virtuellen Keynote der GPU Technology Conference die Katze aus dem Sack gelassen und die Ampere-Architektur vorgestellt. Noch kennen wir nicht alle Details, aber wir kennen einige Eckdaten der neu vorgestellten Produkte. Nach der Vorstellung der Volta-Architektur vor drei Jahren, stellt NVIDIA nun den Nachfolger vor.

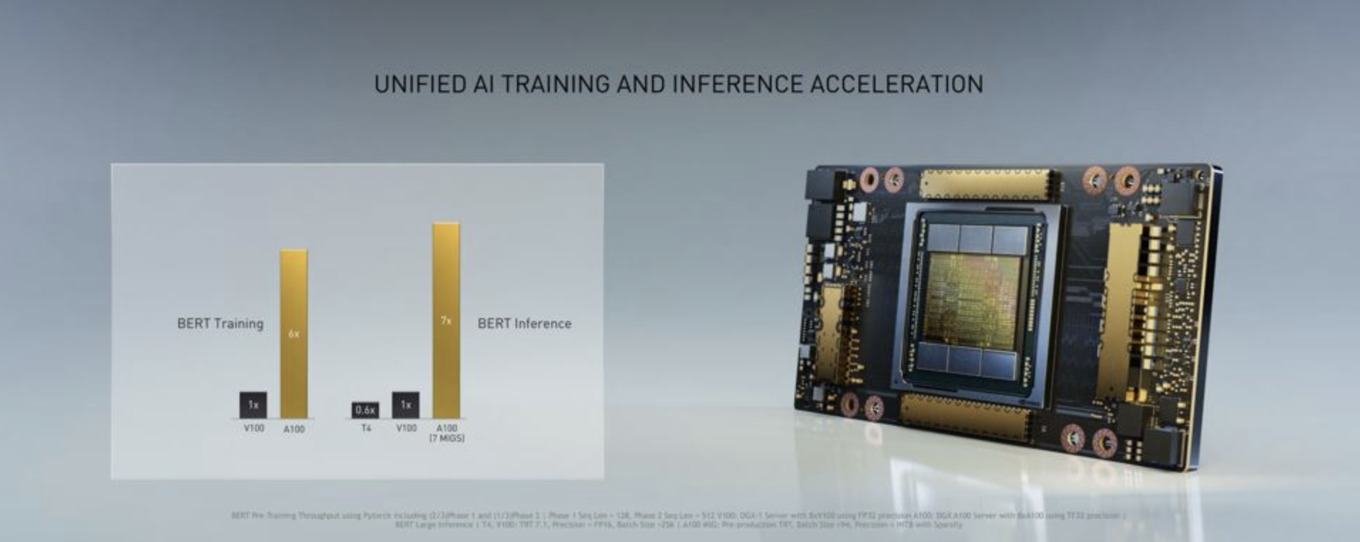

Die Ampere-Architektur wurde im Hinblick auf drei Ziele entwickelt: Die Leistung sollte signifikant gesteigert werden. Am Ende ist man in einigen Bereichen bei einem Leistungsplus im Faktor 20 gelandet. Zudem sollten die GPGPUs flexibler werden. Stellt man die Volta- und Turing-Architektur gegenüber, dann zeigt dies recht deutlich, dass NVIDIA die erstgenannte auf HPC und das AI-Training ausgelegt hat, während Turing auf das Gaming und ein AI-Inferencing hin optimiert ist. Die Möglichkeit beides in der Ampere-Architektur anzusprechen, soll das Datacenter homogenisieren (Elastic Datacenter).

Die Ampere-Architektur wird das Zugpferd der HPC-Strategie von NVIDIA sein. Hinzu kommen neue Technologien in der Infrastruktur der GPGPU-Beschleuniger, wie ein schnellerer NVLink-Interconnect und eine schnellere sowie intelligentere Netzwerkanbindung. Auf einige der Aspekte werden wir in der Folge nun etwas genauer eingehen.

GA100: 7 nm und 54 Milliarden Transistoren auf 826 mm²

Laut NVIDIA ist die neue Ampere Datacenter-GPU bereits in Produktion und die entsprechende Hardware soll demnach in Kürze verfügbar sein. Was wir über die GPU wissen ist, dass diese in 7 nm gefertigt wird. Auch die Chipfläche kennen wir: Die GA100-GPU kommt auf 826 mm². Die Anzahl der Transistoren liegt bei 54 Milliarden. Zum Vergleich: Die Vorgänger-GPU V100 kommt auf 21,1 Milliarden Transistoren bei einer Fläche von 815 mm². Allerdings wird dieser noch in 12 nm gefertigt. Ein kompletter EPYC-Prozessoren auf Basis des Rome-Designs kommt mit seinen neun Chips (8x CCD + 1x IOD) auf 39,54 Milliarden Transistoren.

Eine GA100-GPU ist also ein gigantischer Chip. Gefertigt wird er bei TSMC im 7N-Prozess. Es handelt sich damit um den größten und komplexesten Chip, der aktuell in 7 nm gefertigt wird. Viel größer lasse sich ein rechtwinkliger Chip kaum noch sinnvoll produzieren – so NVIDIA.

Zum großen Chip mit seinen Milliarden Transistoren gesellen sich auch noch sechs HBM2-Speicherchips, die eine Kapazität von 40 GB für eine GA100-GPU zur Verfügung stellen. Die Speicherchips sollen von Samsung stammen. 40 GB Speicher teilen sich allerdings nicht sonderlich gut auf sechs Speicherchips auf. Inzwischen ist klar: NVIDIA verbaut zwar sechs HBM2-Speicherchips, aber nur fünf werden auch verwendet. Bei 5x 8 GB kommen wir auf 40 GB für eine GA100-GPU und das Speicherinterface ist 5.120 Bit breit. Es ist das erste Mal, dass NVIDIA eine Datacenter-GPU derart umsetzt. Die Titan V verwendete ebenfalls nur drei von vier verfügbaren HBM2-Speicherchips, aber diese ist auch in einem anderen Markt zu verorten. Da NVIDIA für die GA100-GPU nur 108 der vermeintlich insgesamt 128 SMs verwendet, passt das Verhältnis auch zum Speicherinterface, welches bei nur fünf Speicherchips 5.120 Bit breit ist.

Vergleich der Rechenleistung

Laut NVIDIA verfügt die GA100-GPU über 108 SMs und diese jeweils über 64 Shadereinheiten. Somit kommen wir hier auf 6.912 Shadereinheiten. Pro SM sollen es weiterhin 32 FP64-Rechenkerne sein. Die Anzahl der Tensor Cores pro SM hat NVIDIA von acht auf vier halbiert. Deren Funktionsumfang hat NVIDIA aber deutlich ausgeweitet.

Mit der Volta-Architektur führte man die Tensor Cores erstmals ein. In der Turing-Architektur kommen sie auch in den GeForce-RTX-Karten zum Einsatz und berechnen dort den Bildaufbau des DLSS 2.0. Erwartungsgemäß baut NVIDIA die Tensor Cores in der dritten Generation weiter aus und lässt diese neben INT16 und FP16 als Datensätze mit der bisher höchsten Genauigkeit nun auch FP32- und FP64-Berechnungen durchführen. Damit helfen die Tensor Cores nicht nur die Rechenleistung im AI-Bereich deutlich zu verbessern, sondern unterstützen die Shader nun auch im HPC-Segment, wo höhere Genauigkeit gefordert sind. NVIDIA spricht von einer um den Faktor 20 höheren AI-Rechenleistung für FP32-Berechnungen.

| Ampere | Volta | Turing | |

| GPU | GA100 | GV100 | TU102 |

| SMs | 108 | 80 | 72 |

| FP64-Kerne / SM | 32 | 32 | 2 |

| FP64-Kerne / GPU | 3.456 | 2.560 | 144 |

| FP32-Kerne / SM | 64 | ||

| FP32-Kerne / GPU | 6.912 | ||

| Tensor-Kerne / SM | 4 | 8 | 8 |

| Tensor-Kerne / GPU | 432 | 640 | 576 |

| FP64-Rechenleistung | 9,7 TFLOPS | 8,2 TFLOPS | 510 GFLOPS |

| FP64-Rechenleistung Tensor Core | 19,5 TFLOPS | - | - |

| FP32-Rechenleistung | 19,5 TFLOPS | 16,4 TFLOPS | 16,3 TFLOPS |

| TF32-Rechenleistung | 156 / 312 TFLOPS | - | - |

| FP16-Rechenleistung | 39 TFLOPS | 32,8 TFLOPS | 32,6 TFLOPS |

| FP16-Rechenleistung Tensor Core | 312 / 624 TFLOPS | - | - |

| BFLOAT16-Rechenleistung | 312 / 624 TFLOPS | - | - |

| INT8-Rechenleistung | 624 / 1.248 TOPS | 130 TOPS | 261 TOPS |

| INT4-Rechenleistung | 1.248 / 2.496 TOPS | 260 TOPS | 522 TOPS |

| Speicher | 40 GB HBM2 5.120 Bit 1.536 GB/s | 32 GB HBM2 4.096 Bit 1.134 GB/s | 48 GB GDDR6 384 Bit 672 GB/s |

| TDP | 400 W | 450 W | 280 W |

Zusammen mit den Tensor Cores der dritten Generation führt NVIDIA ein neues Gleitkommaformat ein. TF32 oder Tensor Float 32 soll den Wertebereich von FP32 aufweisen, dabei aber nur die Genauigkeit von FP16 verwenden. NVIDIA kombiniert hier also die Vorteile aus FP32 und FP16 und passt diese den Bedürfnissen in bestimmten Bereichen an.

Bei den Angaben zur Rechenleistung sei noch erwähnt, dass NVIDIA hier eine neue Technik einführt: Sparsity/Sparse Matrix oder die dünnbesetzte/schwachbesetzte Matrix. Besteht eine Matrix aus sehr vielen mit Nullen besetzten Einträgen, können über verschiedene Techniken diese Bereiche in der Berechnung und Speicherung effizienter genutzt werden. Bei aktiverter Structural Sparsity verdoppelt sich die Rechenleistung daher theoretisch.

Schlussendlich auch noch ein Vergleich zu anderen HPC- und AI-Lösungen: Eine Radeon Instinct MI50 kommt auf eine FP64-Rechenleistung von 6,6 TFLOPS und bietet 53 TOPS für INT8-Berechnungen.

MIG (Multi Instance GPU)

Eine neue Technologie der Ampere-Architektur bzw. der GA100-GPU ist die Möglichkeit die zur Verfügung stehenden Ressourcen per Multi Instance GPU (MIG) in sieben unabhängige Instanzen zu verwandeln. Aus der GA100-GPU werden sozusagen sieben eigenständige, kleinere GPUs. Diesen sieben virtuelle GPUs können eigenen Ressourcen in Form von Speicherbandbreite, Caches, etc. zugeteilt werden. Letztendlich ist eine GA100-GPU in der Lage sieben Tesla T4 zu ersetzen.

Die MIG-Technik ist laut NVIDIA einer der Schlüssel, um aus eine recht unflexiblen GPU eine solche für ein Elastic Datacenter zu machen, in dem sie für die verschiedensten Anwendungsbereiche genutzt werden kann. Die bisherige Technologie namens Virtual GPU (vGPU) benötigte mehrere Software-Ebenen (Hypervisor und die Virtualisierungssoftware), um einen ähnlichen Effekt zu erzielen. MIG virtualisiert die GPU aber schon deutlich näher zur Hardwareebene und macht diese Funktion deutlich effektiver.

Noch viele Unbekannten

Was wir nicht wissen ist, welchen Maximalausbau NVIDIA für die GA100-GPU vorsieht. In den Gerüchten wurden 128 SM besprochen. Für die GA100-GPU verwendet NVIDIA nun aber nur 108, was ein recht großer Ausschuss wäre. Bei der GV100-GPU waren 80 der 84 verfügbaren SMs aktiv, was einem Ausschuss durch Defekte von gerade einmal 5 % entspricht. Nur 108 von 128 aktive SMs würde einem inaktiven Anteil von 15 % entsprechen – weit mehr als zu erwarten wäre.

Für die Turing-Architektur führte NVIDIA die gleichzeitig Nutzung der INT32- und FP32-Berechnungen ein, was für die Spieleleistung von hoher Bedeutung ist. Ob die Ampere-Architektur diese INT32-Einheiten besitzt, wissen wir nicht. Dies gilt auch für die RT Cores zur Hardwarebeschleunigung von Raytracing-Berechnungen. Auch zur restlichen Renderpipeline fehlen uns die Angaben und es ist auch gar nicht klar, ob die Ampere-Architektur diese überhaupt besitzt.

So wirklich können wir also noch keine Rückschlüsse ziehen, ob und in welcher Form die Ampere-Architektur für zukünftige GeForce-Grafikkarten zum Einsatz kommen wird.

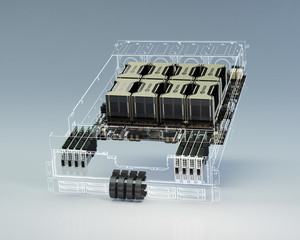

DGX A100: 8x Tesla A100 für insgesamt 320 GB HBM2-Speicher

Die GA100-GPU kommt vor allem in den DGX-Servern zum Einsatz. Diese verwenden acht der SMX2-Module. Die Rechenleistung multipliziert sich entsprechend:

- FP64: 156 TFLOPS

- TF32: 2.5 PFLOPS

- FP16: 5 PFLOPS

- INT8: 10 POPS

Doch ein DGX A100 ist weit mehr als nur eine Ansammlung von acht GA100-GPUs. Die acht GPUs wurden über den NVLink der dritten Generation miteinander verbunden. Dazu kommen sechs NVSwitches zum Einsatz. Jeder der NVSwitches bietet eine GPU-GPU-Bandbreite von 600 GB/s. Dies bedeutet eine Verdopplung der Bandbreite gegenüber den Tesla V100. Die 600 GB/s pro GPU werden über 12 NVLinks zu je 50 GB/s realisiert.

In einem DGX A100 verbaut NVIDIA sechs NVSwitches, die eine zusammengenommene Bandbreite von 4,8 TB/s verarbeiten können.

Weiterhin verwendet NVIDIA in den DGX-Systemen ab dem A100 keine Intel-Prozessoren mehr, sondern setzt auf zwei EPYC-Prozessoren von AMD auf Basis des Rome-Designs mit 64 Kernen. Den Prozessoren zur Seite gestellt werden 1 TB an Arbeitsspeicher und 15 TB an schnellen NVMe-SSDs, die per PCI-Express 4.0 angebunden sind.

Die Möglichkeit der Anbindung per PCI-Express 4.0 dürfte ein wichtiger Faktor für die Entscheidung hin zu den EPYC-Prozessoren gewesen sein. Neben der Anbindung der NVMe-SSDs können darüber auch die neun Mellanox ConnectX-6 Lx SmartNICs angebunden werden, die eine Ethernet-Anbindung mit 2x 25 GBit/s ermöglichen. Ob Alle DGX- und HGX-Systeme zukünftig auf EPYC-Prozessoren setzen werden, ist nicht bekannt.

Die GA100-GPU wird es vorerst ausschließlich in der SMX2-Variante geben. Einzeln oder als PCI-Express-Karte wird NVIDIA sie auf absehbare Zeit nicht anbieten. Ein Grund ist unter anderem, dass NVIDIA das komplette Board mit den acht A100-Modulen fertigen lässt, da ein solch komplexes Mainboard bestimmte Voraussetzungen stellt. Die OEMs und ODMs kaufen also ein komplettes Mainboard und nicht mehr nur die einzelnen Komponenten.

Ein DGX A100 kostet 199.999 US-Dollar und ist ab sofort erhältlich.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen

HGX A100 und die Mellanox ConnectX-6 Lx SmartNICs

Als HGX A100 bietet NVIDIA das Mainboard mit den acht Modulen und der Netzwerkanbindug auch den Hyperscalern an. Entsprechende Systeme werden von den OEMs und ODMs angeboten werden. Solche Systeme mit vier GA100-GPUs können auch mit den speziellen EGX-A100-Modulen ausgestattet werden. Dazu kommen wir gleich.

Die Mellanox ConnectX-6 Lx SmartNICs haben wir bereits angesprochen. Sie stellen eine schnelle Anbindung zum Netzwerk bereit. NVIDIA kombiniert den dort verwendeten Netzwerkchip ConnectX-6 aber auch mit der GA100-GPU und nennt den EGX A100. Damit erfolgt eine engere Verzahnung zwischen den GPGPUs und dem Netzwerk. Hier wird dann eine Anbindung von 2x 100 GBit/s per Ethernet oder InfiniBand direkt an die GPU bzw. in den Speicher der GPU ermöglicht.

In den DGX-A100-Systemen kommen die Mellanox ConnectX-6 Lx SmartNICs aber auch als vorm dem Erweiterungskarten zum Einsatz. NVIDIA selbst verwendet für die eigenen DGX-A100-Hardware gleich neun dieser Netzwerkkarten mit 2x 25 GBit/s. Hier ist die Anbindung mittels PCI-Express 4.0 ein wichtiger Faktor.

Die Wichtigkeit immer schnellerer Interconnect-Technologien zeigt sich in allen Bereichen des Datacenter-Marktes. Inzwischen zeichnet sich eine Etablierung des CXL-Interconnects über die verschiedenen Herstellern hinweg ab. Gen-Z soll als weiterer offener Standard die Verbindung zwischen den Nodes und Racks übernehmen. NVIDIA hat die Übernahme von Mellanox inzwischen abgeschlossen und in Form der EGX A100 zeigen sich die ersten Früchte der Zusammenarbeit.

Daten sollten wenn möglich gar nicht von A nach B bewegt werden und wenn doch sollten sie entsprechend optimiert sein. Sogenannten SmartNICs sollen die Daten entsprechend vorbereiten. NVIDIA will die Interconnect- bzw. Netzwerktechnologie tiefer in die eigenen GPGPUs integriert. Die Prozessoren sollen als Management-Ebene für diese Techniken weitestgehend überflüssig werden. Der Trainings-Beschleuniger Gaudi von Habana Labs bietet beispielsweise zehn 100-GBit/s-Netzwerkinterconnects. Für Habana Labs ist eine möglichst schnelle und latenzfreie Netzwerkanbindung ein essentieller Bestandteil für solche Hardware.

Eben diesen Weg schlägt nun auch NVIDIA ein bzw. hat dies schon in der Vergangenheit getan. Die Netzwerkinfrastruktur ist ein wichtiger Punkt, die dazugehörige Software ein anderer. NVIDIA verwendet das Netzwerkprotokoll RDMA over Converged Ethernet (RoCE). Dazu werden InfiniBand-Transportpakete über Ethernet übertragen. Über verschiedenen Maßnahmen soll RoCE v2 vor allem hinsichtlich der Latenzen verbessert werden. Auch die gegenseitigen Zugriffe auf den Speicher über das Netzwerk werden mit RoCE v2 deutlich verbessert.

Erste DGX A100 bereits ausgeliefert

NVIDIA hat die ersten DGX-A100-Server bereits ausgeliefert. Unter anderem gingen einige an das Argonne National Laboratory, um dort an der Forschung an Wirkstoffen gegen COVID-19 zu arbeiten.

Aber NVIDIA hat natürlich wirtschaftliche Interessen möglichst viele DGX-A100-Systeme zu verkaufen und dies ist auch keinesfalls verwerflich. Besteht eine AI-Datacenter heute aus 50 DGX-1 und weiteren Servern mit etwa 600 Prozessoren um eine gewisse Rechenleistung zu erreichen, sollen zukünftig fünf DGX A100 ausreichen. Anstatt 25 Racks und eine Leistungsaufnahme von 630 kW sollen dann ein Rack und 28 kW ausreichen. Die Kosten werden von 11 auf 1 Million US-Dollar für die Anschaffung reduziert.

Hier soll sich Jen-Hsun Huang Lieblingssatz "The more you buy, the more you save" bewahrheiten.

Doch NVIDIA geht noch weitere: Ein DGX A100 SuperPOD besteht aus 140 DGX A100 und bietet eine Rechenleistung von 700 PFLOPS. Vier dieser SuperPODs hat NVIDIA seinem eigenen SATURNV Supercomputer hinzugefügt. Zusammen mit den 1.800 älteren DGX-Systemen kommt dieser auf eine Rechenleistung von 4,6 EFLOPS – wohlgemerkt für AI-Berechnungen.

In der virtuellen Keynote zur GTC20 hat NVIDIA auch noch zahlreiche weitere Anwendungen im Industrie- und Automotive-Bereich vorgestellt. Unter anderem statten die ersten Anbieter ihre autonomen Fahrzeuge mit der Drive AGX Xavier Plattform aus. Auch in diesem Segment treibt NVIDIA die Entwicklung also voran – mit der Unterstützung der DGX-A100-Systeme natürlich.

Drive AGX Orin wird als GPU auf die Ampere-Architektur setzen und wurde Ende 2019 erstmals vorgestellt.