Werbung

In einem sogenannten Deep Dive hat Jonah Alben, Senior Vice President des GPU-Engineering bei NVIDIA einige weitere Fragen und Details zur Ampere-Architektur beantwortet. Alle wichtigen Details zur Ampere-Architektur haben wir uns bereits angeschaut. Darüber hinaus haben wir uns bereits in einer Analyse damit beschäftigt, wie viel GeForce in der GA100-GPU steckt.

Wer sich neue Erkenntnisse zu einer möglichen nächsten Generation der GeForce-Karten erwartete, wird allerdings enttäuscht sein, denn NVIDIA spricht aktuell ausschließlich über die A100 Tensor Core GPU bzw. die GA100-GPU in der Ausführung, wie sie für A100 zum Einsatz kommt.

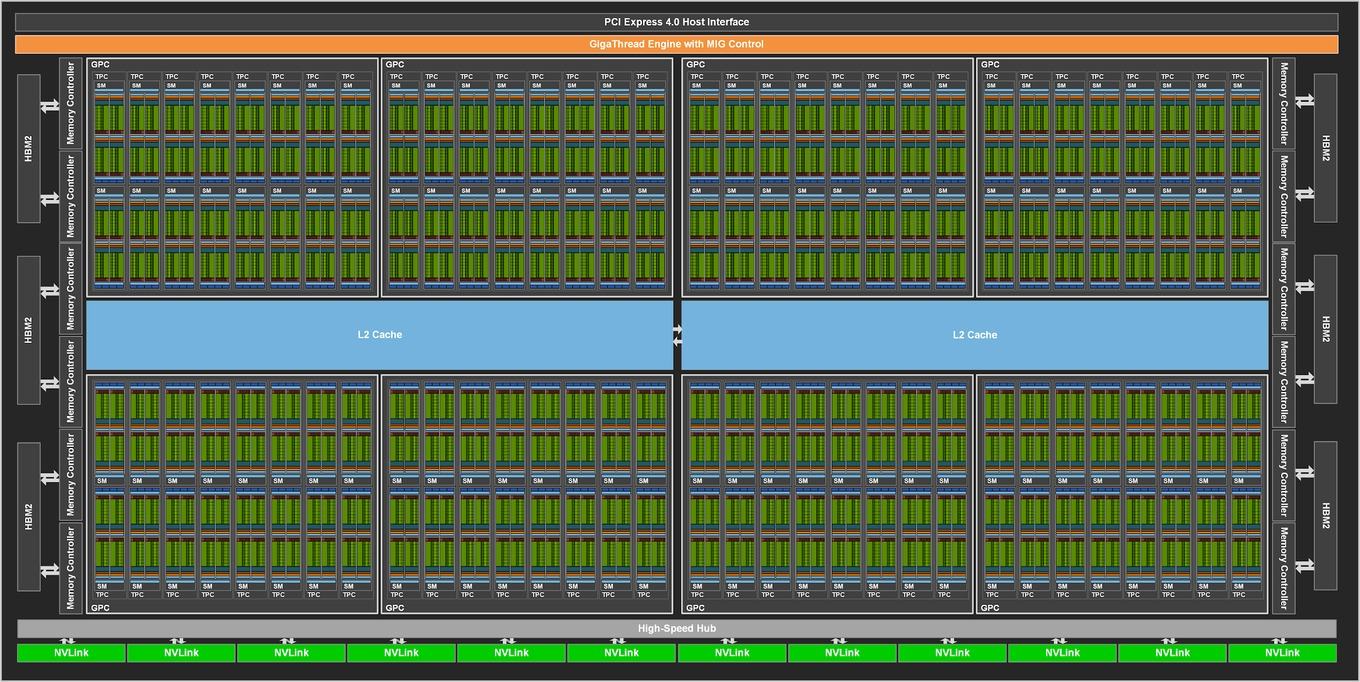

Zunächst einmal bleibt festzuhalten, dass sich die Ampere- und Volta-Architektur ähnlicher sind, als dies auf den ersten Blick den Eindruck macht. So verzichtet auch die GA100-GPU auf die RT Cores, kann also keine Hardwarebeschleunigung für Raytracing-Berechnungen bieten. Zudem bestätigte Alben, dass insgesamt 48 MB an L2-Cache vorhanden sind, aber nur 40 MB angesprochen werden – analog zur Nutzung von nur 108 der 128 für den Vollausbau vorgesehenen SMs. In der Topologie sieht NVIDIA acht sogenannte Slices mit jeweils 512 kB pro Speichercontroller vor. 8 x 512 kB x 12 Speichercontroller entspricht 49.152 kB und demzufolge 48 MB an L2 Cache insgesamt.

Dies führt uns zum Speicher. NVIDIA verwendet für die A100 Tensor Core GPU 40 GB an HBM2 – 5x 8 GB. Das eigentlich 6.144 Bit breite Speicherinterface ist aufgrund der Nutzung von nur fünf der sechs Speicherstacks nur 5.120 Bit breit. Beim sechsten Speicherstack handelt es sich nicht um einen Dummy, sondern einen funktionstüchtigen Speicherchip, der allerdings einfach nicht genutzt wird.

Zusammengenommen lässt NVIDIA hier einen Großteil der zur Verfügung stehenden Ressourcen brach liegen. Dies wird man allerdings nicht ohne Grund tun, denn die Ausbeute in der Fertigung wird einfach nicht gut genug sein, um eine höhere Ausbaustufe als 108 SMs gewährleisten zu können.

Um die Thermal Design Power bei 400 W einhalten zu können beschränkt NVIDIA den GPU-Takt bei gegebener Rechenleistung auf 1.410 MHz. Dies kann aber ebenfalls nicht als Indikator für einen GeForce-Ableger der Ampere-Architektur herhalten, da wir hier bereits in der Chipgröße ganz andere Voraussetzungen sehen werden.

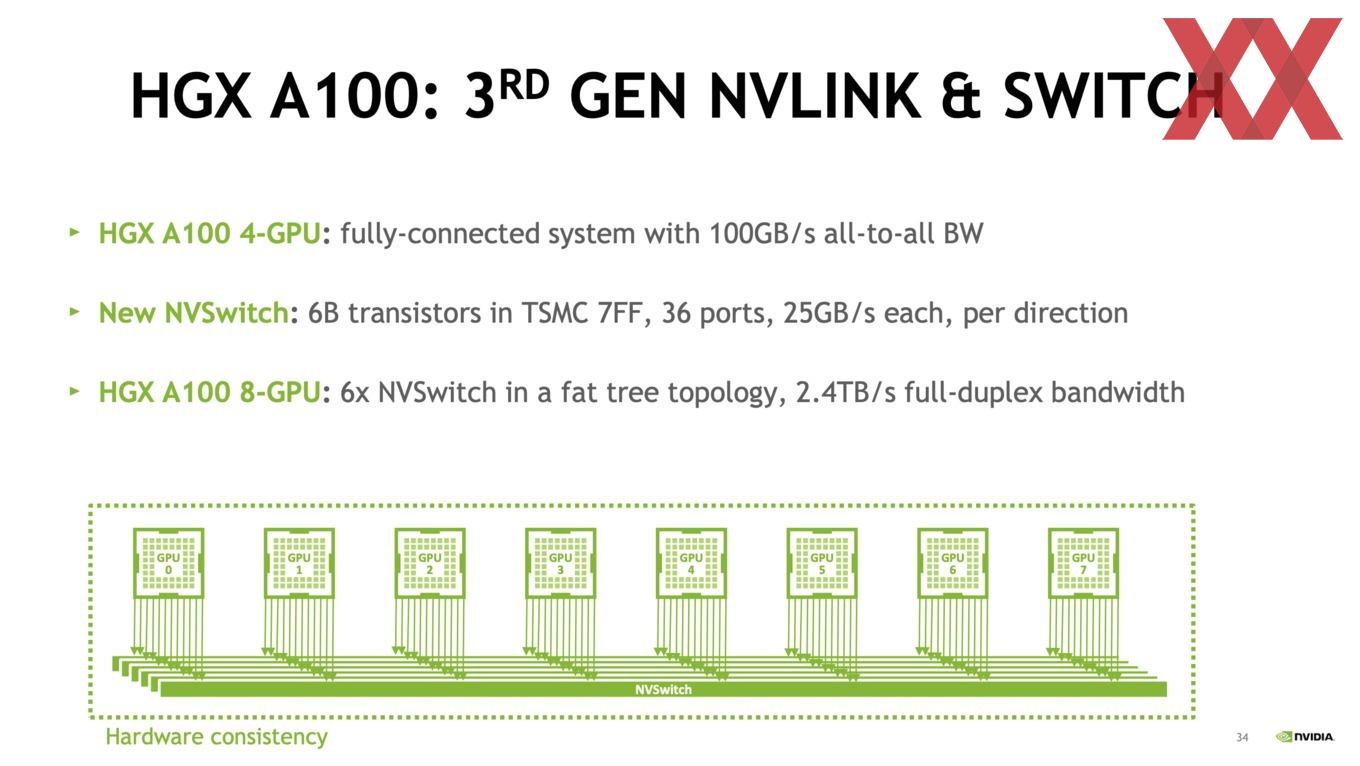

Bis auf weiteres wird es keine PCI-Express-Variante der A100 Tensor Core GPU gehen. NVIDIA liefert nur die HGX A100 bestehend aus vier direkt per NVLink miteinander verbundenen SMX4-Modulen sowie die DGX-Varianten mit acht oder 16 SMX4-Modulen, die dann den NVSwitch der dritten Generation verwenden.

NVSwitch 2.0: 6 Milliarden Transistoren in 7FF gefertigt

Eine große Bedeutung in der Infrastruktur der A100 Tensor Core GPUs kommt NVLink und den neuen NVSwitches zu. Direkt miteinander verbunden erreichen die A100-Beschleuniger eine NVLink-Datenrate von 100 GB/s zueinander. Bei mehr als vier GPUs kommen die neuen NVSwitches zum Einsatz.

Diese werden bei TSMC in 7FF gefertigt und besitzen 6 Milliarden Transistoren. Die ersten NVSwitches wurden noch in 12 nm gefertigt und kommen auf zwei Milliarden Transistoren. Die Komplexität ist also um den Faktor drei angestiegen. Jeder der NVSwitches verfügt über 36 NVLink-Ports mit einer bidirektionalen Datenrate von 25 GB/s pro Port.

Jeder der NVSwitches bietet in den A100-Systemen eine GPU-GPU-Bandbreite von 600 GB/s. Dies bedeutet eine Verdopplung der Bandbreite gegenüber den Tesla V100. Die 600 GB/s pro GPU werden über 12 NVLink-Ports realisiert.