Werbung

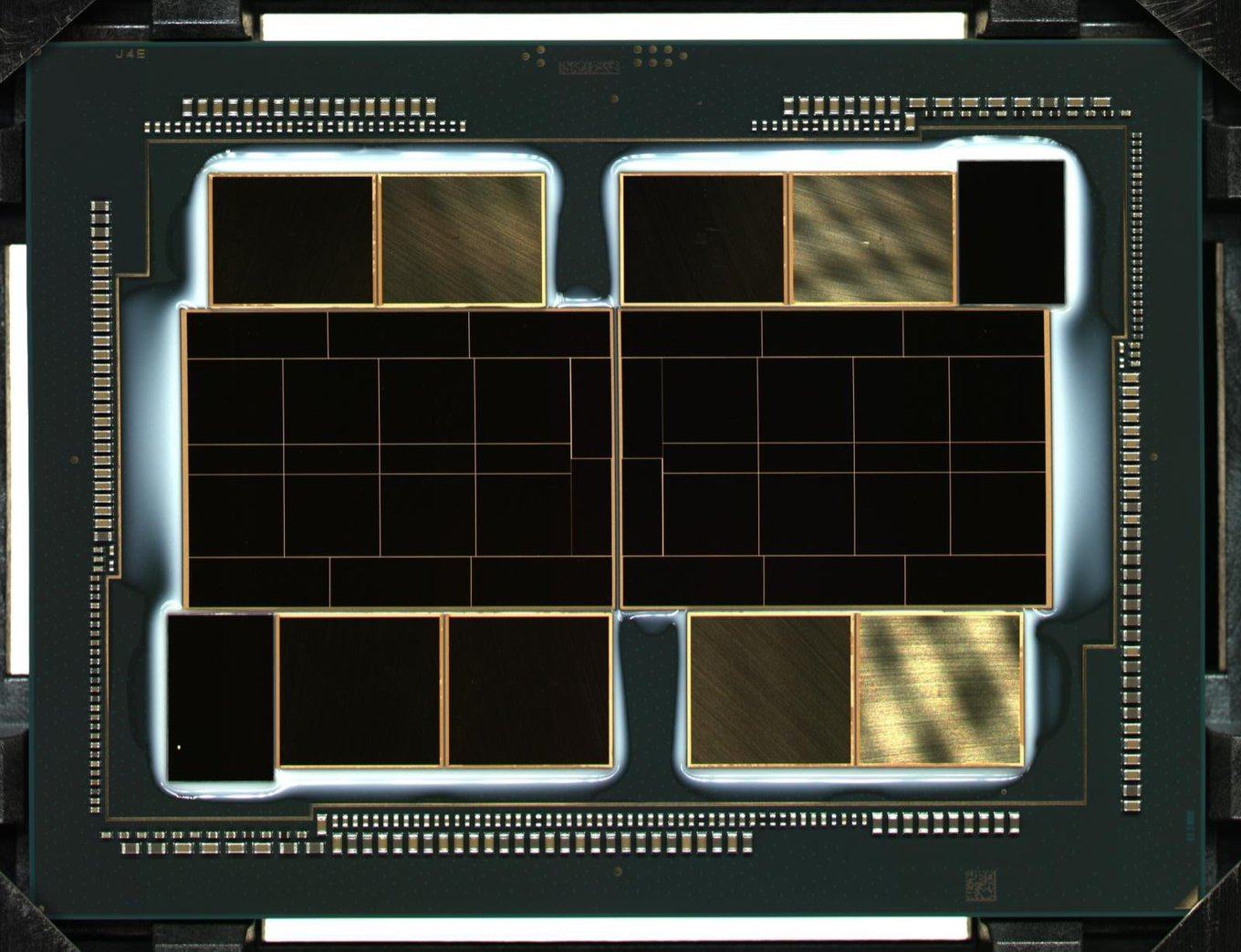

Auf Twitter hat Raja Koduri, seines Zeichens Senior Vice President der neuen Grafiksparte "Core and Visual Computing" bei Intel, ein Foto eines Xe-HPC-Chips alias Ponte Vecchio veröffentlicht. Der GPU-Beschleuniger verwendet ein komplexes Chiplet-Design. Der Compute-Chiplet basiert auf der Xe-HPC-Architektur, als dem Datacenter-Ableger der Xe-Familie.

Offenbar hat man nun den ersten kompletten Chip erhalten und wird diesen in einem nächsten Schritt erstmals starten – das sogenannte "Power on". Laut Koduri kommen für das Package sieben unterschiedliche Technologien gemeinsam in einem Package zum Einsatz ("7 advanced silicon technologies in a single package"). Um welche es sich genau handelt, ist nicht bekannt.

Den Chip das erste Mal in Betrieb zu nehmen ist ein wichtiger Schritt. Erst dann lässt sich erkennen, ob es eventuell noch Fehler im Design gibt. In einer Evaluierungsphase wird überprüft, ob alle Funktionen so umgesetzt wurden, wie dies angedacht war. Ist dies nicht der Fall, können noch Korrekturen gemacht werden.

Die Xe-HP-GPUs haben die "Power on"-Phase bereits durchschritten und dürfen sich in der Erweiterten Evaluierung befinden. Erste Samples sind bereits aus Kunden ausgeliefert worden. Intel plant die Xe-HP-GPU-Beschleuniger in diesem Jahr auf den Markt zu bringen. Auch wenn Intel auch für Xe-HP ein Chiplet-Design verwendet, so ist dies mit 1, 2 oder 4 Compute-Dies weit weniger komplex als bei den Xe-HPC-Chips, wie viele unterschiedliche Komponenten zusammenkommen.

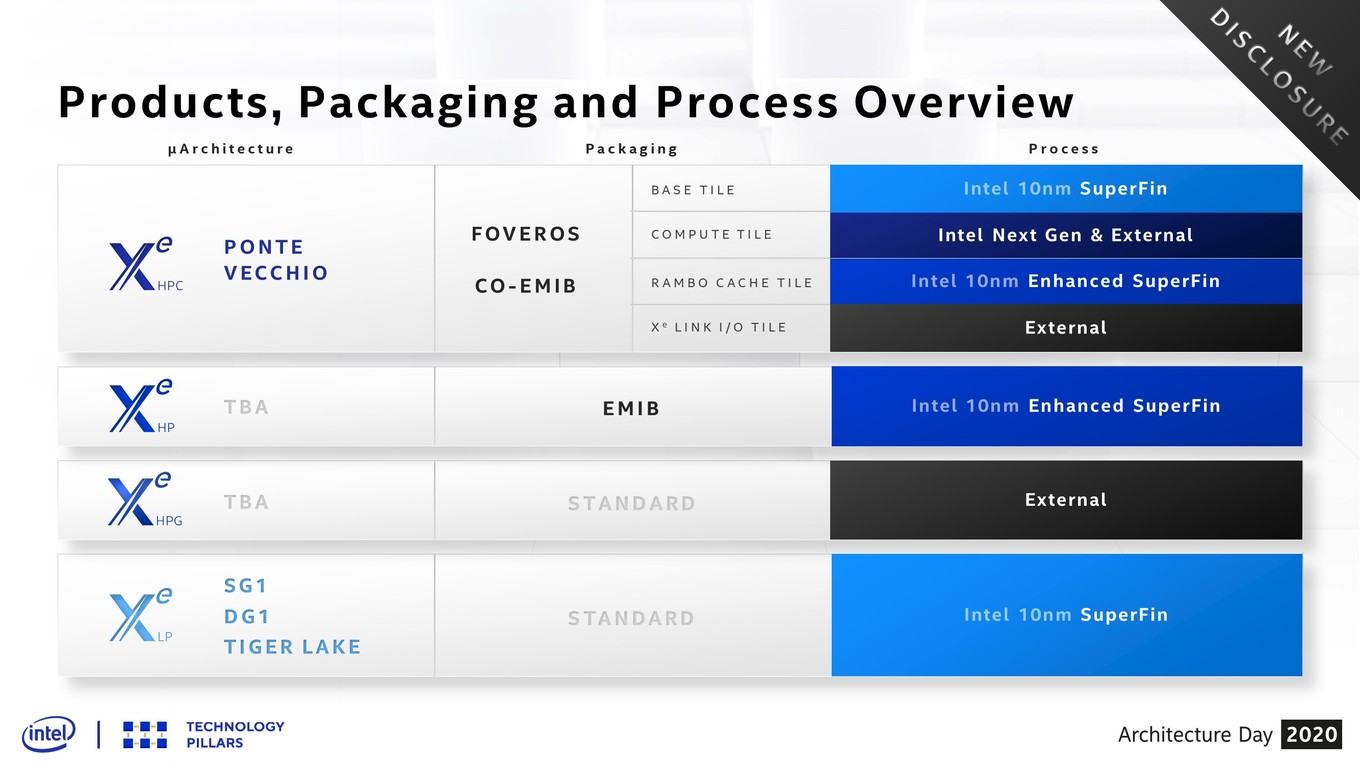

Für Ponte Vecchio, so der Codename des HPC-Chips, verwendet Intel verschiedene Tiles oder Chiplets. So gibt es einen Base Tile, einen Compute Tile, einen Rambo Cache Tile und einen Xe Link I/O Tile. Letztgenannter soll extern gefertigt werden, genau wie gewisse Stückzahlen des Compute Tiles. Diesen will Intel aber auch in einem nicht näher genannten Next-Gen-Prozess selbst fertigen. Den Base Tile fertigt man in der aktuellen 10nm-SuperFin-Technologie. Der Rambo Cache Tile soll in 10 nm Enhanced SuperFin, also einer bereits verbesserten Variante, gefertigt werden. Hinzu kommen die Packaging-Technologien Foveros und CO-EMIB. Nimmt man nun auch noch den HBM-Speicher hinzu, entspräche dies sieben Technologien, die hier zusammenkommen. Als letzter Punkt könnte aber auch der Omni-Directional Interconnect (ODI) gemeint sein, den Intel in verschiedenen Umsetzungen im Package verwendet.

Einsatz von Ponte Vecchio

Intel will zusammen mit dem U.S. Department of Energy (DOE) in der Nähe von Chicago das erste ExaFLOPS-System in den USA aufbauen. Betrieben werden soll das System vom Argonne National Laboratory. Das Besondere am Aurora-Supercomputer: Alle wichtigen Komponenten sollten von Intel stammen. Dies betrifft besonders die Prozessoren (Xeon Scalable der 4. Generation, Sapphire Rapids) und die GPU-Beschleuniger (Ponte Vecchio, Xe-HPC). Auch Intels Optane DC Persistent Memory soll zum Einsatz kommen.

Ursprünglich sollte der Supercomputer 2021 aufgebaut werden. Doch aufgrund der Probleme in der Fertigung und der allgemeinen Lage dürfte dieser Termin nicht zu halten sein.

Update:

Raja Koduri hat noch einmal nachgelegt und liefert zusätzliche Informationen.

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

So hat man den Xe-HPC-Chip offenbar tatsächlich funktionstüchtig testen können. Den "Hello World"-Moment hat man in Form eines Mandelbrot-Fraktals zelebriert, welches der Chip berechnet hat. Koduri liefert zudem die Information, dass sich 41 aktive Chiplets im Package befinden. Zählt man die insgesamt erkennbaren einzelnen Chips, kommt man auf zweimal 25, so dass es neun inaktive Chips bzw. Komponenten geben müsste.