Werbung

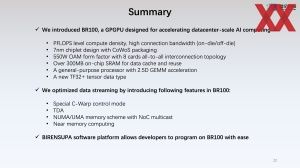

Auf der Hotchips stellte das chinesische Unternehmen Biren die BR100-GPU vor, die für AI-Anwendungen vorgehen ist und die im eigentliche Sinne gar keine GPU im Hinblick auf eine Graphics Processing Unit mehr ist, denn Grafik kann die BR100-GPU gar nicht mehr ausgeben. Die Abkürzung GPU darf hier eher als General Processing Unit verstanden werden.

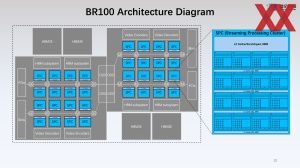

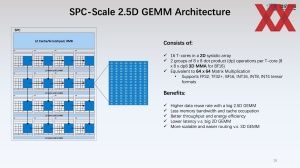

Bei der BR100-GPU handelt es sich um ein Chiplet-Design, bestehend aus zwei Chips mit jeweils zwei HBM2E-Speicherchips. Insgesamt kommt der Chip auf eine Größe von 1.074 mm² und auf 77 Milliarden Transistoren. Gefertigt wird er in 7 nm – mutmaßlich bei TSMC, auch wenn dies nicht explizit erwähnt wird. Der HBM2E-Speicherausbau beläuft sich auf 64 GB. Die Kommunikation zwischen den beiden Chips findet über ein BLink getauftes Interface statt, welches 896 GB/s erreichen soll. Bei der Radeon Instinct MI250X sprechen die beiden Chips im Package über ein Interface mit 800 GB/s. Auch hier ist die BR100-GPU also auf Niveau der Konkurrenz.

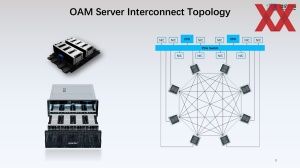

Im OAM-Format, wie es für das Datacenter vorgesehen ist, genehmigt sich die BR100-GPU eine Leistungsaufnahme von maximal 550 W. Bis zu acht BR100-Chips können direkt miteinander angebunden werden und kommunizieren per PCI-Express 5.0 mit dem Host-System. Es ist aber auch eine abgespeckte Variante BR104 vorgestellt worden, die auf PCI-Express-Karten eingesetzt werden soll. Hier befindet sich nur ein Chip im Package.

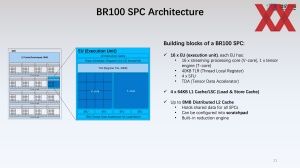

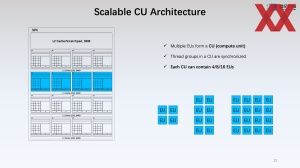

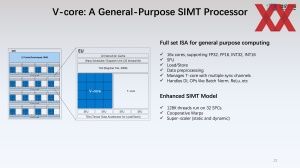

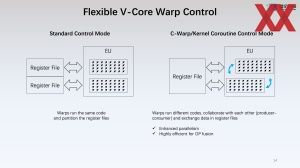

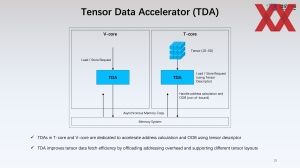

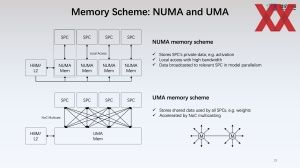

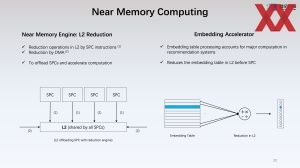

Die GPU besteht aus 16 SPCs (Streaming Processing Cluster) und diese wiederum aus 16 EUs (Execution Units). Jede EU wiederum besteht aus 16 V-Cores (Streaming Processing Core) und einer Tensor Engine (T-Core). 4x 64 KB an L1-Cache und LSC (Road & Store Cache) stehen diesen Funktionseinheiten zur Verfügung. Hinzu kommen bis zu 8 MB an L2-Cache.

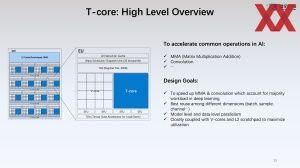

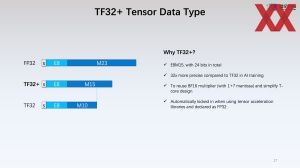

Der V-Core ist ein General-Purpose SIMT Prozessor, der FP32, FP16, INT32 und INT16 unterstützt. Ein FP64 kann die GPU nicht verarbeiten und dazu ist sie auch nicht vorgesehen. Der T-Core ist für MMA (Matrix Multiplikation Addition), also Matrix-Berechnungen, vorgesehen. Die T-Cores können 64x64 Matrix-Multiplikationen durchführen und unterstützen die Datenformate FP32, TF32, BF16, INT16, INT8 und INT4.

Schaut man sich die von Biren veröffentlichten Leistungsdaten zur BR100-GPU an, so werden hier 256 TFLOPS für FP32-Berechnungen genannt. Intels Ponte Vecchio soll über die Xe-Cores auf 52 TFLOPS kommen, NVIDIAs H100 auf 60 TFLOPS. 1.024 TFLOPS für BF16 gibt Biren an, bei Intel und NVIDIA sind es 839 bzw. knapp 2.000 TFLOPS. Das immer wichtigere INT8-Format in den Matrix-Berechnungen erledigten Intel und NVIDIA mit etwa 1.600 und 4.000 TFLOPS – beim BR100 sollen es 2.048 TFLOPS sein.

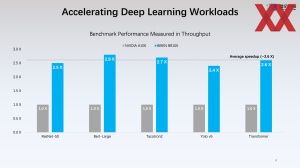

Aus technischer Sicht ist die BR100-GPU von Biren extrem interessant. 2x 537 mm² zusammen mit 4x HBM2E im CoWoS-Package. Dazu 300 MB an SRAM auf dem Chip und vieles mehr sind imposante Eckdaten einer Neuentwicklung, die vor drei Jahren gestartet wurde. Erste Vergleichsdaten mit NVIDIAs A100 liefert der Hersteller. Aber auch hier gilt, dass bei Verfügbarkeit des BR100-Beschleunigers der H100-Beschleuniger das Gegenstück sein wird und man sich auch gegen Intels Ponte Vecchio sowie AMDs Radeon Instinct MI250X vergleichen muss. Unabhängige Benchmarks werden aber sicherlich in Kürze aufzeigen, was in der BR100-GPU steckt.