News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

Hotchips

-

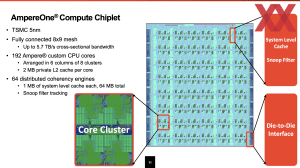

5 nm, HBM3E und aufwändiges Packaging: Hersteller protzen mit High-End-Chips

Nicht kleckern, sondern klotzen – so könnte das Motto der diesjährigen Hot-Chips-Konferenz lauten. Die Hersteller überbieten sich mit immer größeren und letztendlich auch schnelleren Chips, doch der Aufwand der betrieben wird ist ebenfalls enorm. Über NVIDIAs Blackwell-GPU haben wir ebenfalls bereits berichtet wie über den Telum II von IBM, der mit gigantischen Caches aufwarten kann. Auch Intels Xeon 6 SoC alias Granite Rapids-D ist mit zwei... [mehr]

Nicht kleckern, sondern klotzen – so könnte das Motto der diesjährigen Hot-Chips-Konferenz lauten. Die Hersteller überbieten sich mit immer größeren und letztendlich auch schnelleren Chips, doch der Aufwand der betrieben wird ist ebenfalls enorm. Über NVIDIAs Blackwell-GPU haben wir ebenfalls bereits berichtet wie über den Telum II von IBM, der mit gigantischen Caches aufwarten kann. Auch Intels Xeon 6 SoC alias Granite Rapids-D ist mit zwei... [mehr] -

NVIDIA Blackwell: Neue Datenformate sorgen für mehr Leistung in den Tensor-Kernen

Im Vorfeld der Hot Chips 2024 sprach NVIDIA bereits über die Blackwell-Infrastruktur in Form des NVLink-Interconnects und der dazugehörigen Switches. Auf der Konferenz selbst verriet NVIDIA etwas mehr zur Blackwell-Architektur bzw. der darin verbauten Tensor-Kerne. Diese können zwar weiterhin auch große Matrizen in einem Durchlauf berechnen, mit Hilfe neuer Datenformate wird der Durchsatz aber deutlich erhöht. Durch ein neues... [mehr]

Im Vorfeld der Hot Chips 2024 sprach NVIDIA bereits über die Blackwell-Infrastruktur in Form des NVLink-Interconnects und der dazugehörigen Switches. Auf der Konferenz selbst verriet NVIDIA etwas mehr zur Blackwell-Architektur bzw. der darin verbauten Tensor-Kerne. Diese können zwar weiterhin auch große Matrizen in einem Durchlauf berechnen, mit Hilfe neuer Datenformate wird der Durchsatz aber deutlich erhöht. Durch ein neues... [mehr] -

Granite Rapids-D: Intel spricht über den Xeon-6-SoC

Bereits im Februar dieses Jahres nannte Intel erstmals eine Network- und Edge-Variante der Xeon-6-Prozessoren. Granite Ridge-D verwendet dabei Performance-Kerne und kombiniert diese mit einer schnellen Ethernet-Anbindung, PCIe/CXL-Lanes und den bekannten Beschleunigern. Es wird der dritte und letzte Schritt in der Xeon-6-Strategie sein, die im zweiten Quartal mit der Xeon-6700E-Serie (Xeon 6E, Siera Forrest-SP), bzw. den kleinsten... [mehr]

Bereits im Februar dieses Jahres nannte Intel erstmals eine Network- und Edge-Variante der Xeon-6-Prozessoren. Granite Ridge-D verwendet dabei Performance-Kerne und kombiniert diese mit einer schnellen Ethernet-Anbindung, PCIe/CXL-Lanes und den bekannten Beschleunigern. Es wird der dritte und letzte Schritt in der Xeon-6-Strategie sein, die im zweiten Quartal mit der Xeon-6700E-Serie (Xeon 6E, Siera Forrest-SP), bzw. den kleinsten... [mehr] -

Hohe Cache-Kapazitäten und Verfügbarkeit: Details zum IBM Telum II

Ähnlich wie im Sommer 2022 zum Telum der ersten Generation hat IBM auf der Hot-Chips-Konferenz in diesem Jahr nun den Telum II vorgestellt. Bei den Prozessoren und den dazugehörigen Systemen von IBM geht es um höchste Verfügbarkeit und möglichst geringe Latenzen. Der Telum II bietet acht Kerne bei einem Takt von 5,5 GHz. Hinzu kommen eine DPU (Data Processing Unit) mit vier Clustern mit jeweils acht Microcontroller-Kernen mit jeweils 64... [mehr]

Ähnlich wie im Sommer 2022 zum Telum der ersten Generation hat IBM auf der Hot-Chips-Konferenz in diesem Jahr nun den Telum II vorgestellt. Bei den Prozessoren und den dazugehörigen Systemen von IBM geht es um höchste Verfügbarkeit und möglichst geringe Latenzen. Der Telum II bietet acht Kerne bei einem Takt von 5,5 GHz. Hinzu kommen eine DPU (Data Processing Unit) mit vier Clustern mit jeweils acht Microcontroller-Kernen mit jeweils 64... [mehr] -

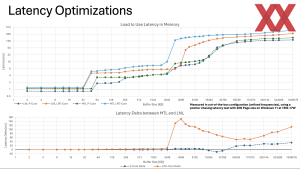

Intel Lunar Lake: Details zu den Kern- und Cache-Latenzen

Auf einer eigenen Intel Tech Tour präsentierte der Chipriese die bisherigen Details zu den kommenden Lunar-Lake-Prozessoren. Durch das Packaging, die Fertigung bei TSMC, neue Performance- und Efficiency-Kerne und die neue Xe2-GPU ist Lunar Lake ein äußerst interessantes Design. Auf der aktuellen Hot-Chips-Konferenz hat Intel einige weitere Details präsentiert. Diese beziehen sich vor allem auf die Latenzen des Caches sowie von Kern zu Kern... [mehr].

Auf einer eigenen Intel Tech Tour präsentierte der Chipriese die bisherigen Details zu den kommenden Lunar-Lake-Prozessoren. Durch das Packaging, die Fertigung bei TSMC, neue Performance- und Efficiency-Kerne und die neue Xe2-GPU ist Lunar Lake ein äußerst interessantes Design. Auf der aktuellen Hot-Chips-Konferenz hat Intel einige weitere Details präsentiert. Diese beziehen sich vor allem auf die Latenzen des Caches sowie von Kern zu Kern... [mehr]. -

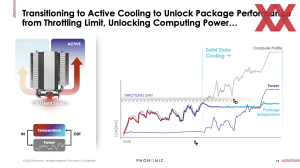

Exotische Kühllösungen: Frore entwickelt LiquidJet, Phononics will Peltier-Elemente einsetzen

Vor dem ersten offiziellen Tag der Konferenz am heutigen Montag gab es gestern bereits einige Tutorial-Sessions, die sich in zwei Themengebiete aufteilten: LLMs für die Entwicklung von Chips und Kühlung der immer leistungsfähigeren und leistungshungrigen Chips. NVIDIA setzt wegen der immer kürzeren Zeiträume zwischen den GPU-Generationen und den Vorteilen in der Effizienz bereits auf LLMs in der Chipentwicklung (siehe ChipNeMo). Dies ist für... [mehr]

Vor dem ersten offiziellen Tag der Konferenz am heutigen Montag gab es gestern bereits einige Tutorial-Sessions, die sich in zwei Themengebiete aufteilten: LLMs für die Entwicklung von Chips und Kühlung der immer leistungsfähigeren und leistungshungrigen Chips. NVIDIA setzt wegen der immer kürzeren Zeiträume zwischen den GPU-Generationen und den Vorteilen in der Effizienz bereits auf LLMs in der Chipentwicklung (siehe ChipNeMo). Dies ist für... [mehr] -

Zukünftige AI-Hardware: Blackwell und Blackwell NVLink Switch im Einsatz

Zur Hot-Chips-Konferenz 2024 spricht NVIDIA über einige weitere Details seiner Blackwell-Generation der KI-Beschleuniger, bzw. die dazugehörige Netzwerk-Hardware. Zunächst einmal gab es in den vergangenen Monaten immer wieder Gerüchte zu einer Verschiebung von Blackwell im Datacenter und tatsächlich musste NVIDIA eine neue Revision des Chips, bzw. Package auflegen, was einen Neustart in der Fertigung bei TSMC nach sich gezogen hat. Davon... [mehr]

Zur Hot-Chips-Konferenz 2024 spricht NVIDIA über einige weitere Details seiner Blackwell-Generation der KI-Beschleuniger, bzw. die dazugehörige Netzwerk-Hardware. Zunächst einmal gab es in den vergangenen Monaten immer wieder Gerüchte zu einer Verschiebung von Blackwell im Datacenter und tatsächlich musste NVIDIA eine neue Revision des Chips, bzw. Package auflegen, was einen Neustart in der Fertigung bei TSMC nach sich gezogen hat. Davon... [mehr] -

Sierra Forest und Granite Rapids: Intel spricht über P- und E-Kern-Xeons

Auf der HotChips 2023 hat Intel über seine kommende Plattform namens Birch Stream gesprochen, die ab dem kommenden Jahr mit dem E-Kern-Xeon Sierra Forest und P-Kern-Xeon Granite Rapids ihre Premiere feiern wird. Die Aufspaltung in E- und P-Kern-Xeons soll Intel dabei helfen die Marktsegmente im Serverumfeld besser abzudecken. Angekündet hat man diesen Schritt bereits vor einigen Monaten. Mitte Juni stellte AMD mit dem Bergamo-Designs seine... [mehr]

Auf der HotChips 2023 hat Intel über seine kommende Plattform namens Birch Stream gesprochen, die ab dem kommenden Jahr mit dem E-Kern-Xeon Sierra Forest und P-Kern-Xeon Granite Rapids ihre Premiere feiern wird. Die Aufspaltung in E- und P-Kern-Xeons soll Intel dabei helfen die Marktsegmente im Serverumfeld besser abzudecken. Angekündet hat man diesen Schritt bereits vor einigen Monaten. Mitte Juni stellte AMD mit dem Bergamo-Designs seine... [mehr] -

IBM Research NorthPole: KI-Beschleuniger soll alle in den Schatten stellen

Aktuell dominiert NVIDIA den Hardwaremarkt, wenn es um das Thema Generative AI geht. 10 Milliarden US-Dollar Umsatz alleine durch die Datancenter-Sparte sprechen eine deutlich Sprache. Es gibt aber auch Punkte, durch die sich andere Hersteller absetzen wollen. Hier kommt vor allem die Effizienz in den Fokus. IBM Research hat auf der HotChips den KI-Beschleuniger NorthPole vorgestellt. Der Trend ist klar: Viele kleine Beschleuniger... [mehr]

Aktuell dominiert NVIDIA den Hardwaremarkt, wenn es um das Thema Generative AI geht. 10 Milliarden US-Dollar Umsatz alleine durch die Datancenter-Sparte sprechen eine deutlich Sprache. Es gibt aber auch Punkte, durch die sich andere Hersteller absetzen wollen. Hier kommt vor allem die Effizienz in den Fokus. IBM Research hat auf der HotChips den KI-Beschleuniger NorthPole vorgestellt. Der Trend ist klar: Viele kleine Beschleuniger... [mehr] -

Mesh-to-Mesh Optical-Fabric-Testchip: 66 Threads pro Kern für viele Daten

Für Desktop- und Serveranwendungen hat sich das gleichzeitige Ausführen von zwei Threads pro Kern etabliert, um die Hardwareressourcen bestmöglich auszunutzen. Für einer besser vorhersehbare Leistung und auch aus Sicherheitsgründen verzichten einige Hardware- und Cloud-Anbieter aber auch auf ein Hyper-Threading bzw. SMT (Simultaneous Multithreading). Für Spezialanwendungen gibt es aber auch Hardware, die vier oder gar acht Threads... [mehr]

Für Desktop- und Serveranwendungen hat sich das gleichzeitige Ausführen von zwei Threads pro Kern etabliert, um die Hardwareressourcen bestmöglich auszunutzen. Für einer besser vorhersehbare Leistung und auch aus Sicherheitsgründen verzichten einige Hardware- und Cloud-Anbieter aber auch auf ein Hyper-Threading bzw. SMT (Simultaneous Multithreading). Für Spezialanwendungen gibt es aber auch Hardware, die vier oder gar acht Threads... [mehr] -

Effizientere Strukturen: FABRIC8LABS druckt komplizierte Oberflächen für bessere Kühlung

Aufgrund der enormen Leistungsdichte ist an einen luftgekühlten HPC-Supercomputer und entsprechend kleinere Cluster in den Rechenzentren nicht mehr zu denken. GPUs und Beschleuniger kommen heute schon an 700 bis 800 W heran, bei den Prozessoren sind 350 W und mehr keine Seltenheit mehr. In den kommenden Jahren soll die Leistungsdichte weiter steigen, Prozessoren und Beschleuniger entsprechend noch mehr verbrauchen. Doch irgendwann komm auch... [mehr]

Aufgrund der enormen Leistungsdichte ist an einen luftgekühlten HPC-Supercomputer und entsprechend kleinere Cluster in den Rechenzentren nicht mehr zu denken. GPUs und Beschleuniger kommen heute schon an 700 bis 800 W heran, bei den Prozessoren sind 350 W und mehr keine Seltenheit mehr. In den kommenden Jahren soll die Leistungsdichte weiter steigen, Prozessoren und Beschleuniger entsprechend noch mehr verbrauchen. Doch irgendwann komm auch... [mehr] -

Von NVIDIA genutzt: ARM nennt mehr Details zum Neoverse V2

Einige Details zum High-Performance-Neoverse-Design namens V2 gab es bereits. Neoverse V2 trägt den Codenamen Demeter und basiert wiederum auf der Armv9-Erweiterung des AArch64-Instruction-Sets. Für das Neoverse-V2-Design sieht ARM bis zu 256 Kerne vor. Bereits gemutmaßt wurde, dass NVIDIA für seinen Grace CPU Superchip und Grace Hopper Superchip auf das Neoverse-V2-Design setzt, was sich nun auch bestätigt. Ein tiefes Front-End und... [mehr]

Einige Details zum High-Performance-Neoverse-Design namens V2 gab es bereits. Neoverse V2 trägt den Codenamen Demeter und basiert wiederum auf der Armv9-Erweiterung des AArch64-Instruction-Sets. Für das Neoverse-V2-Design sieht ARM bis zu 256 Kerne vor. Bereits gemutmaßt wurde, dass NVIDIA für seinen Grace CPU Superchip und Grace Hopper Superchip auf das Neoverse-V2-Design setzt, was sich nun auch bestätigt. Ein tiefes Front-End und... [mehr] -

Sk hynix und Samsung: Speicher mit In-Memory-AI wird konkreter

Sk hynix und Samsung arbeiten bereits seit geraumer Zeit daran, den Speicher und den AI-Beschleuniger dichter zusammen zu bringen. Bei Sk hynix nennt sich die entsprechende Technologie AiM (Accelerator in Memory), bei Samsung Processing-in-Memory (PIM). Beide Ansätze sind nicht neu, rücken auf der diesjährigen HotChips 2023 aber näher an einen möglichen Praxiseinsatz. So sieht Sk hynix zu einem GDDR6-AiM einen Prototypen vor,... [mehr]

Sk hynix und Samsung arbeiten bereits seit geraumer Zeit daran, den Speicher und den AI-Beschleuniger dichter zusammen zu bringen. Bei Sk hynix nennt sich die entsprechende Technologie AiM (Accelerator in Memory), bei Samsung Processing-in-Memory (PIM). Beide Ansätze sind nicht neu, rücken auf der diesjährigen HotChips 2023 aber näher an einen möglichen Praxiseinsatz. So sieht Sk hynix zu einem GDDR6-AiM einen Prototypen vor,... [mehr] -

ARM CSS N2: Schnellere Entwicklung und geringere Kosten

Einen Prozessor zu entwickeln setzt einerseits eine gewisse Expertise voraus, man benötigt aber auch die entsprechenden Kompetenzen und Lizenzen. Kosten und die für die Entwicklung notwendige Zeit sind ein wichtiger Faktor. Mehrere hundert Millionen Euro an Entwicklungskosten fallen für ein modernes Design an. ARM bietet über sein Lizenzmodell zumindest schon einmal die Möglichkeit, ein Design eines CPU-Kerns verwenden zu dürfen. Die... [mehr]

Einen Prozessor zu entwickeln setzt einerseits eine gewisse Expertise voraus, man benötigt aber auch die entsprechenden Kompetenzen und Lizenzen. Kosten und die für die Entwicklung notwendige Zeit sind ein wichtiger Faktor. Mehrere hundert Millionen Euro an Entwicklungskosten fallen für ein modernes Design an. ARM bietet über sein Lizenzmodell zumindest schon einmal die Möglichkeit, ein Design eines CPU-Kerns verwenden zu dürfen. Die... [mehr] -

Für Telco-Anwendungen: AMD nennt weitere Details zur Siena-CPU

Auf der diesjährigen HotChips-Konferenz präsentierte AMD weitere Details zum Telco-Spezialmodell der aktuellen Zen-4-Serie: Dem EPYC Siena. Die Prozessoren sollen als EPYC-8004-Serie auf den Markt kommen und ergänzen die aktuelle Produktpalette bestehend aus Genoa (General Purpose EPYC), Bergamo (Cloud Native EPYC) und Genoa-X (HPC/Technical EPYC mit 3D V-Cache). Mal bis zu 96 Kerne mit jeweils 32 MB für einen Core Complex, mal bis zu 128... [mehr]

Auf der diesjährigen HotChips-Konferenz präsentierte AMD weitere Details zum Telco-Spezialmodell der aktuellen Zen-4-Serie: Dem EPYC Siena. Die Prozessoren sollen als EPYC-8004-Serie auf den Markt kommen und ergänzen die aktuelle Produktpalette bestehend aus Genoa (General Purpose EPYC), Bergamo (Cloud Native EPYC) und Genoa-X (HPC/Technical EPYC mit 3D V-Cache). Mal bis zu 96 Kerne mit jeweils 32 MB für einen Core Complex, mal bis zu 128... [mehr] -

Hotchips 34: Biren BR100-GPU ohne Graphics und ohne FP64

Auf der Hotchips stellte das chinesische Unternehmen Biren die BR100-GPU vor, die für AI-Anwendungen vorgehen ist und die im eigentliche Sinne gar keine GPU im Hinblick auf eine Graphics Processing Unit mehr ist, denn Grafik kann die BR100-GPU gar nicht mehr ausgeben. Die Abkürzung GPU darf hier eher als General Processing Unit verstanden werden. Bei der BR100-GPU handelt es sich um ein Chiplet-Design, bestehend aus zwei Chips mit jeweils zwei... [mehr]

Auf der Hotchips stellte das chinesische Unternehmen Biren die BR100-GPU vor, die für AI-Anwendungen vorgehen ist und die im eigentliche Sinne gar keine GPU im Hinblick auf eine Graphics Processing Unit mehr ist, denn Grafik kann die BR100-GPU gar nicht mehr ausgeben. Die Abkürzung GPU darf hier eher als General Processing Unit verstanden werden. Bei der BR100-GPU handelt es sich um ein Chiplet-Design, bestehend aus zwei Chips mit jeweils zwei... [mehr] -

Hotchips 34: NVIDIA nennt Details zum Cache und Speicher des Grace-Superchips

In diesem Frühjahr stellte NVIDIA seinen ersten ARM-Supercomputer/Server-Chip Grace offiziell vor. Die Grace-CPU verwendet 72 ARM-Kerne und bietet zudem 32 Speicherkanäle für LPDDR5X-Speicher. Die Kapazität des Speichers beläuft sich auf 512 GB und die Speicherbandbreite liegt bei 546 GB/s. Auf der Hotchips 34 spricht NVIDIA über Grace, den Grace CPU Superchip (2x Grace CPU) und auch den Grace Hopper Superchip, bei dem eine Grace-CPU... [mehr]

In diesem Frühjahr stellte NVIDIA seinen ersten ARM-Supercomputer/Server-Chip Grace offiziell vor. Die Grace-CPU verwendet 72 ARM-Kerne und bietet zudem 32 Speicherkanäle für LPDDR5X-Speicher. Die Kapazität des Speichers beläuft sich auf 512 GB und die Speicherbandbreite liegt bei 546 GB/s. Auf der Hotchips 34 spricht NVIDIA über Grace, den Grace CPU Superchip (2x Grace CPU) und auch den Grace Hopper Superchip, bei dem eine Grace-CPU... [mehr] -

HotChips32: AMD gibt Ausblick auf RDNA 2 mit Raytracing-Beschleunigung

Auf der HotChips-Konferenz hat Microsoft die System Architecture der Xbox Series X vorgestellt. Fast alle technischen Daten des Custom-SoCs, den man gemeinsam mit AMD entwickelt hat, kennen wir bereits. Für uns besonders interessant ist das, was man über die verbaute GPU-Architektur verraten hat, denn die acht Zen-2-Kerne kennen wir bereits von den Desktop- und Mobile-Prozessoren. Die verbaute GPU unterstützt ein Sampler Feedback... [mehr]

Auf der HotChips-Konferenz hat Microsoft die System Architecture der Xbox Series X vorgestellt. Fast alle technischen Daten des Custom-SoCs, den man gemeinsam mit AMD entwickelt hat, kennen wir bereits. Für uns besonders interessant ist das, was man über die verbaute GPU-Architektur verraten hat, denn die acht Zen-2-Kerne kennen wir bereits von den Desktop- und Mobile-Prozessoren. Die verbaute GPU unterstützt ein Sampler Feedback... [mehr]