Werbung

Wie die aktuellen Roadmaps zu AMDs Desktop- und Notebook-Plattformen zeigen, soll das Jahr 2011 nicht nur den 32-nm-Fertigungsprozess für den Endkundenmarkt einläuten, sondern auch neue Chip-Architekturen mit sich bringen. Auf dem gestrigen Financial Analyst Day 2009 hat AMD nun erste Details zu den Mikroprozessoren der nächsten Generation bekannt gegeben. Darunter sind die CPUs mit den Codenamen Bulldozer und Bobcat, über die schon viel spekuliert wurde. Außerdem stellte AMD die Accelerated Processing Unit (APU) vor, eine Kombination aus CPU und GPU, die als der Inbegriff der "Fusion"-Kampagne bezeichnet werden kann.

Die Erwartungen der AMD-Fangemeinde an die Bulldozer-Architektur sind groß. Man erhofft sich, endlich wieder Intel bei der CPU-Leistung im High-End-Segment Paroli bieten zu können oder gar die Performance-Krone zurückzuerobern. Bulldozer wird im bewährten "Silicon On Insulator"-Verfahren (SOI) gefertigt, dass AMD seit Jahren verwendet. Jedoch kombiniert man nun dieses erstmals mit der "High-K Metal Gate"-Technologie, die Konkurrent Intel schon seit längerem einsetzt. Dadurch lassen sich theoretisch die Leistungsaufnahme und die internen Schaltzeiten erheblich reduzieren. Den grundlegenden Aufbau des Bulldozer-Chips zeigt AMD nun in Form von schematischen Grafiken.

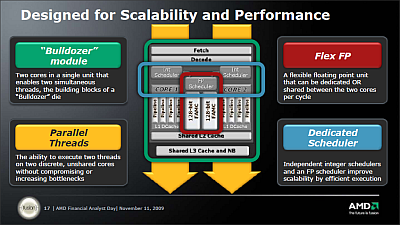

Bei der Entwicklung der CPU legte man großen Wert auf eine weitgehende Skalierbarkeit der Systeme, was man durch die Kombination von einer unterschiedlichen Anzahl an Bulldozer-Modulen auf einem DIE erreichen will. Auch die Energieeffizienz steht im Vordergrund, die man unter anderem durch neue Power-Management-Funktionen steigern will. Im Grunde besteht ein solcher Bulldozer-"Baustein" aus zwei eng beieinander liegenden Kernen, die sich Ressourcen teilen. Der Level-2-Cache ist somit nicht wie bei der aktuellen Stars-Architektur exklusiv für einen Kern reserviert (dedicated), sondern für beide Kerne zugängig (shared). Jeder der zwei Kerne besitzt eine Integer-Einheit mit vier Pipelines, dem L1-Data-Cache und einem unabhängigen Int-Scheduler. Außerdem steht eine doppelte 128-Bit-Floating-Point-Einheit mit eigenem, unabhängigen FP-Scheduler zur Verfügung, die mit ISA-Extensions wie FP "FMAC" umgehen kann und auch die Befehlssatzerweiterung SSE5 ermöglichen soll. Die Floating-Point-Unit (FPU) soll dabei flexibel sein und pro Takt entweder einem Kern (dedicated) oder beiden Kernen (shared) zugeordnet werden können. Die Northbridge und der geteilte L3-Cache werden wie beim Vorgänger (K10) für alle Kerne zuständig sein. Weiterhin stehen jeweils eine Fetch-Einheit und ein Decoder pro Modul zur Verfügung. Ein Bulldozer-Modul ist also in der Lage, dank der beiden eigenständigen Kerne, zwei simultane Threads auszuführen.

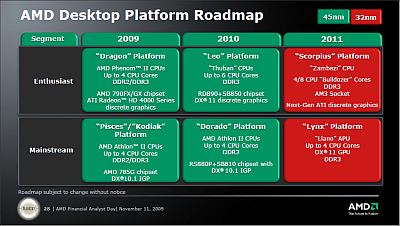

Wie die aktuelle Desktop-Roadmap zeigt, wird Zambezi die erste Bulldozer-CPU für den Endkundenmarkt sein und über vier bis acht Kerne verfügen, dabei ist aber noch unklar, ob es sich bei der genannten Anzahl um vollständige Bulldozer-Module (2 Cores) handelt, was die Anzahl an Threads verdoppeln würde, oder die Gesamtzahl an Kernen bereits einberechnet ist. Auch im Serverbereich soll Bulldozer 2011 als Teil der Interlagos- und Valencia-Plattform seinen Dienst verrichten.

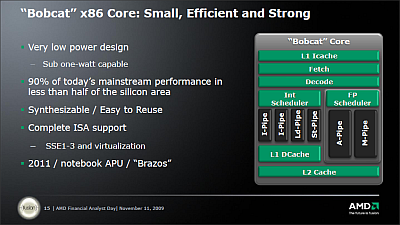

Während bei Bulldozer die Performance und Skalierbarkeit im Vordergrund stehen, sollen bei Bobcat eine geringe Leistungsaufnahme, geringe Kosten und Flexibilität vorwiegen. Als Zielgruppe sieht man nicht nur Low-Power-Geräte, sondern auch Cloud-Computing-Systeme. Ein Bobcat-Core soll in der Lage sein, weniger als ein Watt Leistung zu benötigen. Er verfügt über eine Fetch-Einheit, einen Decoder und den L1-Instruction-Cache sowie den dedizierten L2-Cache. Für Integerberechnungen stehen vier Pipes zur Verfügung mit verschiedenen Aufgaben. Ein Scheduler und der L1-Data-Cache vervollständigen die Integer-Einheit. Für Gleitkommaberechnungen ist die FPU mit zwei Pipes und einem Scheduler zuständig. Bobcat soll 90 Prozent der aktuellen Mainstream-Leistung auf der Hälfte der Silizium-Fläche liefern können. Außerdem soll die komplette x86 Instruction Set Architecture (ISA) unterstützt werden, darunter auch SSE 1-3 und Virtualisierung.

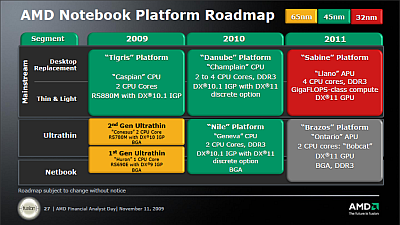

In 2011 soll Bobcat zunächst als Teil der APU Brazos in Notebooks eingesetzt werden.

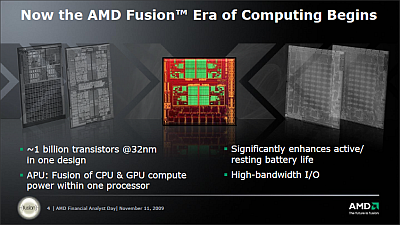

The Future is Fusion, so lautet AMDs Logo zurzeit. Erstmals sollen CPU und GPU zu einer Einheit fusionieren und auf einem DIE verschmelzen. AMD nennt das Ergebnis dieser Vereinigung Accelerated Processing Unit, kurz APU. Im Jahr 2011 sollen die APUs Llano (Desktops/Notebooks) und Brazos (kompakte Notebooks) erscheinen und das Zeitalter des heterogenen Computings erst richtig einläuten. Dabei wird die GPU-Einheit nicht nur für grafische Zwecke benutzt, sondern auch für parallele Berechnungen, bei denen GPUs den CPUs deutlich überlegen sind, Stichwort OpenCL und Direct Computing. Die Fusion-APU soll etwa eine Milliarde Transistoren beinhalten, die in 32 nm gefertigt werden. In der Roadmap, die AMD zuvor in Japan präsentierte war jedoch von 40 nm die Rede, was etwas verwirrt. Neben der GPU-Computing-Power im Tera-Flop-Bereich soll auch eine höhere Batterielaufzeit für mobile Geräte ermöglicht werden. Der CPU-Teil wird auf der Stars-Architektur (K10.5) basieren, die auch in den aktuellen Phenom-Prozessoren zu finden ist. Die GPU soll der DirectX-11-Generation angehören. Einen ersten DIE-Shot - offensichtlich von Llano - zeigen die Präsentationsfolien.

{gallery}/galleries/news/mguensch/amd-analyst-day-2009-bulldozer-bobcat-fusion-apus-gallerie{/gallery}

Erste Samples von Bulldozer, Bobcat und der Fusion-APU will AMD noch in 2010 an Partner ausliefern. Dann dürfte es auch nicht mehr lange dauern bis die ersten Vorab-Tests ihren Weg ins Internet finden, wie so häufig der Fall.

Weiterführende Links: