Werbung

Auf der diesjährigen International-Solid-State-Circuits-Conference äußerte sich AMD ein weiteres mal zur aktuellen Entwicklung der eigenen "Carrizo"- und "Excavator"-Architekturen. In der vergangenen Woche erst tauchten weitere Details zur "Zen"-Architektur auf, die aber weiter in der Zukunft liegt als das, was AMD in den vergangenen Tagen auf der ISSCC präsentierte. Auf der CES Anfang des Jahres zeigte man erste lauffähige "Carrizo"-Systeme und verkündete gleichzeitig, dass entsprechende Prozessoren ausschließlich für mobile Geräte vorgesehen sind. "Carrizo" wird damit die erste APU, die ausschließlich im mobilen Bereich eingesetzt und daher auch verstärkt in dieser Richtung optimiert wird.

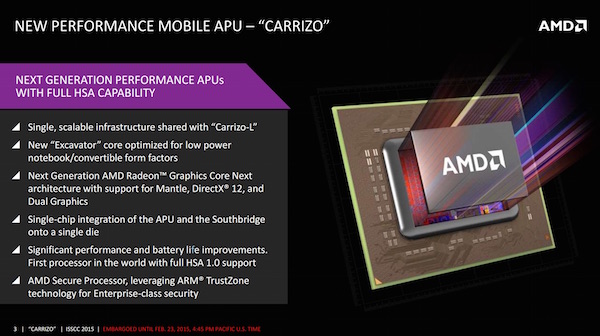

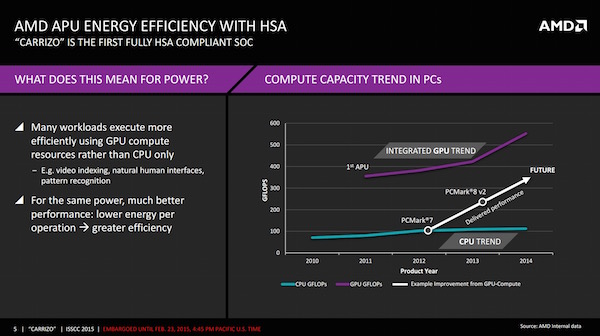

"Carrizo" vereint ein paar Hardware-Module mit "Exavator"-Kernen, eine aktuelle GCN-GPU sowie einen Chipsatz in einem einzigen Package. Als erster SoC bietet "Carrizo" damit HSA, Mantle, TrueAudio und ARM Trustzone. Gefertigt werden wird er von Global Foundries im 28nm-Super-High-Performance-(28SHP)-Prozess. Die Auslegung auf das mobile Segment wird durch die Optimierungen auf einen niedrigen Stromverbrauch der "Excavator"-Kerne deutlich. Interessant ist dabei folgender Punkt: "Single-chip integration of the APU and the Southbridge onto a single die". Erstmals bringt AMD also auch die Southbridge im selben Package wie die restlichen Komponenten unter. Dabei geht AMD aber noch viel weiter und integriert die Funktionen der Southbridge direkt in der APU. Da die entsprechenden Komponenten nun nicht mehr in 65 oder 45 nm in einem extra Chip zu finden sind, sondern ebenfalls als Teil der APU in 28 nm gefertigt werden, kann AMD den Stromverbrauch natürlich deutlich reduzieren. Allerdings erkauft man sich die Integration in Teilen auch durch die Tatsache, dass der Verbrauch der Southbridge-Funktionen mit in die APU eingebracht wird.

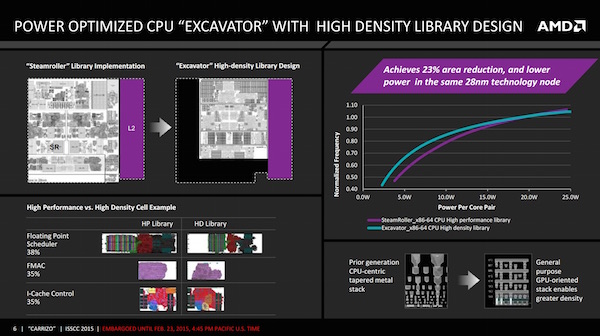

AMD versuchte also in der Folge sowohl Platz auf dem Die als auch den Verbrauch der übrigen Komponenten zu reduzieren. Daraufhin ausgelegt sind wie erwähnt die "Excavator"-Kerne. Einige wichtige Controller für die CPU-Kerne wurden neu organisiert und angeordnet, so dass sie im 28-nm-Prozess weniger Platz benötigen und auch weniger verbrauchen. Offenbar hat sich das Ingenieur-Team hier von den Kollegen aus dem GPU-Departement inspirieren lassen.

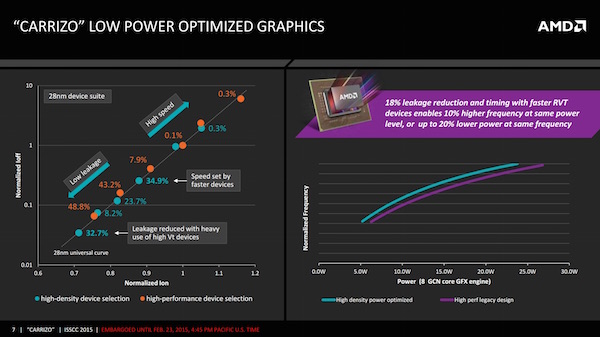

Auswirkungen sind aber auch im GPU-Segment zu erkennen, welches mit vollen acht GCN-Kernen auf 20 Watt gedrosselt wurde. Möglich wird dies durch eine Reduzierung der Leckströme bei höheren Spannungen. Im Vergleich zu "Kaveri", dessen GPU-Part ebenfalls auf 20 Watt ausgelegt ist, steigt die Anzahl der GCN-Kerne von sechs auf eben acht.

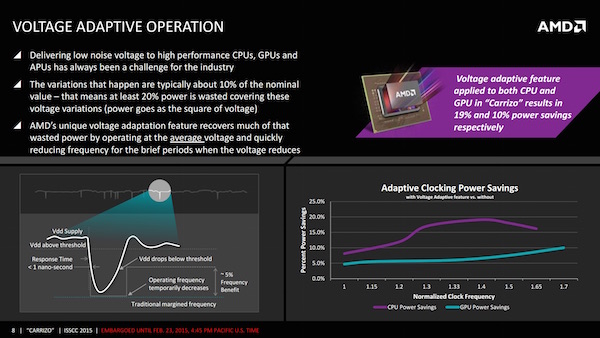

Das Powermanagement ist ein wichtiger Bestandteil der Einsparungen und hat einen maßgeblichen Einfluss darauf. AMD verwendet hier die sogenannten Voltage Adaptive Operation. Dabei wird die Spannung so stabil und ohne großes Rauschen gehalten. Das Rauschlevel liebt üblicherweise bei zehn Prozent, was auch bedeutet, dass recht viel Spannung und damit elektrische Leistung dafür aufgewendet wird, damit die Spannung über einem bestimmten Level bleibt. Das neue CPU-Design arbeitet auch in kleinen Spannungsabfällen des Rauschens weiter und reduziert nur kurz die Taktfrequenz. Die durchschnittliche Spannung kann so reduziert werden, ohne dass große Leistungseinbußen zu befürchten sind. Laut AMD lässt sich die Leistungsaufnahme so um 10 bis 20 Prozent reduzieren.

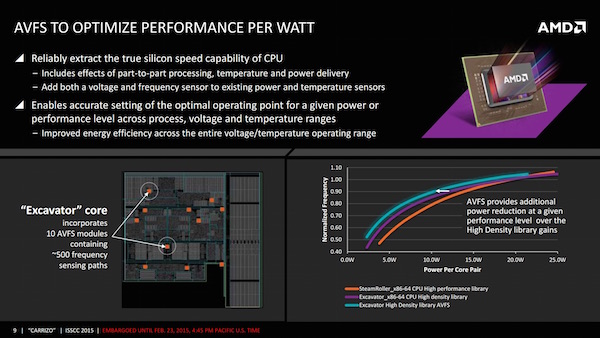

Da die Änderungen der Spannung und Frequenz in Bereich von Nanosekunden stattfinden, musste AMD sich bei der Versorgung der "Excavator"-Kerne etwas neues einfallen lassen. Jeder "Excavator"-Kern besitzt zehn sogenannte Adaptive Voltage-Frequency Scaling Module (AVFS). Diese jeweils zehn Module passen die Spannung und die Taktfrequenz innerhalb der verschiedenen Komponenten des Kerns an. Auch weitere Faktoren, wie die Temperatur, fließen hier mit ein. Bei einem stabilen Verbrauch von zehn Watt spricht AMD von einer um 29 Prozent höheren Taktfrequenz durch diese Maßnahmen. Oder anders gesagt: Soll der Verbrauch konstant auf zehn Watt gehalten werden, kann die Leistungsaufnahme um 40 bis 50 Prozent reduziert werden.

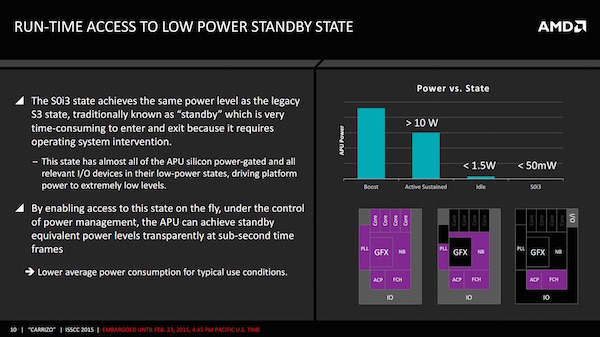

Doch nicht nur ein niedriger Verbrauch der Architektur spielt eine Rolle, sondern auch ein schneller Wechsel zwischen den verschiedenen Betriebszuständen. Die "Excavator"-Kerne können vom S0i3-Power-State, in dem der Kern weniger als 50 mW verbraucht, in die Volllast innerhalb von einer Sekunde wechseln. Dieser schneller Wechsel ermöglicht letztendlich auch einen niedrigeren Idle-Stromverbrauch. Im S0i3-Power-State werden nur noch wenige Komponenten des Prozessors überhaupt mit Strom versorgt, während die übrigen komplett abgeschaltet sind. Auch Stromsparmechanismen wie ein "Inter Frame Power Gating" finden sich in den neuen "Carrizo"-APUs. Dabei wird die GPU einige Zeit abgeschaltet, wenn der Frame Buffer voll ist. Ein Abschalten von nur ein paar Millisekunden spart bereits einen erheblich Teil der Verbrauchs der APU ein.

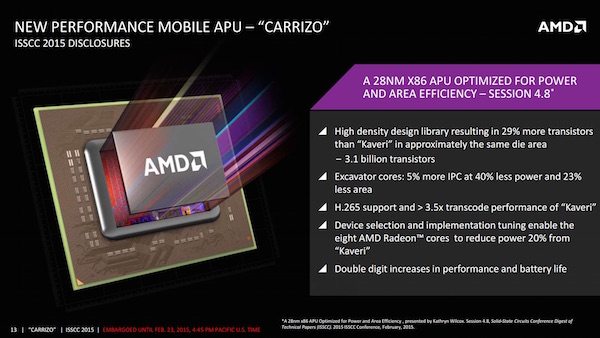

Zum Abschluss nannte AMD noch ein paar technische Daten der Auslegung der "Carrizo"-Prozessoren. So steigt die Anzahl der Transistoren im Vergleich zu "Kaveri" von 2,3 auf 3,1 Milliarden an. Die Die-Fläche aber wägst von 245 mm2 auf gerade einmal 250 mm2. Die in die APU integrierte Southbridge beansprucht 5,5 Prozent der Transistoren, die "Excavator"-Kerne konnten in ihrer Fläche aber um 23 Prozent reduziert werden, so dass wir insgesamt bei einem Transistor-Wachstum von 29 Prozent nur eine geringfügige Vergrößerung der Die-Fläche sehen.

Zusammenfassend erreicht AMD bei einer Reduzierung der Leistungsaufnahme von 40 Prozent ein Performance-Plus von fünf Prozent. Doch eine Leistungssteigerung ist für AMD nicht zwingend das, was mit "Carrizo" vorgesehen ist. Vielmehr geht es um eine höhere Integrationsdichte und das zu erwartende Leistungsplus stellt sich an anderer Stelle dar. So wird "Carrizo" die erste APU sein, die über einen dedizierten H.265-Decoder verfügt. Zudem wird "Carrizo" vollständig HSA-kompatibel sein und auch ein Context-Switching der GPU ermöglichen. HSA wird in zukünftigen Anwendungen eine immer wichtigere Rolle spielen. Derzeit zeigen sich die Vorteile nur in Benchmarks, wie dem PCMark von Futuremark.

AMD plant die Auslieferung erster "Carrizo"-APUs an die Systemhersteller für das zweite Quartal 2015, so dass wir vermutlich auf der Computex Anfang Juni erste marktreife Geräte sehen werden.