Werbung

Erst in der vergangenen Woche gab Intel einigen ausgewählten Journalisten in Portland einen Einblick in den aktuellen Entwicklungsstand der Xeon-Phi-Beschleuniger der "Knights Landing"-Generation. Damals standen die Fertigung in 14-nm-FinFET-Verfahren sowie die Tatsache, dass 8 Milliarden Transistoren im Chip arbeiten im Fokus. Auf dem Intel Developer Forum in Shenzen, China, verriet Intel nun weitere Details.

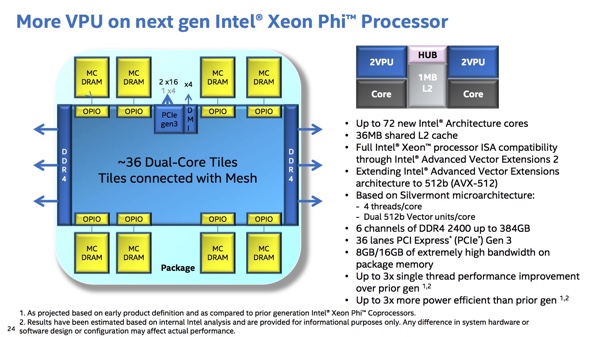

Bisher war bekannt, dass Intel für die F-Version der Xeon-Phi-Beschleunigerchips mindestens 60 Rechenkerne auf Basis der "Silvermont"-Architektur plant. Gerüchten zufolge sollte sich der Maximalausbau auf 72 Kerne belaufen. Diese Angaben wurden nun gemeinsam mit einem 36 MB großen L2-Cache bestätigt. Konkreter wurden auch die Angaben zu den unterschiedlichen Varianten. So wird es die klassische Beschleunigerkarte mit PCI-Express-Interface geben. Geplant sind aber auch mehr oder weniger eigenständig arbeitende Sockel-Varianten, die mit oder ohne Omni Path ausgeliefert werden. Per Omni Path realisiert Intel die Anbindung der Chips untereinander, aber auch mit weiteren Systemkomponenten. Das äußerst komplizierte "Fabric" äußert sich auch in Zahlen bei der Fertigung. So kommt die Xeon-Phi-Variante mit Fabric auf die bereits erwähnten 8 Milliarden Transistoren, während der Chip ohne das Fabric auf "nur" 7,2 Milliarden Transistoren kommt.

In der zweiten Jahreshälfte will Intel die ersten Beschleunigerkarten ausliefern. Später folgen dann auch die gesockelten Varianten. Auf dem IDF in Shenzhen ebenfalls bereits erwähnt wurde der Nachfolger namens "Knights Hill", der aber noch einige Jahre auf sich warten lassen wird. Dort soll dann auch die zweite Generation der Omni-Path-Technologie zum Einsatz kommen und für die Fertigung des Chips plant Intel in 10 nm.

Hintergrund zum Xeon Phi auf Basis von "Knights Landing"

Die Rechenkerne im neuen Xeon Phi basieren auf der klassischen x86-Architektur, genauer gesagt der "Silvermont"-Architektur und können pro Kern vier Threads bearbeiten. Daneben besitzen sie noch AVX512-Einheiten. Im Vergleich zum Einsatz in der "Bail Trail"-Plattform sind aber einige Änderungen vorgenommen worden, die auf den Xeon-Phi-Karten besonders interessant sind. Dazu zählt unter anderem eine andere Cache-Hierarchie. Eine höhere Pack-Dichte im Server will Intel durch die Sockelbarkeit der neuen "Knights Landing"-Xeon-Phi erreichen.

Insgesamt sollen die neuen Xeon-Phi-Beschleuniger auf über 3 TFLOPS Double-Precision-Performance kommen. Zum Vergleich: AMDs FirePro W9100 kommt auf 2,62 TFLOPS und NVIDIAs Tesla K80 erreicht 2,91 TFLOPS. Wichtig ist aber auch der lokal verfügbare Speicher, der 16 GB groß sein soll. Beim Speicher handelt es sich um Hybrid Memory Cubes von Micron, die im gleichen Package untergebraucht sind, wie der Xeon-Phi-Chip. Damit will Intel die Zugriffszeiten auf diesen Speicher reduzieren und zudem die Bandbreite erhöhen. Letztgenannte soll bei 480 GB pro Sekunde liegen, was in etwa 1/3 schneller ist, als das was AMD und NVIDIA derzeit als Anbindung ihrem Grafikspeicher zur Verfügung stellen können.