Werbung

Das IDF 2015 nutzte Intel, um erstmals Details zu ihrer neuen Skylake-Architektur zu präsentieren. Den Test der ersten Prozessoren hatten wir mit dem Core i5-6600K und dem Core i7-6700K bereits online – ungewohnterweise präsentiert Intel aber erst nach diesem ersten, vorgezogenen Launch die Architekturdetails.

Zunächst erklärte Intel die historische Entwicklung von Skylake im Unternehmen, die während der letzten fünf Jahre mehrmals verändert worden ist. Skylake wurde von Intel vor fünf Jahren als Prozessorgeneration für klassische Desktops und Light- und Thin-Notebooks geplant. Damit wurde zunächst an einem klassischen PC I/O-Set gearbeitet, bei welchem die TDP bei den beiden extremsten Produkten um den Faktor 3 auseinanderliegen kann, wie man es von bestehenden Desktop- und Mobile-Parts von Intel kennt. Es waren zunächst zwei Formfaktoren für Notebooks und Desktops geplant.

Dann kamen allerdings die Ultrabooks und 2-in-1-Notebooks – und das Skylake-Team musste ihre Pläne ausweiten. Die Entfernung zwischen dem kleinsten Skylake-Produkt und dem größten High-End-Skylake-Chip liegen nun um den Faktor 20 auseinander. Es gibt vier Formfaktoren und es wurden höhere Anforderungen an die Video- und Multimediafähigkeiten gestellt, die 40-60% weniger SoC-Power benötigen mussten.

Das Team arbeitete also neben an den Kernen und der Architektur auch an anderen Formfaktoren, anderen kleinen Plattformen, kleineren Mainboards und Verbrauchsszenarien für den Batteriebetrieb. Auf der anderen Seite musste man an der Grafikperformance arbeiten und auch neue Features, wie Sicherheitsfeatures implementieren. Vielleicht sind diese Ausführungen auch ein wenig als Entschuldigung zu werten, dass sich Skylake etwas verzögert hat und man auf neue Gegenheiten und Anforderungsprofile im CPU-Markt Rücksicht nehmen musste.

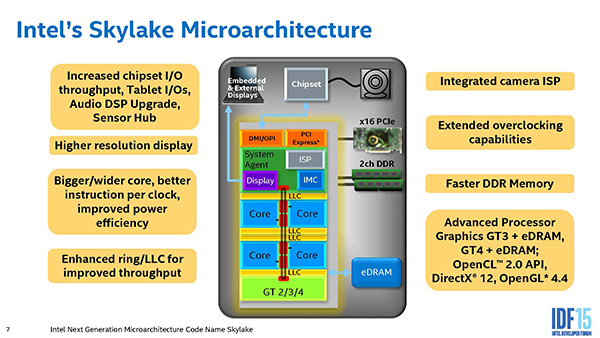

Die Skylake-Mikroarchitektur besteht natürlich zunächst aus der neuen Core-Architektur, die in vielen Bereichen verbessert wurde. Man verbesserte auch die Ring-Architektur und erhöhte die Bandbreite des Rings. Es gibt nun drei verschiedene Grafikausbaustufen, jeweils mit und ohne eDRAM, die in zukünftigen CPUs eingesetzt werden. Der Speichercontroller wurde verbessert, sodass DDR3 und DDR4 unterstützt wird. Die weiteren Bereiche PCIe, Display, Chipsatz und DMI wurden ebenfalls überarbeitet. Zudem wurde an einer Camera ISP gearbeitet für Tablets und 2-in-1s. Zudem hebt Intel die Overclockingfähigkeiten hervor.

Die folgenden Ziele gab es bei der Entwicklung von Skylake: Höhere Instruktionen pro Takt und ein höherer Takt, um Leistungsgewinne zu ermöglichen. Eine Verringerung des Energieverbrauchs, Sicherheitsverbesserungen und eine bessere Konfigurierungsmöglichkeit waren weiter Ziele.

Wie immer können dedizierte Server- und Client-IP-Konfigurationen von Skylake gebaut werden, wobei Intel hier eigenen Informationen nach die Flexibilität erhöht hat. Da man allerdings noch nicht über die kommenden Server-Xeons spricht, lässt sich dies noch nicht nachvollziehen.

Kern-Veränderungen bei Skylake

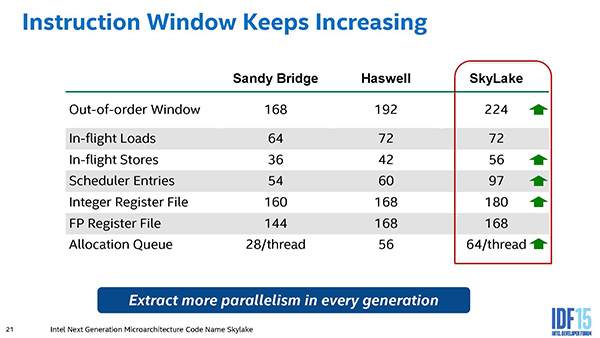

Auf Kern-Seite hat Intel das Front-End bei Skylake optimiert, eine Branch Prediciton mit höherer Kapazität integriert, größere Pufferspeicher implementiert und der Prefetch-Mechanismus verbessert. Die Out of Order Buffers wurden durch eine höhere Parallelisierung verbessert, weiterhin hat man auch die Ausführungseinheiten aufgebohrt. Hier wurde insbesondere auf eine verbesserte Latenz, mehr Einheiten und einen intelligenteren Abschaltungsmechanismus aus Stromverbrauchsgründen geachtet.

Um die Kerne ordentlich mit Daten füttern zu können wurde auch die Anbindung verbessert. Es gibt nun deutlich mehr load/store-Bandbreite durch Verbesserungen auf Prefetcher-Seite. Die Store-, Fill- und Write-Back-Buffer wurden vergrößert, bei Page Misses wurde ein schnelleres Handling implementiert („weniger intrusive“), identisches gilt für eine besseres L2-Cache-Miss-Handling, wodurch bei gleicher Bandbreite deutlich mehr Daten geliefert werden können. Hinzu kamen auch ein paar neue Instruktionen, die das Cache-Management betreffen. Das Hyperthreading hat Intel ebenso durch größere Reservation Stations und einen größeren Zwischenspeicher verbessert.

Neue Sicherheitstechnologien

Ein weiteres Ziel bei der Entwicklung der Skylake-Architektur war die Implementierung neuer Sicherheitstechniken. Zwei verschiedene Techniken kommen dabei zum Einsatz: SGX (Software Guard Extensions Technology) und MPX (Intel Memory Protection Extensions). Bei SGX handelt es sich um eine Technik, um Malware- und Software-Attacken auf bestimmte Speicherbereiche zu verhindern, in dem das System Trusted Encalves, also geschützte Bereiche einrichtet, auf die von aussen auch über Debugging-Funktionen nicht mehr zugegriffen werden kann. Bei MPX handelt es sich hingegen um einen Schutz gegen Buffer Overflows, die oft für Attacken verwendet werden. Das System prüft vor dem Zugriff, ob es einen Buffer Overflow geben könnte und blockiert den Zugriff dann im Vorfeld.

Verbesserungen beim Stromverbrauch

Wie bei jedem Prozessor aus der Core-Generation hat Intel auch das Ziel der Reduzierung des Stromverbrauchs nicht aus den Augen gelassen. Die Skylake-Architektur setzt dabei zum einen auf die fortschrittliche 14-nm-Produktion, die man schon von Broadwell kennt, aber es existieren einige neue Techniken, die den Stromverbrauch auf CPU- und Plattform-Ebene senken können. Auf Core-Ebene können die AVX2-Bereiche jetzt komplett deaktiviert werden, wenn der Code kein AVX2 enthält. Einige Verbesserungen betreffen zudem spezifische Funktionen, wie die Medien-Wiedergabe: Hier hat Intel Hardwarefunktionen implementiert, die auch ohne Core-Belastung laufen können und somit Strom sparen. Auf Grafikseite wurden Optimierungen beim Stromverbrauch für hochauflösende Displays implementiert und für kleinere Skylake-Modelle wurde das Ziel ins Auge gefasst, dass diese komplett fanless laufen können.

Neu ist Intels „Speed Shift Technology“: Hier übernimmt Intel die Kontrolle der Betriebszustände der CPU. Aktuell wird dies über einen Software-Layer vom Betriebssystem mit den bekannten P-States vorgenommen, die es nun nicht mehr gibt. Allerdings muss das Betriebssystem die neue Art und Weise beherrschen - das kann aktuell nur Windows 10. Bei besonders leistungsintensiven Applikationen kann der Prozessor mit hohem Takt betrieben werden, um dann möglichst schnell in den Halt-Modus gebracht zu werden. Das Prinzip kennt man von älteren Intel-Prozessoren als „Hurry Up and Get Idle (HUGI)“, jetzt nennt es Intel Race to Halt. Bei manchen Anwendungen ist dies allerdings nicht möglich, da sie dauerhaft mit niedrigerer Performance laufen. Hier optimiert das Betriebssystem dann im Hinblick auf die verbrauchte Gesamtenergie.

Bei allen derartigen Speed-Shift-Optimierungen hat Intel allerdings auch darauf geachtet, dass die Responsiveness des Systems nicht leidet. Um den Stromverbrauch im Leerlauf zu senken, hat Intel die Frequenz des Prozessors nicht weiter abgesenkt, da dann die Responsiveness leidet. Statt dessen baut man Duty Cycles ein, also quasi ein ständiges „Ein-Aus-Ein-Aus“ des Prozessors, da sich dann Bereiche komplett abschalten lassen. Ein weiterer Vorteil der Lösung in Hardware ist, dass die Responsiveness des Prozessors deutlich erhöht wird.

Die Speed Step Technology kennt man schon von älteren Intel-Prozessoren und ist ja ein Klassiker, jetzt wurde sie auch für den System Agent und das Memory Subsystem implementiert. Diese Bereiche können jetzt auch je nach Belastung heruntergetaktet werden.

Um auch eine bessere Kühlung des Systems zu gewährleisten – oder die Energieeinsparungen durch OEMs in leisere Systeme umzusetzen, gibt es die Möglichkeit, die Skin-Temperatur des Prozessors und bessere Wärmesensor-Informationen auszulesen. Somit können bessere Kühllösungen gebaut werden und die Probleme, die in der Vergangenheit durch Throttling bestanden haben, sollen minimiert werden.

Verbesserungen der Caches und deren Anbindung

Diverse Tweaks hat Intel auch bei den Caches implementiert. Der Durchsatz des Last-Level-Caches ist um den Faktor 2 gestiegen, da man das Cache Miss Handling verbessert hat. Bei gleichbleibendem Stromverbrauch hat man zudem den Durchsatz des Ring-Busses verdoppelt. Die eDRAM-Cache-Architektur wurde verbessert, in dem er nun vollständig kohärent agiert und nicht nur für die Grafik, sondern auch für I/O, Display oder andere Zugriffe genutzt werden kann, ohne geflashed werden zu müssen. Dies wurde erreicht, in dem er jetzt über den System Agent angebunden ist und nicht mehr über den Last-Level-Cache.

Weitere Optimierungen

Um den Prozessor auch in Tablets einsetzen zu können, hat Intel im kompletten Skylake-Lineup einen Image Signal Processor integriert, der bis zu vier Kameras mit je 13MP verarbeiten kann. Intel hat diesen ISP in den Prozessor integriert, um ihn aus Stromverbrauchsgründen direkt auf dem Die steuern zu können. Zudem können für Tablets kleinere CPU-Formate realisiert werden und Platz gespart werden. Als Spezifikationen gibt Intel an, dass die Kameras mit 2160p und 30 Hz oder 1080p und 60 Hz mit niedrigem Stromverbrauch und hoher Performnace laufen können.

Auf Chipsatzebene ist es den Chipsätzen jetzt auch möglich, den Takt zu verändern und zu throttlen, zudem wurden – und das haben wir schon in den ersten Tests beschrieben – die I/O-Ports deutlich aufgebohrt und verbessert, sei es durch PCIe 3.0, NVME oder USB 3.0. Die Anbindung an die CPU ist mit dem DMI 3.0 ebenso verbessert, um nicht hier ein neues Bottleneck entstehen zu lassen.

Hinzu kommen noch die bereits bekannten Overclocking-Funktionen, die wir mit dem Core i7-6700K schon demonstriert haben.

Wer sich das komplette PDF einmal ansehen möchte, kann dies bei Intel im IDF-Bereich bei der zugehörigen Veranstaltung.

{jphoto image=80451}