Werbung

Das Geheimnis ist eigentlich längst keines mehr und dennoch sorgt eine Präsentation der Technik aus dem Forschungszentrum CERN für Aufsehen. Darin ist die Rede von zukünftigen AMD-Serverprozessoren mit 32 physischen Kernen, die auf der neuen Zen-Architektur basieren sollen.

Gehalten wurde der Vortrag Ende Januar von einem Techniker des CERN (Europäische Organisation für Kernforschung). Dort wird unter anderem Grundlagenforschung betrieben und dazu werden auch große Teilchenbeschleuniger verwendet. Derzeit ist dies der Large Hadron Collider, der 2008 in Betrieb genommen wurde. Bei Versuchen erzeugt er eine riesige Datenmenge, die teilweise nicht mehr lokal und direkt an der Forschungseinrichtung gespeichert werden kann, sondern per Glasfaser an zahlreiche europäische Einrichtungen verschickt wird, um sie dann zu speichern. Diese enormen Datenmengen machen vielleicht auch ersichtlich, warum man am CERN an AMDs zukünftigen Serverprozessoren auf Basis der Zen-Architektur interessiert ist.

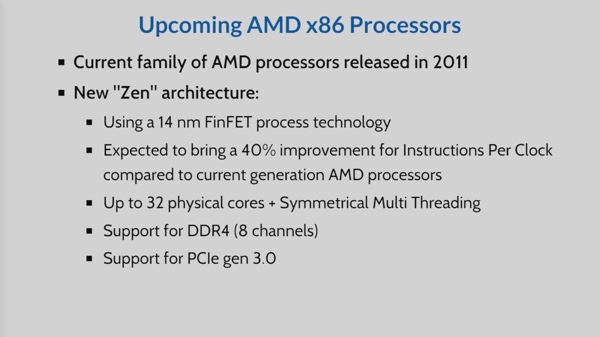

In der Präsentation werden einige interessante und teilweise bereits bekannte Details aufgeführt. Unter anderen wird die Fertigung in 14-nm-FinFET erwähnt. Außerdem sollen die Prozessoren bei gleichem Takt etwa 40 % schneller arbeiten können. Doch soweit waren diese Kennzahlen bereits bekannt und AMD hat diese teilweise bereits bestätigt. Interessant wird es bei der Anzahl der Kerne. Hier ist von 32 physischen Kernen die Rede. Per Symmetrical Multi Threading (bei Intel Hyperthreading) sind sogar 64 Theads verfügbar. Ebenfalls erwähnt wird ein Octa-Channel-Interface für DDR4-Arbeitsspeicher. Wenig spektakulär ist die Unterstützung von PCI-Express 3.0. Die Anzahl der Kerne wurde zuletzt durch einen neuen Linux-Kernel bestätigt, wenngleich auch diese Veröffentlichung sicherlich etwas früh geschah.

Natürlich gibt die Folie keinerlei detaillierte Auskunft über die Architektur oder den Aufbau des Prozessors. 32 physische Kerne auf einem Die sind aber mehr als unwahrscheinlich und so dürfte es sich bei dem Prozessor um einen Multi Chip Package (MCM) handeln, das mehrere Dies in einem gemeinsamen Package beinhaltet. Es dürfte sich dabei um zwei Zeppelin-CPUs mit jeweils 16 Kernen handeln. Auf diese beiden Dies teilen sich auch die insgesamt acht Speicherkanäle auf, so dass pro Chip derer vier zur Verfügung stehen. Eine zusätzliche Komplexität könnte das Thema erlangen, wenn nicht nur zwei Dies auf einem Package untergebracht werden müssen, sondern sich dabei auch noch High Bandwidth Memory befindet, der über einen Interposer mit der CPU/GPU verbunden wird.

Es ist nicht unüblich, dass Hersteller von CPUs und GPUs lange vor der eigentlichen, öffentlichen Präsentation neuer Hardware bereits mit professionellen Anwendern bzw. im Rahmen derer Einsatzgebiete über die technischen Details sprechen. Rechenzentren sind langfristig ausgelegt und Update-Zyklen über Jahre hinweg geplant – dazu ist es natürlich wichtig zu wissen, was in einigen Monaten an neuer Hardware erscheinen wird. NVIDIA verbaut seine Tesla-Karten meist noch vor der offiziellen Ankündigung in einigen Rechenzentren und ebenso gehen Intel und AMD vor.

Im Vortrag ebenfalls ein Thema waren zukünftige Prozessoren aus dem Hause Intel. Hier sind aber offenbar keine bisher unbekannten Details verkündet worden. Außerdem eine Rolle spielen Speichertechnologien und weitere Infrastruktur in Rechenzentren. Dennoch lohnt sicherlich ein Blick in den Vortrag, zu dem ein Video verfügbar ist und der etwa 45 Minuten dauert.