Werbung

Bereits viel wurde darüber spekuliert, welche Änderungen AMD mit den EPYC-Prozessoren der zweiten Generation einführen wird. Diese werden auf Basis der Zen-2-Architektur auf den Markt kommen, die ebenfalls in der zweiten Generation entwickelt wurde. Vorgesehen ist die Fertigung in 7 nm. Seit Sommer diesen Jahres hat AMD bereits die ersten Samples im Labor und will ab 2019 im Serversegment einen erneuten Angriff auf Intel starten.

AMD fährt in seiner aktuellen CPU-Strategie den Weg der Multi-Chip-Modules, verbaut also in den Ryzen-Threadripper- und EPYC-Prozessoren vier Dies, von denen immer mindestens zwei aktiv sind. Jeder dieser Dies verfügt über bis zu acht Kerne, so dass wir bei vier Dies mit jeweils acht Kernen von bis zu 32 Kernen sprechen, die in den High-End-Modellen zur Verfügung stehen. Intel hingegen bleibt bisher dem monolithischen System treu und verbaut einen großen Die mit bis zu 28 Kernen.

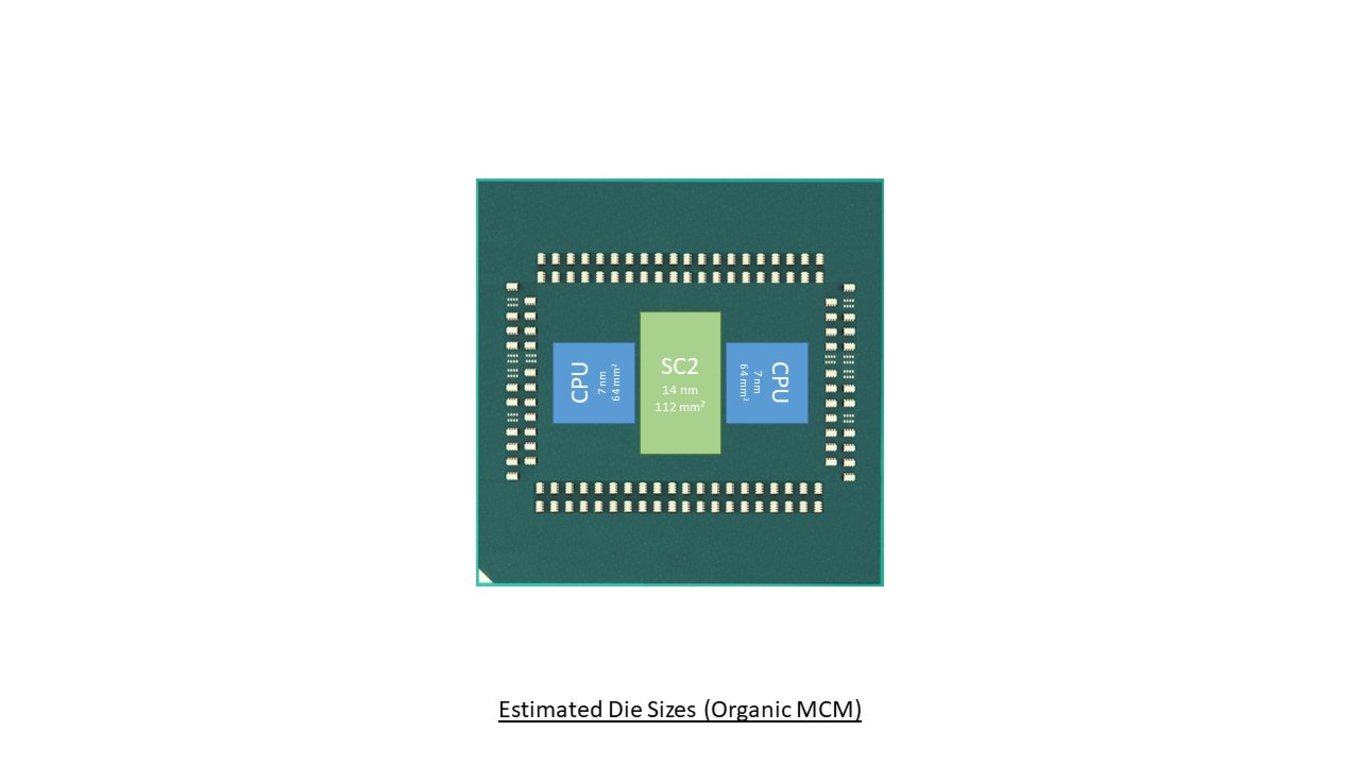

Für Zen 2 wurde bisher davon ausgegangen, dass AMD die Anzahl der Kerne pro CCX-Cluster, also Die, erhöht. Zwölf Kerne pro CCX waren dabei denkbar und am wahrscheinlichsten. Doch offenbar fährt AMD die MCM-Strategie noch etwas breiter aus und nutzt dabei die Vorteile von MCM. Statt eines großen Chips, der in 7 nm zwar etwas kleiner wird, aber auch extrem teuer in der Fertigung ist, setzt man weiterhin auf viele kleine Komponenten, die dann in einem MCM zusammengeführt werden. Aktuell verfährt man genauso und lässt einzig Zeppelin-Dies mit jeweils 213 mm² fertigen, die dann in den Ryzen-, Ryzen-Threadripper- und EPYC-Prozessoren zum Einsatz kommen. Die Fertigung der Zeppelin-Dies in dieser geringen Größe ist deutlich günstiger und skaliert über die Stückzahl sicherlich extrem gut.

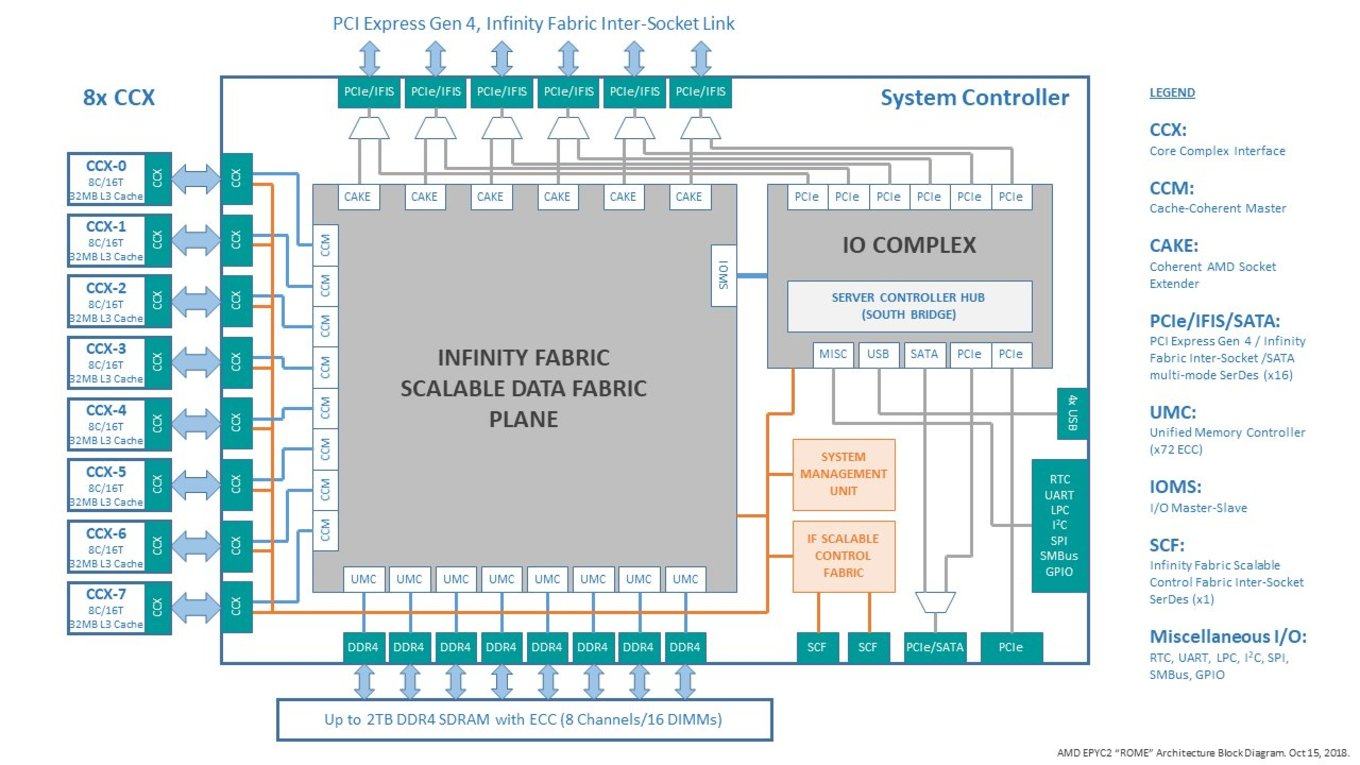

Für EPYC 2 sollen nicht mehr nur vier Dies zum Einsatz kommen, die dann per Infinity Fabric miteinander verbunden werden, sondern gleich neun. An zentraler Stelle befindet sich in diesem Konzept ein Controller-Chip, der alle Aufgaben des Interconnects übernimmt und steuert. Wie sich bei den Tests der Ryzen-Threadripper-Prozessoren (AMD Ryzen Threadripper 2990WX und 2950X und AMD Ryzen Threadripper 2920X und 2970WX im Test) gezeigt hat, kommt der Ansteuerung der Caches und Speichercontroller mit akzeptablen Latenzen eine extrem wichtige Rolle zu und dabei werden auch die Nachteile eine MCM-Designs deutlich. Der Controller soll genau dies übernehmen und optimieren.

An den Controller angebunden sind dann die einzelnen CCX-Dies. Ausgehend von einem ähnlichen Aufbau wie bisher besitzen diese jeweils acht Kerne und 32 MB an L3-Cache, so dass ein EPYC-2-Prozessoren im Vollausbau auf 64 Kerne kommt, die 128 Threads verarbeiten können. Außerdem stünden dem Prozessor 256 MB an L3-Cache zur Verfügung.

Weiterhin vorhanden wären acht DDR4-Speichercontroller, die über acht Kanäle und auf 16 DIMM-Steckplätzen bis zu 2 TB an Arbeitsspeicher anbinden können. Die Speichercontroller sitzen ebenfalls im besagten Controller-Chip und nicht mehr in den einzelnen CCX-Dies. Gleiches gilt für die 128 PCI-Express-Lanes, die im Falle von Zen 2 vermutlich schon als PCI-Express 4.0 ausgeführt sind. Eine art Server-Controller oder Southbridge übernimmt die Anbindung weiterer I/O-Komponenten wie USB und SATA.

Es handelt sich bei den Informationen noch nur um Gerüchte, an denen es aber nur noch wenige Zweifel gibt. Eine offizielle Bestätigung könnte aber bereits in Kürze folgen, denn AMD hat zu einem Event in San Francisco geladen, bei dem Datacenter-Produkte im Fokus stehen sollen. Ab wann die hier präsentierten Informationen dann aber öffentlich sein werden, kann derzeit nicht abgeschätzt werden.

Ryzen der 3. Generation dann ebenfalls als MCM denkbar

Die Ryzen-Prozessoren bieten derzeit maximal acht Kerne, da hier nur ein Die zum Einsatz kommt. Mit Zen 2 und der Fertigung in 7 nm wäre aber auch hier ein MCM-Ansatz denkbar. Der Controller könnte die Latenzen und Bandbreitenlimitierungen in Grenzen und für Spieler in einem erträglichen Rahmen halten. Damit wäre ein fiktiver „Ryzen 3800X" mit zwei Dies und bis zu 16 Kernen denkbar. Ob AMD dies auch so umsetzen kann und wird, werden wir aber erst in der ersten Jahreshälfte 2019 wissen.