Werbung

Unter dem Motto "New Horizon" hat AMD in San Francisco über seine Zukunft im Datencenter gesprochen. Nach einem Rückblick zu EPYC und Radeon Instinct ging es dann auch schon an die Neuerungen.

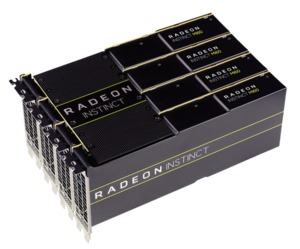

Nicht aber eine Radeon Instinct MI25 mit Vega-GPU in 7 nm und im Vollausbau mit 64 Compute Units wurde zunächst vorgestellt, sondern eine Radeon Instinct MI60 als erste "7 nm GPU" - und damit als schnellste GPU-Beschleuniger mit PCI-Express-Interface. Die Karte wird anhand der Namensgebung eine Rechenleistung von 60 TFLOPs für FP16-Berechnungen bieten. Die Radeon Instinct MI25 kommt auf 25 TFLOPs Peak-Rechenleistung für FP16.

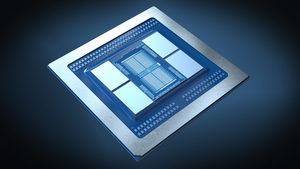

Die Radeon Instinct MI60 soll auf der Vega-20-GPU basieren und kommt auf 13,28 Milliarden Transistoren und besitzt eine Chipfläche von 331 mm². Die Vega-10-GPU kommt auf 12,5 Milliarden Transistoren auf einer Fläche von 484 mm². Zudem wird PCI-Express 4.0 offiziell unterstützt, was im Datacenter von besonderer Bedeutung ist.

Neben der Vega-20-GPU bietet die Radeon Instinct MI60 noch vier HBM2-Speicherstacks für einen Speicherausbau von bis zu 32 GB. Das Speicherinterface ist 4.096 Bit breit und soll eine Speicherbandbreite von 1 TB/s aufweisen. Die Speicherchips müssen dazu mit 1.000 MHz arbeiten.

Anders als die Vega-10-GPUs wird Vega 20 auch FP64-Einheiten bieten können und soll zudem mit INT8 und INT4 umgehen können. Außerdem gibt es eine Ende-zu-Ende-Verschlüsselung mit ECC-Unterstützung.

Es wird offenbar auch noch eine Radeon Instinct MI50 geben, die entsprechend eine Rechenleistung von 50 TFLOPs FP16-Rechenleistung aufweisen wird. Es wird sich dabei wohl um eine kleinere Ausbaustufe der Vega-20-GPU handeln. Ebenfalls unterstützt werden INT8- und INT4-Berechnungen.

Ein Vergleich der Rechenleistung:

| Modell | GeForce RTX 2080 Ti | Quadro RTX 8000 | Tesla V100 | Radeon Instinct MI60 | Radeon Instinct MI50 |

| Technische Date | |||||

|---|---|---|---|---|---|

| GPU | TU102 | TU102 | GV100 | Vega 20 | Vega 20 |

| Architektur | Turing | Turing | Volta | Vega | Vega |

| Fertigung | 12 nm | 12 nm | 12 nm | 7 nm | 7 nm |

| Shader | 4.332 | 4.608 | 5.120 | 4.096 | 3.840 |

| GPU-Takt | 1.635 MHz | 1.770 MHz | 1.380 MHz | 1.800 MHz | 1.746 MHz |

| Speicherinterface | 352 Bit | 384 Bit | 4.096 Bit | 4.096 Bit | 4.096 Bit |

| Speicherausbau | 11 GB GDDR6 | 48 GB GDDR6 | 32 GB HBM2 | 32 GB HBM2 | 16 GB HBM2 |

| Speichertakt | 1.750 MHz | 1.750 MHz | 900 MHz | 1.000 MHz | 1.000 MHz |

| Speicherbandbreite | 616 GB/s | 672 GB/s | 900 GB/s | 1 TB/s | 1 TB/s |

| Interconnect | NVLink 100 GB/s | NVLink 100 GB/s | NVLink 150 GB/s | Infinity Fabric 100 GB/s | Infinity Fabric 100 GB/s |

| TDP | 260 W | 295 W | 300 W | 300 W | 300 W |

| Rechenleistung | |||||

| FP32 TFLOPS | 14,2 | 16,3 | 15,7 | 14,7 | 13,4 |

| INT32 TIPS | 14,2 | 16,3 | 15,7 | - | - |

| FP64 TFLOPS | 0,445 | 0,510 | 7,8 | 7,4 | 6,7 |

| FP16 TFLOPS | 28,5 | 32,6 | 31,4 | 29,5 | 26,8 |

| INT8 Tensor TOPS | 227,7 | 261 | 60 | 58,9 | 53,6 |

| INT4 Tensor TOPS | 455,4 | 522 | 120 | - | - |

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen

Rome auf Basis von Zen 2

An zentraler Stelle steht aber die Zen-Architektur der zweiten Generation: Zen 2. AMD spricht für den Einsatz von Zen 2 von "Hochleistungskernen", die in 7 nm gefertigt werden. Neben der Fertigung in 7 nm gibt es ein "modulares System Design" – Details dazu später. Der erste Prozessor, der die Zen-2-Architektur einsetzen wird, wurde ebenfalls vorgestellt und hört auf den bereits bekannten Namen Rome – er wird als EPYC 2 im kommenden Jahr auf den Markt kommen.

Für die Fertigung in 7 nm hat AMD mit TSMC zusammengearbeitet. Bisher war GlobalFoundries für die Fertigung der Prozessoren der Partner der Wahl – dies scheint sich nun zu ändern. Die Fertigung für 7 nm bietet eine um den Faktor zwei höhere Packdichte, ermöglicht eine halbierte Leistungsaufnahme bei gleicher Performance oder aber ermöglicht ein Leistungsplus von 25 % bei gleicher Leistungsaufnahme.

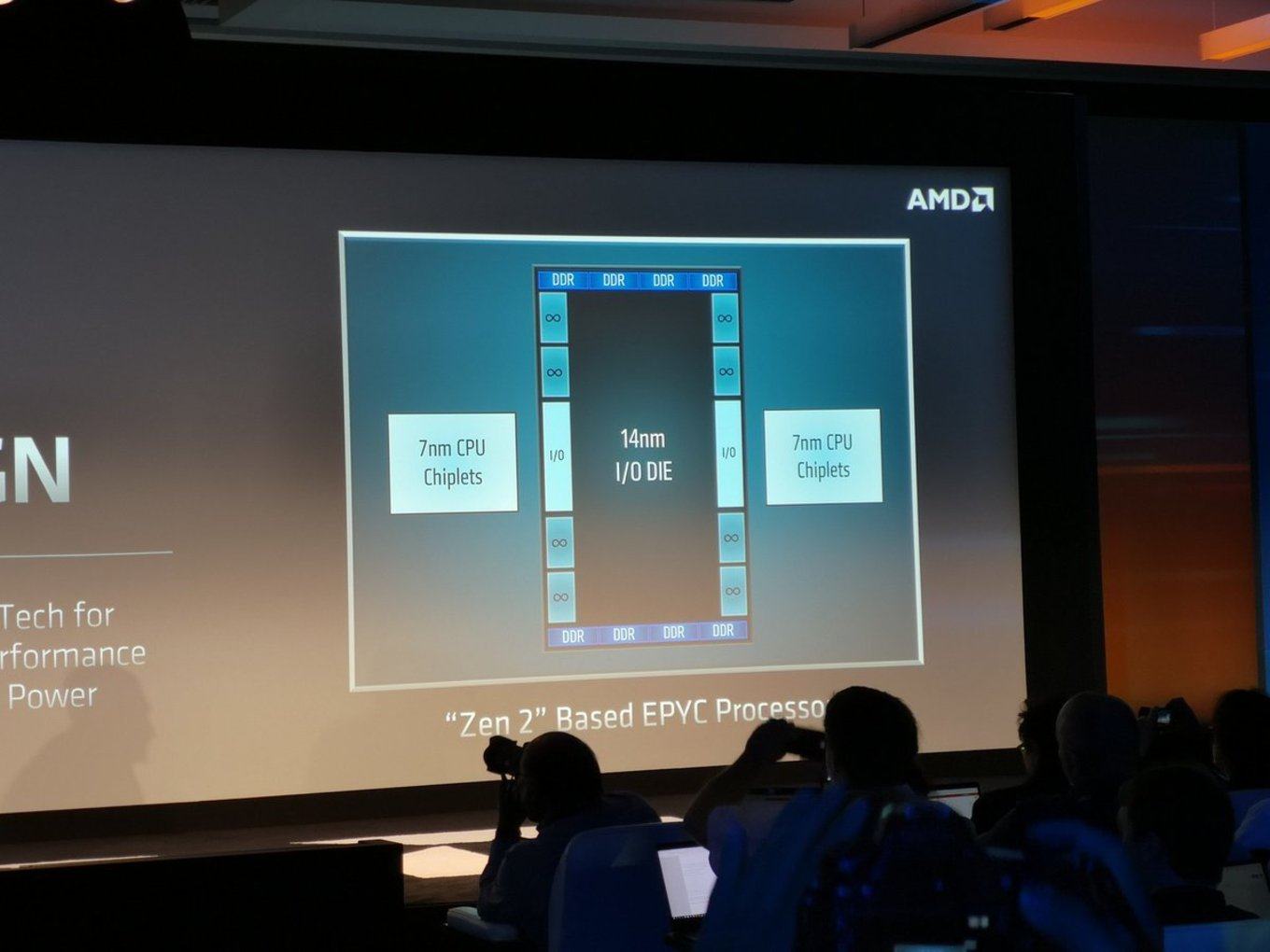

Rome wird aus einem I/O-Die bestehen, der in 14 nm gefertigt wird und sämtliche I/O-Aufgaben übernimmt. Realisiert wird dies über den Infinity Fabric in der 2. Generation. An den I/O-Die werden dann die CPU-Chiplets angebunden. In der Präsentation zeigt AMD einen Aufbau mit einem zentralen I/O-Die mit zwei CPU-Chiplets. Wie die Chiplets selbst aufgebaut sind, hat man noch nicht verraten. AMD spricht allerdings von einer höheren "Core Density" – also womöglich verdoppelten Anzahl an Kernen pro CCX.

Um die Rechenleistung weiter zu erhöhen und dem Datacenter-Fokus gerecht zu werden, hat AMD die Zen-2-Architektur etwas ausgebaut. Unter anderem bietet diese nun vier 256 Bit breite FPUs (Floating Point Units). Zudem hat man den Op-Cache vergrößert, den Instructions Cache reorganisiert und die gesamte Pipeline weiter optimiert. AMD spricht außerdem davon, pro Rechenoperation mit Zen 2 nur die halbe Leistungsaufnahme zu benötigen.

Die EPYC-Prozessoren der zweiten Generation unterstützen PCI-Express 4.0, genau wie die Radeon Instinct MI60 und Radeon Instinct MI50. Zwischen CPU und GPU lassen sich damit bidirektional bis zu 64 GB/s übertragen. Der Infinity Fabric kommt für eine GPU-zu-GPU-Verbindung auf 100 GB/s pro Link. Verbunden werden können bis zu vier Radeon-Instinct-Beschleuniger in einer Ring-Topologie.

In den Fußnoten einer Folie wird das Vorhandensein von 64 Kernen erwähnt. Zudem wird ein Speicherinterface mit acht Kanälen genannt. Inzwischen sind diese Zahlen auch auf der Bühne bestätigt worden.

Letztendlich werden damit die Gerüchte eines 8+1-Designs bestätigt. Statt eines großen Chips, der in 7 nm zwar etwas kleiner wird, aber auch extrem teuer in der Fertigung ist, setzt man weiterhin auf viele kleine Komponenten, die dann in einem MCM zusammengeführt werden. Der auf der Bühne gezeigte Chip zeigt zentral den I/O-Die, der in 14 nm gefertigt wird. Daneben sind acht Chiplets zu sehen - die CCX-Dies mit jeweils acht Kernen.

Zusammengenommen sollen die 8+1-Dies auf eine Chipfläche von 1.000 mm² – die ließ AMD auf dem Event verlauten. Aus den vorliegenden Bildern kann man eine Größe eines CCX-Dies von jeweils etwa 72 mm² errechnen, der I/O-Die kommt auf etwa 430 mm².

Wie sich bei den Tests der Ryzen-Threadripper-Prozessoren (AMD Ryzen Threadripper 2990WX und 2950X und AMD Ryzen Threadripper 2920X und 2970WX im Test) gezeigt hat, kommt der Ansteuerung der Caches und Speichercontroller mit akzeptablen Latenzen eine extrem wichtige Rolle zu und dabei werden auch die Nachteile eine MCM-Designs deutlich. Der Controller soll genau dies übernehmen und optimieren.

An den Controller angebunden sind dann die einzelnen CCX-Dies. Ausgehend von einem ähnlichen Aufbau wie bisher, besitzen diese jeweils acht Kerne und 32 MB an L3-Cache, sodass ein EPYC-2-Prozessor im Vollausbau auf 64 Kerne kommt, die 128 Threads verarbeiten können. Außerdem stünden dem Prozessor 256 MB an L3-Cache zur Verfügung.

Weiterhin vorhanden wären acht DDR4-Speichercontroller, die über acht Kanäle und auf 16 DIMM-Steckplätzen bis zu 4 TB an Arbeitsspeicher anbinden können. Die Speichercontroller sitzen ebenfalls im besagten Controller-Chip und nicht mehr in den einzelnen CCX-Dies. Gleiches gilt für die 128 PCI-Express-Lanes nach PCI-Express-4.0-Standard.

Konkrete Daten zu den Taktraten gibt es noch nicht. Auf der Bühne zeigte AMD einen Vergleich mit einem EPYC-Prozessor mit 64 Kernen gegen zwei Intel Xeon Platinum 8180M mit jeweils 28 Kernen. Der verwendete C-Ray-Benchmark läuft auf EPYC-Prozessoren recht gut und so verwundert das Ergebnis mit 28 zu 30 Sekunden zu Gunsten von AMD auch nicht. Gekühlt wurde der EPYC-Prozessor mit 64 Kernen mittels Luftkühler. Die Taktraten sollen aber noch nicht final sein.

2019 sollen die EPYC-Prozessoren der 2. Generation auf den Markt kommen. Spätestens bis dann werden wir sicherlich die Taktraten und einzelnen Modelle kennen.