Werbung

AMD hat über seinen CTO Mark Papermaster verkündet, dass man nun offizielles Mitglied des Konsortiums hinter dem Compute Express Link (CXL) ist. Nach CCIX, OpenCAPI und Gen-Z ist CXL die vierte Interconnect-Entwicklung der letzten Jahre und an allen beteiligt sich nun auch AMD. Damit sind nun 55 Unternehmen an CXL beteiligt.

"I’m pleased to announce AMD has joined other industry leaders in the Compute Express Link (CXL) Consortium.

Since 2016 AMD has played a leadership role in driving three other new bus/interconnect standards, CCIX, OpenCAPI and Gen-Z. Like CXL, these three efforts are driven by the need to create tighter coupling and coherency between processors and accelerators, and better exploit new and emerging memory/storage technologies in open, standards-based solutions."

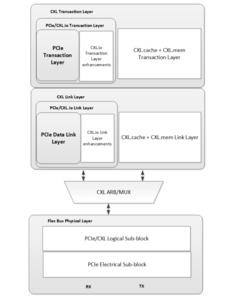

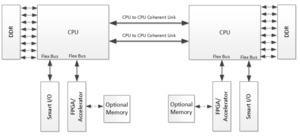

CXL soll den Bedarf an Bandbreite und Speicherkohärenz in zukünftiger Hardware decken können. Diese wird zwischen den Prozessoren, FPGAs, GPUs und anderen an einem High-Performance-Computing beteiligten Systemkomponenten benötigt. CXL wird dabei auf PCI-Express 5.0 basieren. Der Standard ist inzwischen final festgeschrieben und erreicht 32 GT/s bzw. 63 GB/s bei einer Breite von 16 Lanes. PCI-Express 6.0 wird schon 2021 erwartet. Da PCI-Express als physikalische Trägertechnologie von CXL verwendet wird, ist die schnelle Folge der Versionen 5.0 und 6.0 wohl eine Folge des hohen Bedarfs in diesem Bereich.

Die Wahl von PCI-Express als physikalischen Träger von CXL soll die beteiligten Unternehmen in die Lage versetzen, schnell und einfach eine Umsetzung der Technologie zu ermöglichen. Eigene Trägertechnologien für neue Protokolle bauten in dieser Hinsicht unnötige Hürden auf – so Intel. CXL besteht aus drei Protokollebenen: Einem I/O-Protokoll, einem Speicher-Protokoll und einem kohärenten Interface.

Als großes, am Datacenter-Markt beteiligtes Unternehmen, fehlt nun noch NVIDIA im Konsortium von CXL. Mit AMD und Intel sind aber schon einmal die größten Prozessor-Hersteller gemeinsam an CXL beteiligt.