Werbung

Auf der Linley Fall Processor Conference in Santa Clara hat Intel erste Details zur Tremont-SoC-Architektur für zukünftige, besonders sparsame Prozessoren, veröffentlicht. Einer der ersten Prozessoren, der auf die Tremont-Kerne setzt, ist der Hybrid-Prozessor Lakefield, der einen Sunny-Cove-Kern mit vier Tremont-Kernen kombiniert. Während zu den Sunny-Cove-Kernen schon recht viele Details bekannt sind, hüllte sich Intel zu Tremont noch in Schweigen.

Die Tremont-Kerne werden von Intel in 10 nm gefertigt. Ob dabei bereits die verbesserte 10-nm+-Variante zum Einsatz kommt, ist nicht bekannt. Tremont ist Teil der Elkhart-Lake-Plattform und wird mit einer Gen11-Grafikeinheit kombiniert – so auch bei Lakefield. Bisher hat Intel zwar einige mobilen Prozessoren aus der 10-nm-Fertigung angekündigt, aber noch keine für den High-Performance-Bereich. Es wird allerdings Xeon-Prozessoren auf Basis von Ice Lake geben. Ob es auch Desktop-Prozessoren aus der 10-nm-Fertigung geben wird, wird sich noch zeigen müssen. Zuletzt musste man große Zweifel daran haben.

Kommen wir nun aber zu Tremont:

Die Ziele für Tremont sind klar und soweit auch recht offensichtlich: Intel will die Single-Thread-Performance deutlich gesteigert haben. Außerdem soll das gesamte Design effizienter werden. Dazu tragen neue Instruktionen bei. Die Einschätzungen der Verbesserungen betreffen alle Metriken wie Leistung/mW und Leistung/mm².

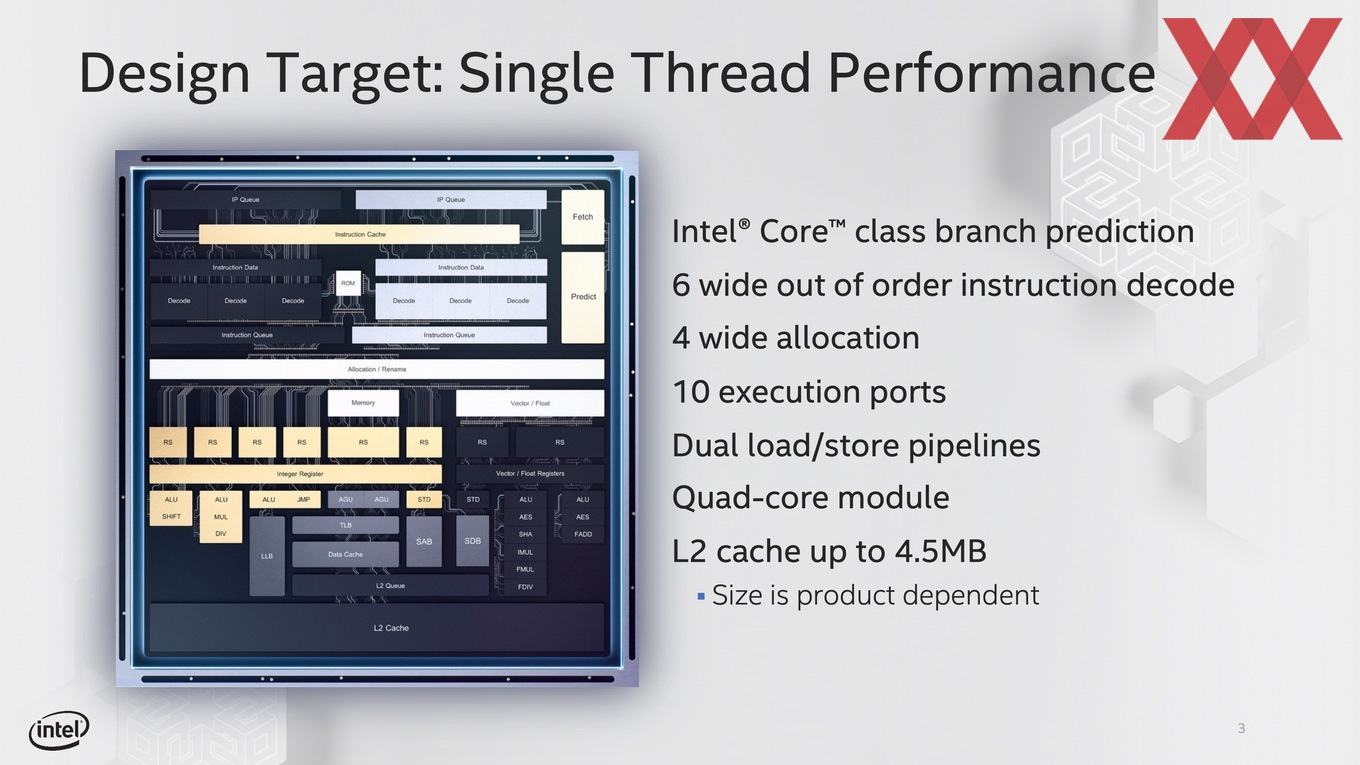

Um eine höhere Single-Thread-Performance zu erreichen, verwendet Intel für die Atom-Architektur nun eine Branch Prediction, wie sie auch bei den Core-Prozessoren eingesetzt wird. Zudem wird aus einer 3-Wide Pipeline ein 6-Wide Out-of-Order Instruction Decode, was mehr Instruktionen pro Takt ermöglicht. Es handelt sich allerdings um zwei 3-Wide-Cluster, die über eine unabhängige Instruction Queue und einen eigenen Instruction Data Cache verfügen, die sich andere Ressourcen wie den Instruction-Cache aber teilen.

Die Branch Prediction wird zu einem zunehmend wichtigeren Bereich einer CPU-Architektur. Sprungvorhersagen machen zu können, steigert die Leistung eines solchen Designs enorm, birgt jedoch einige Schwierigkeiten, die Intel mit einem größeren Predictor, der nun auf 32 Byte basiert, umgeht.

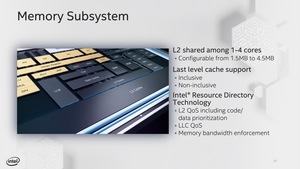

Der L1-Instruction-Cache ist mit 32 kB im Vergleich zu Goldmont unverändert geblieben, allerdings hat Intel den L1-Data-Cache von 24 auf ebenfalls 32 kB vergrößert. Während sich zwei Kerne der Goldmont-Architektur 1 MB an L2-Cache teilen mussten, stehen in der Tremont-Architektur 1,5 bis 4,5 MB zur Verfügung, die sich ein bis vier Kerne teilen. Die Anzahl der Kerne und die Größe des Caches hängen vom jeweiligen SoC-Modell ab. Der Translation Lookaside Buffer (TLB) ist mit 1.024 Einträgen nun halb so groß wie beispielsweise in der Ice-Lake-Architektur. Die Skylake-Architektur bietet einen 1.536 Einträge großen TLB. Auf einen µOP-Cache verzichtet Intel für Tremont.

Die eigentlichen Rechenaufgaben werden von drei ALUs (Arithmetic Logic Unit), zwei AGUs (Address Generation Unit), einer Jump-Unit und einer Data-Store-Unit übernommen.

Die verbesserte Architektur, eine leicht andere Cache-Hierarchie mit teilweise deutlich mehr L2-Cache pro Kern und die zahlreichen weiteren Verbesserungen sollen zu einem deutlichen Plus bei der Single-Thread-Performance führen. Auch einen L3-Cache können die Tremont-Kerne ansprechen und das tun sie im Falle der Lakefield-Prozessoren auch. Allerdings ist ein L3-Cache keine Grundvoraussetzung für das Design.

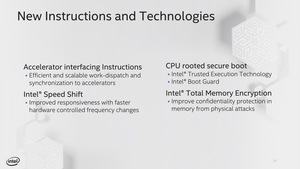

Weitere Anleihen aus den aktuellen Core-Prozessoren sind die Verwendung von Speed Shift, was die Tremont-Kerne in die Lage versetzen soll ihre Takt schneller wechseln zu können und einige Sicherheitsfunktionen. So unterstützen die zukünftigen Atom-Prozessoren mit Tremont-Kernen die Verschlüsselung des Arbeitsspeichers namens – bei Intel Total Memory Encryption (TME) genannt. Gegen Manipulationen der Firmware soll die Systeme durch einen CPU Rooted Secure Boot geschützt werden.

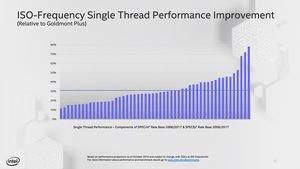

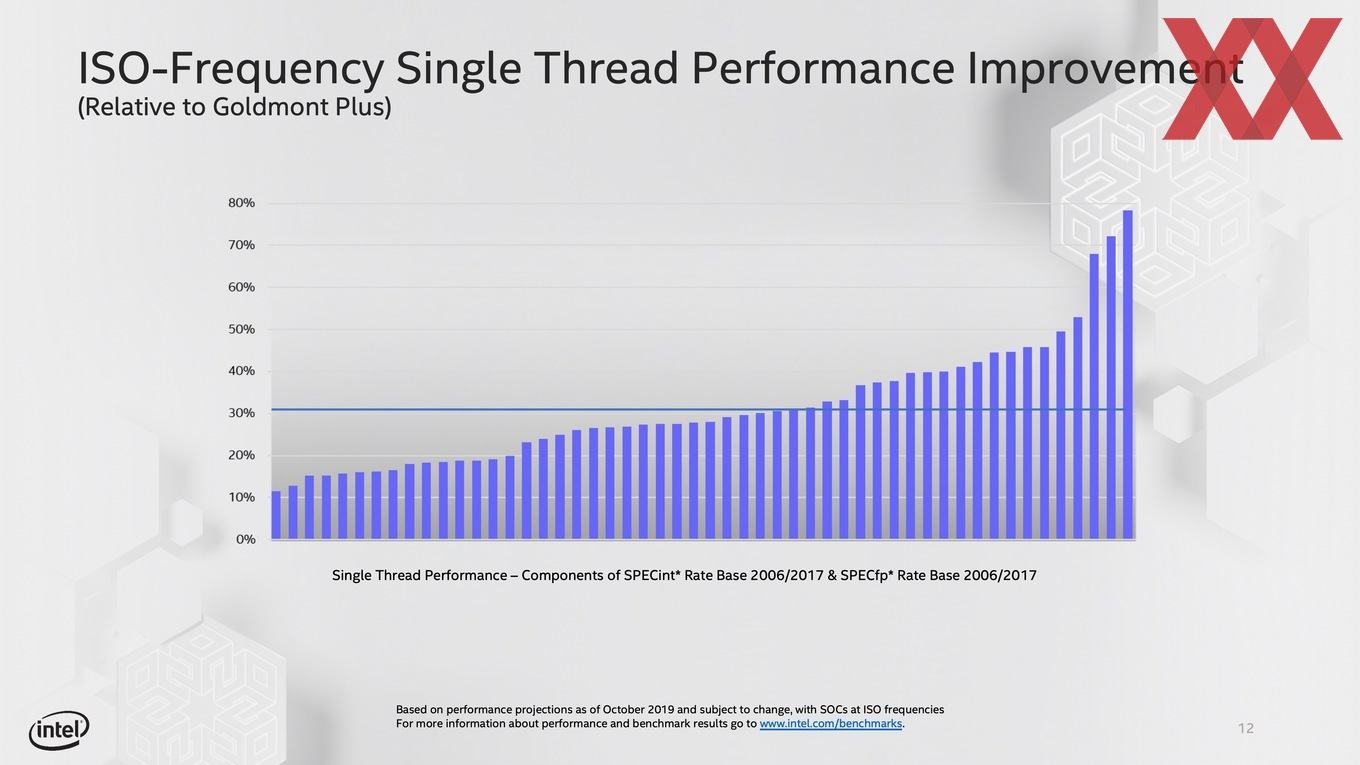

Intel stellt hier den Vergleich zu Goldmont Plus an. Goldmont Plus wiederum entspricht einer recht großen Verbesserung gegenüber Goldmont – zumindest größer als es der Namenszusatz vermuten lässt. Das Front- und Back-End wurden angepasst, ebenso das Speicher-Subsystem. Dennoch spricht Intel von einem Leistungsplus von 10 bis fast 80 %. Wie immer sind diese Angaben natürlich abhängig von der jeweiligen Anwendung. Im Schnitt soll das Plus allerdings 30 % betragen, was schon recht beachtlich ist.

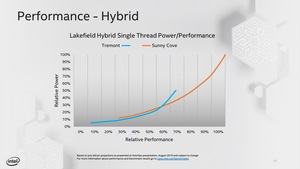

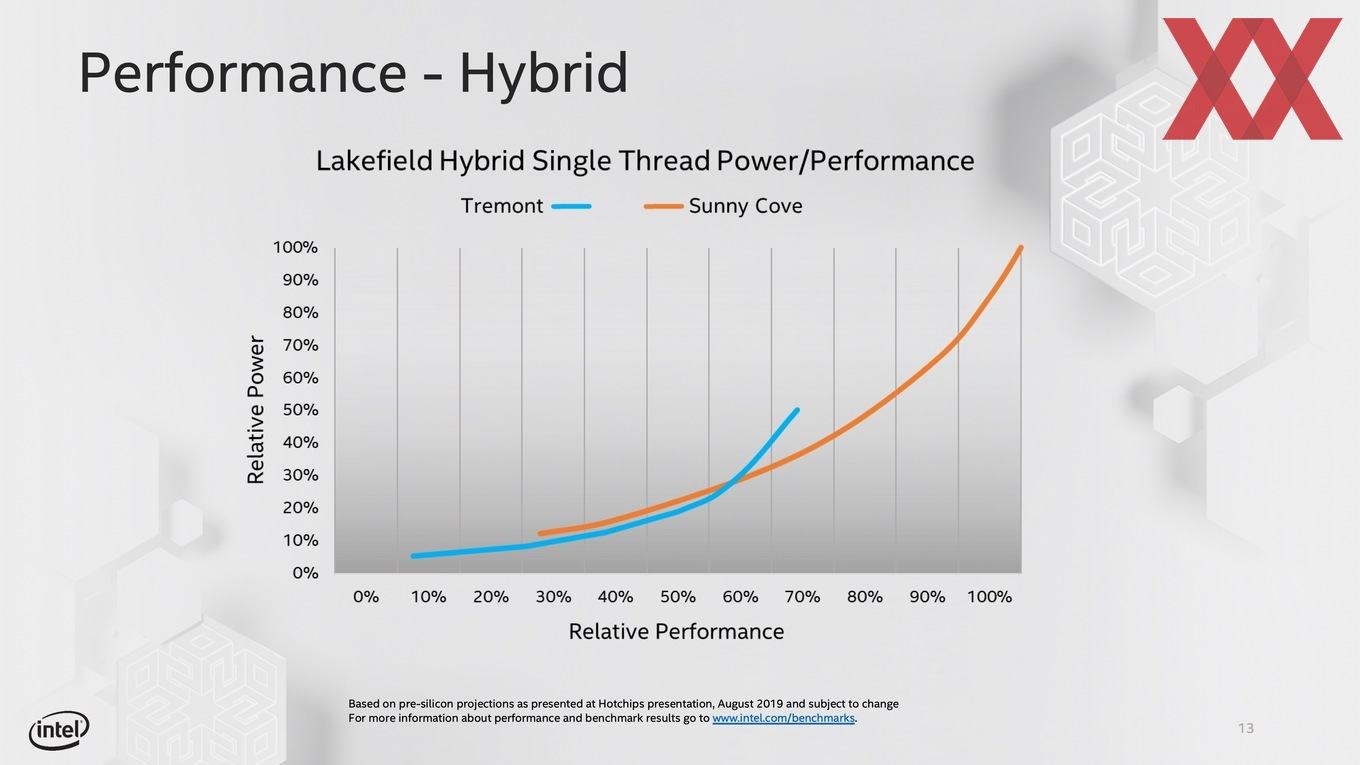

Erstes Einsatzgebiet der Tremont-Kerne ist der Lakefield-Prozessor, der vier dieser und einen Sunny-Cove-Kern verwendet. Als Hybrid-Design sollen sich die verschiedenen Kerne die Aufgabengebiete entsprechend aufteilen. Während der Sunny-Cove-Kern für Prozesse mit besonders hohen Leistungsanforderungen verwenden wird, können die Tremont-Kerne die vielen weniger aufwendigen Aufgaben übernehmen und helfen so Strom zu sparen.

Aber die Tremont-Kerne werden als Atom-Prozessoren auch in anderen Chips von Intel verwendet werden. Analog zu den aktuellen Atom-Prozessoren werden dies auch das Datacenter, Netzwerkhardware und andere Produkte sein, zu denen sich Intel jedoch noch genauer äußern will.

Die Details zu den konkreten Produkten stehen noch aus. So kennen wir bisher ausschließlich den Lakefield-Prozessor als Einsatzgebiet der Tremont-Architektur bzw. der entsprechenden Kerne. Intel wird aber sicherlich auch bald näheres zur Atom-Produktlinie verraten, denn hier dürften die Absatzzahlen wesentlich höher und der Markt für Intel entsprechend wichtig sein. Als Snow Ridge werden wir Tremont im Datacenter wiedersehen, aber auch dazu gibt es bisher recht wenige Details – schon gar nicht offiziell von Intel.

Intels eigene Angaben machen klar: Ein Tremont-Design kann aus bis zu vier Kernen mit bis zu 4,5 MB an L2-Cache bestehen. Den aktuellen Gerüchten zu Snow Ridge zufolge kann ein entsprechender SoC bis zu sechs Atom Core Tiles enthalten und diese wiederum bis zu vier Kerne. Wir könnten also vor allem im Datacenter Prozessoren sehen, die über 24 Kerne verfügen. Ob Intel diesen Maximalausbau nutzen wird, wird sich noch zeigen müssen.