Werbung

Im Hinblick auf die aktuelle Marktsituation bei den Desktop- und HEDT-Prozessoren hat Intel derzeit nicht viel bewundernswertes zu präsentieren (siehe Test zum Core i9-10980XE und den Ryzen-Threadripper-Prozessoren der 3. Generation), aber immerhin im Hinblick auf zukünftige Technologien scheint Intel sich wieder für einen härteren Kampf zu rüsten.

EMIB (Embedded Multi Die Interconnect Bridge) ist eine dieser Technologien, die im Falle des Kaby-Lake-G-Prozessors mit Vega-Grafikeinheit von AMD sogar schon zum Einsatz kam. Auch für einige Stratix-10-FPGAs verwendet Intels bereits EMIB zur Anbindung weiterer Komponenten an einen zentralen Chip.

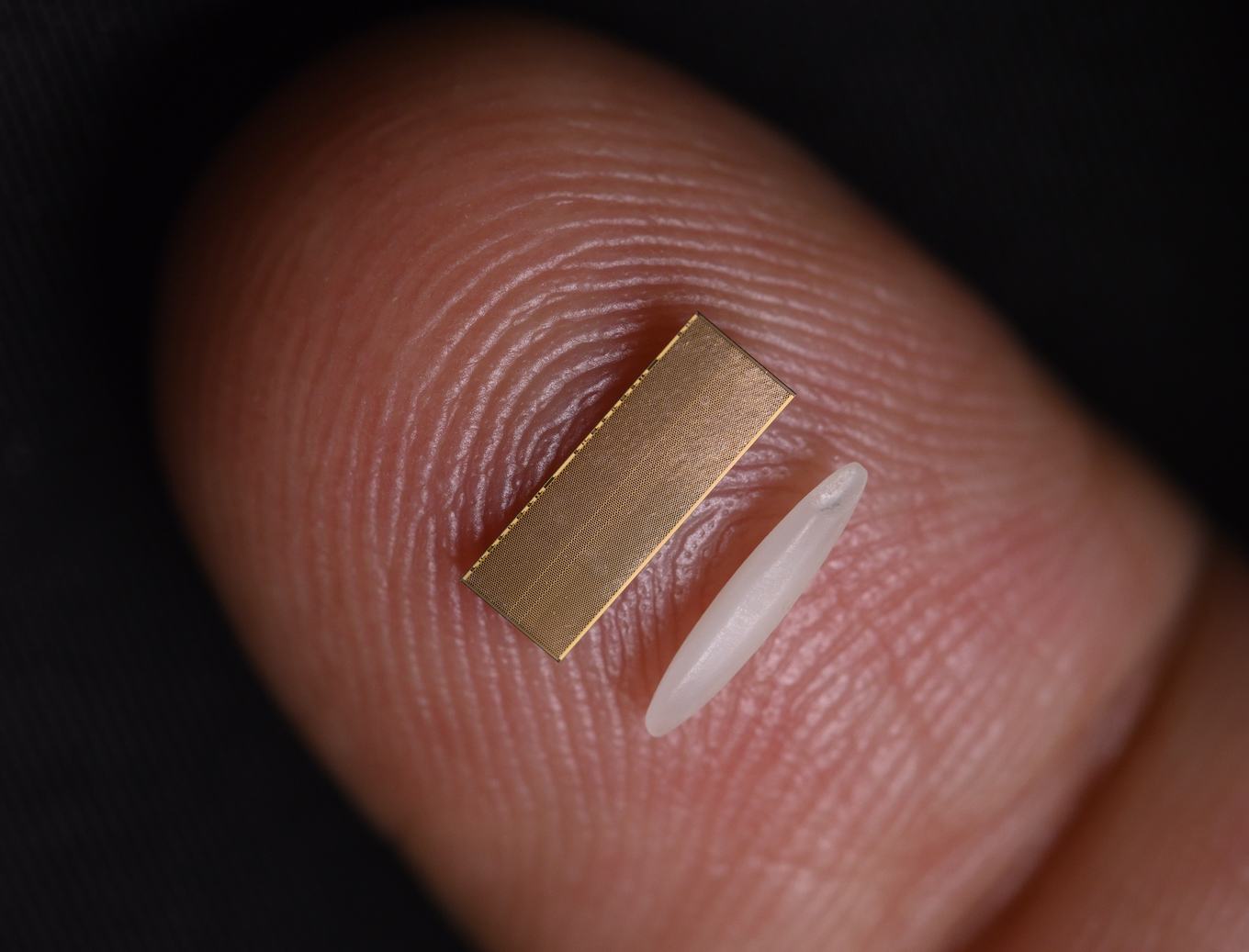

Nun hat man ein Bild veröffentlicht, welches eine solche Bridge zeigt. Zum Größenvergleich wurde auf die Fingerspitze ein Reiskorn gelegt. Eine solche Bridge wird verwendet, um beispielsweise zwei Chips miteinander zu verbinden. Aber auch HBM lässt sich darüber anbinden. Im Falle der Kaby-Lake-G-Prozessoren erreichte eine EMIB-Verbindung bereits über 200 GB/s. Im Falle der FPGAs dürfte es an die Terabyte pro Sekunde heranreichen.

Zukünftig sollen EMIB und eine weitere Kerntechnologie im Bereich des Packaging zusammen eingesetzt werden. In Co-EMIB wird der EMIB-Part im Substrat verwendet, auf dem dann die einzelnen Dies sitzen. Per FOVEROS werden dann auf bzw. in diesen Chips verschiedene Layer realisiert.

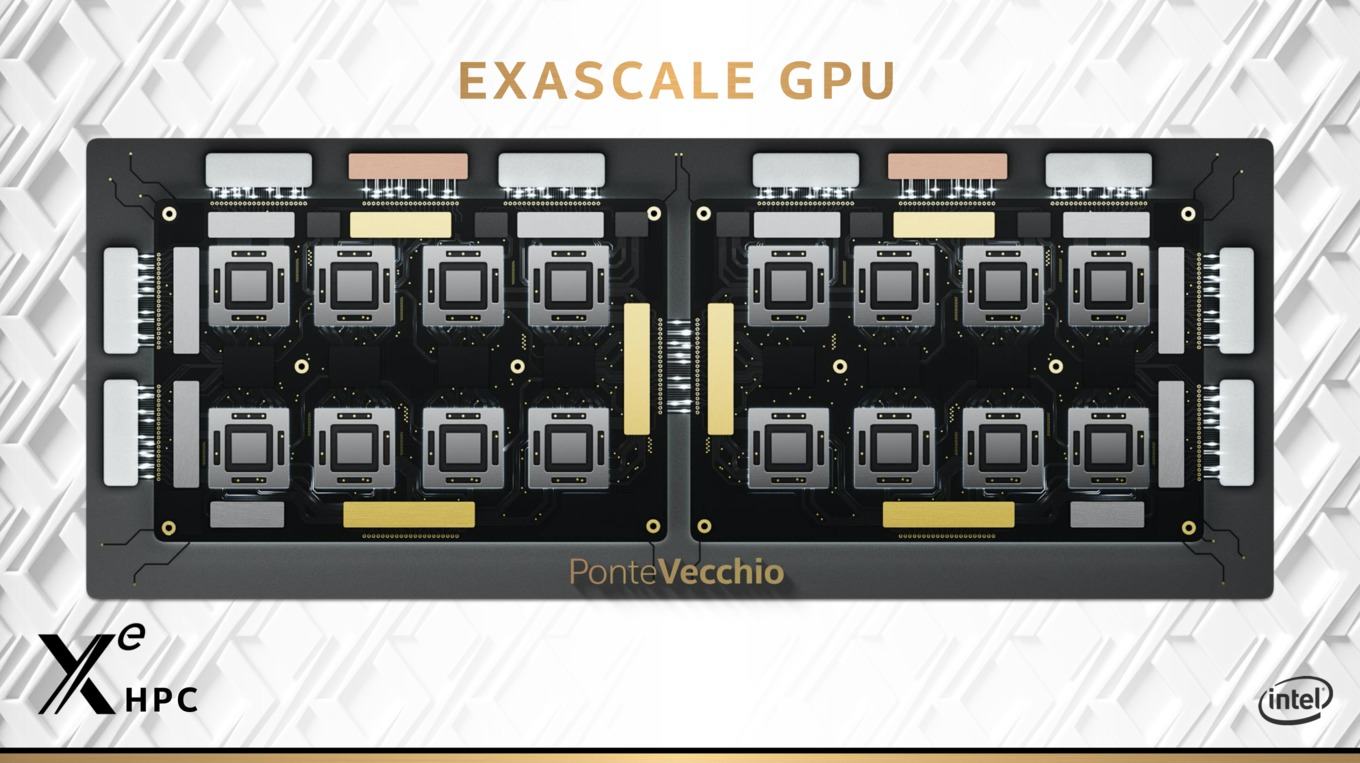

Erst kürzlich präsentierte Intel auf der Supercomputing 19 die Ponte Vecchio getaufte GPU auf Basis der Xe-Architektur. Sie soll zahlreiche technologische Meilensteine in sich vereinen. Zum einen wird sie der erste in 7 nm gefertigte Chip von Intel sein – dies hat man bereits vor einigen Monaten verraten. Zum anderen wird hier Intels Packaging-Technologie Foveros und EMIB zum Einsatz kommen. EMIB wird beispielsweise verwendet, um die HBM-Chips an das Chiplet-Design aus mehreren GPUs anzubinden. Außerdem scheint EMIB zum Einsatz zu kommen, um die beiden Slices der Ponte-Vecchio-GPU miteinander zu verbinden.

Die Ponte-Vecchio-GPU ist Intels zentraler Ansatz im HCP-Segment. Neben einem Design namens Xe-HPC für eben dieses Segment arbeitet Intel aber auch noch an Designs namens Xe-HP und Xe-LP. Xe-HP adressiert klar den Bereich der High-End-Grafikkarten, während Xe-LP für integrierte Lösungen angedacht ist. Hier müssen sich die konkreten Ansätze jedoch über die kommenden Monate herauskristallisieren. Bisher hat Intel noch recht wenige technische Details zur Xe-Architektur als solches verraten.