Werbung

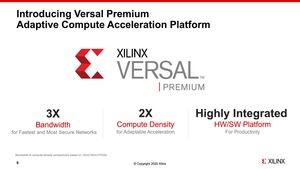

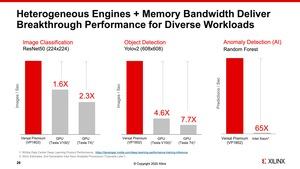

Xilinx hat mit der Versal-Premium-Serie eine neue Art von Cloud- und Netzwerkbeschleunigern vorgestellt, die 2021 auf den Markt kommen sollen. Mit der Adaptive Compute Acceleration Platform (ACAP) zielt Xilinx auf einen breiten Anwendungsbereich, der sich nicht nur auf reine Netzwerklösungen beschränkt, wenngleich hier sicherlich der Fokus liegt.

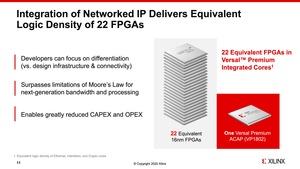

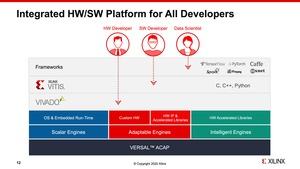

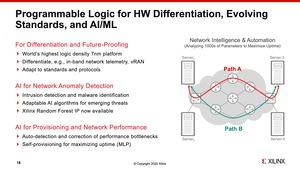

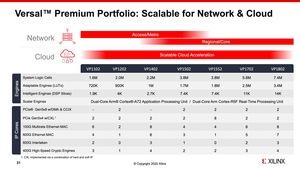

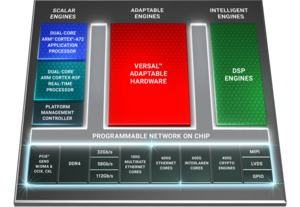

Zentraler Baustein des in 7 nm gefertigten Chips ist die Versal Adaptable Hardware, die je nach Modell aus einer unterschiedlichen Anzahl an Logikelementen besteht. Zwischen 1,6 und 7,4 Millionen Logikzellen bewegen wir uns hier. Hinzu kommen 720.000 bis 3.400.000 Adaptable Engines (LUT) und 1.900 bis 14.000 Intelligent Engines (DSP Slices).

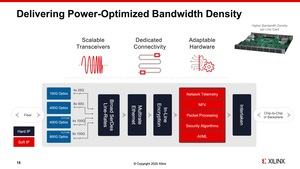

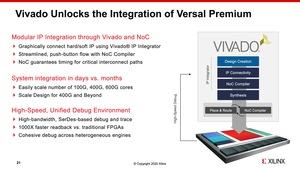

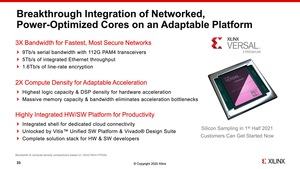

Immer gleich ist die Ausstattung an einem Dual-Core-Cluster bestehend aus ARM Cortex-A72-Kernen sowie einem weiteren Dual-Core-Cluster bestehend aus ARM Cortex-R5F-Kernen, die auf Echtzeit-Berechnungen optimiert sind. All die Engines und Logikzellen sind über einen schnellen Interconnect miteinander verbunden. Hinzu kommen schnelle I/O-Blöcke 600G-Ethernet, 112G-PAM4-Transceiver und PCI-Express 5.0. PCI-Express 5.0 kommt dann zum Einsatz, wenn ein Versal Premium mit einem Host kommunizieren bzw. daran angebunden werden soll. Xilinx spricht hier von PCI-Express 5.0 mit acht Lanes, wenn CCIX verwendet werden soll und PCI-Express 5.0 mit vier Lanes, wenn die Anbindung per CXL (Compute Express Link) erfolgt. Dies könnte auch ein erster Ausblick auf die Datenraten sein, die mit CCIX und CXL geplant sind.

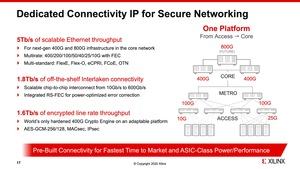

Je nach Variante des Xilinx Versal Premium stehen unterschiedlich viele MACs für die Ethernet-Anbindungen zur Verfügung. Wir sprechen hier von bis zu sieben der schnellen 600G-Ethernet-MACs. Zukünftig sollen sogar 800 GBit/s per optischer Verbindung möglich sein. Ein solches Modell hat man zum aktuellen Zeitpunkt jedoch noch nicht vorgestellt.

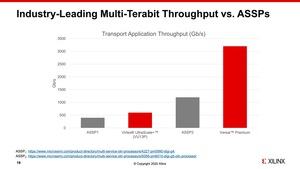

Insgesamt kann eine Datenrate von 5 TBit/s per Ethernet durch den Chip geroutet werden. Auch eine Ver- und Entschlüsselung der Daten ist möglich. Dann werden etwa 1,6 TBit/s erreicht. Werden auch die 112G PAM4 Transceiver genutzt, sind 9 TBit/s an Gesamtdatenrate möglich.

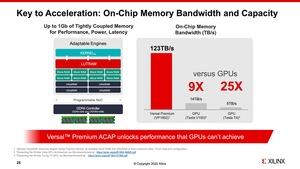

Auf dem Chip selbst ist in den Engines und Logikzellen eigener RAM verbaut. Die verschiedenen Caches (LUTRAM, Block RAM, UltraRAM) zusammengenommen sollen es ein Gigabyte an Speicherkapazität sein. Die On-Chip-Speicherbandbreite gibt Xilinx mit 123 TB/s an. Außerdem steht ein DDR4-Speichercontroller zur Verfügung, der DDR4-3200 und LPDDR4-4266 ansprechen kann.

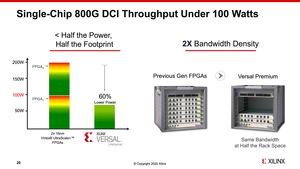

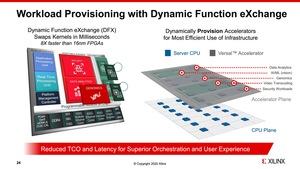

Aufgrund der Änderungen in der Architektur und der Fertigung (7 statt 16 nm) sollen die neuen Chips deutlich sparsamer sein. Die Fertigung selbst findet bei TSMC statt. Bis zu 25 % an Einsparung werden durch die Fertigung erreicht, zwischen 75 und 80 durch die Architektur. Die Einsparung bei der Leistungsaufnahme wirkt sich zusammen mit der hohen Integrationsdichte auf die Kosten für den Einsatz eines solchen Systems aus.

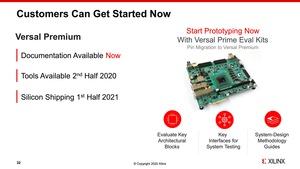

Kunden für die Xilinx Versal Premium sind vor allem Kommunikationsausrüster. Aktuell spricht Xilinx nur über ein theoretisches Produkt. In der zweiten Jahreshälfte 2020 sollen die ersten Tools zur Verfügung stehen und in der ersten Jahreshälfte 2021 sollen die ersten Chips ausgeliefert werden.