Werbung

Im Rahmen des Architecture Day 2020 hat Intel einige Ankündigungen gemacht. Diese betreffen die zukünftigen Mobil-Prozessoren Tiger Lake mit ihren Willow-Cove-Kernen, aber es gibt auch Details zur Xe-Grafikarchitektur, den verschiedenen Ausbaustufen und vor allem den Einsatzgebieten.

Intel will sich auch endlich von der problembehafteten Fertigung in 10 nm lösen bzw. diese in eine Form überführt haben, die endlich die gesteckten Ziele erfüllen kann. Abgesehen von den mobilen Ice-Lake-Prozessoren (Core i7-1065G7 im Test) und dem Compute-Die der Lakefield-Prozessoren (Core i5-L16G7 im Test) fertigt Intel alle wichtigen CPUs bis heute in 14 nm. Dies gilt für die Desktop-Modelle (Comet Lake-S) ebenso wie für die Servervarianten (Cooper Lake-SP).

Einige ASICs und Atom-Modelle werden zwar ebenfalls bereits in 10 nm gefertigt, das Fehlen der Desktop- und Servermodelle zum jetzigen Zeitpunkt zeigt aber, dass 10nm und 10nm+ nicht die Leistungsziele in allen Bereichen abdecken können. Spannend ist Intels Ankündigung auch dahingehend, dass man erst kürzlich verkündete, dass man die ersten Chips aus der Fertigung in 7 nm um sechs Monate wird verschieben müssen. Die Fertigung in 10 nm wird für Intel also noch eine wichtige Rolle spielen – trotz aller Probleme.

10nm SuperFin Technology

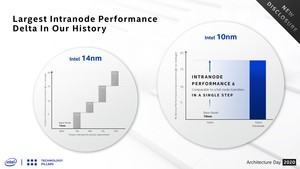

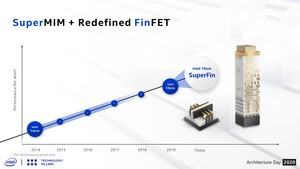

Für die Tiger-Lake-Prozessoren und wohl auch alle zukünftigen Chips aus der Fertigung in 10 nm hat Intel einige Verbesserungen einfließen lassen. Diese fasst man unter dem Begriff "10nm SuperFin Technology" zusammen. Intel spricht in diesem Zusammenhang von einer der größten Verbesserung innerhalb einer Fertigungsgröße (Intranode) in der Geschichte des Unternehmens.

Anstatt einen Begriff wie 10nm++ zu verwenden, gibt Intel den Verbesserungen mit 10nm SuperFin Technology einen fürs Marketing bedeutsamen Namen. Was dahinter steckt, schauen wir uns nun an.

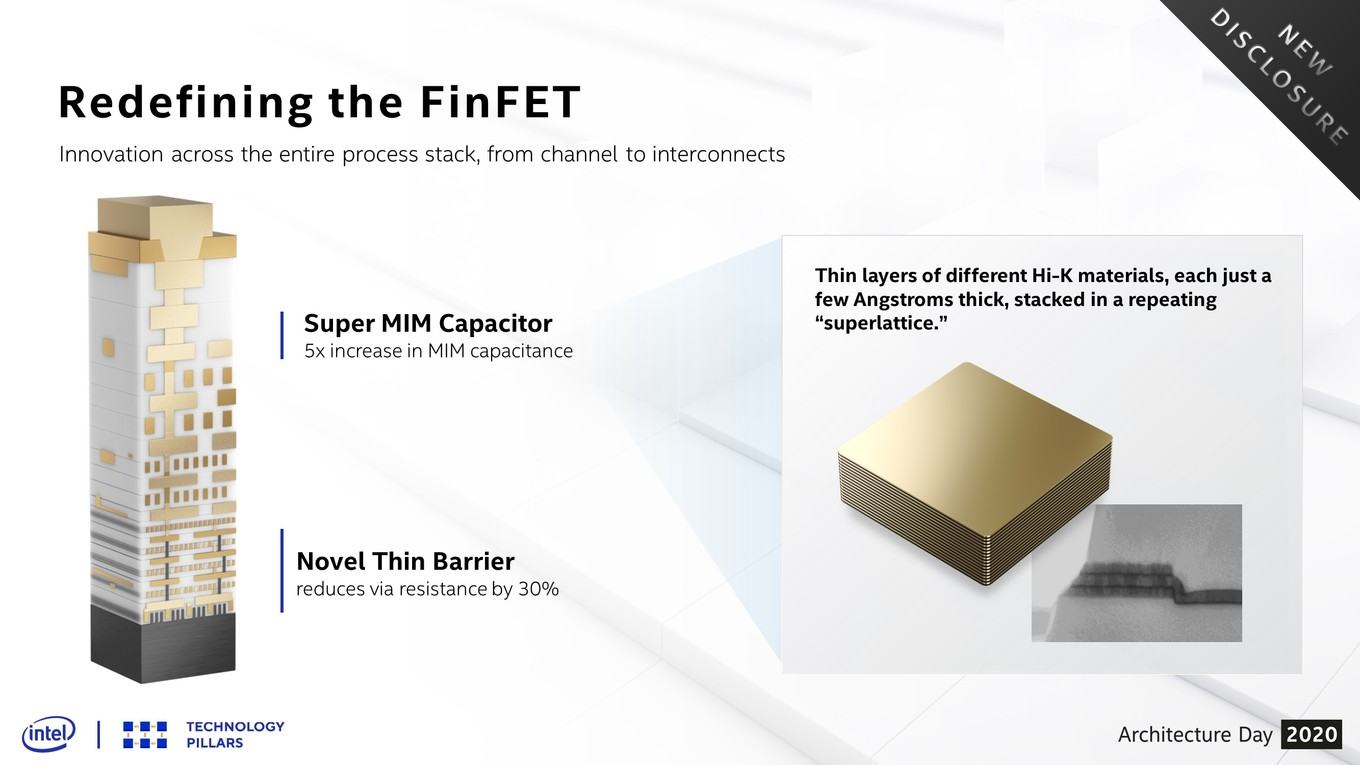

In der 10nm SuperFin Technology vereint Intel die Eigenschaften der FinFET-Technik mit einem Super metal insulator metal (MIM) Kondensator. Damit bieten die Transistoren eine verbesserte Epitaxie (spezielles Dotierprofil) für die Source und Drain. Ebenfalls verbessert wurde der Gate-Prozess und es gibt einen zusätzlichen Gate-Abstand.

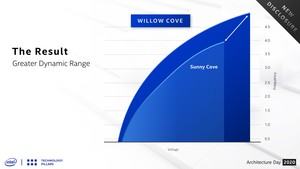

Durch ein verbessertes Dotierprofil in den Siliciumschichten auf einem Siliciumsubstrat für Source und Drain des Transistors und die damit verbundene höhere Reinheit in diesen Epitaxie-Schichten kann Intel den Widerstand verringern, um mehr Strom durch den Kanal fließen zu lassen. Dies geht Hand in Hand mit den Verbesserungen im Gate, die eine höhere Kanalmobilität ermöglichen sollen, wodurch sich die Ladungsträger schneller bewegen können. Dort, wo höhere Ströme erforderlich sind, hat Intel den Gate-Abstand zudem erhöht.

Unterstützt wird dies durch dünnere Barrieren zur Reduzierung des Durchgangswiderstands um 30 %. Im Vergleich zu den bisherigen Umsetzungen wird die Kapazität bei gleicher Grundfläche um das 5-fache erhöht und der Spannungsabfall reduziert. Möglich wird dies auch durch den Einsatz neuer Hi-K-Dielektrikumsmaterialien, die in ultradünnen Schichten von nur einigen Ångström Dicke (ein Ångström entspricht dem zehnmillionsten Teil eines Millimeters) gestapelt sind, um eine sich wiederholende "Supergitter"-Struktur zu bilden.

Neben den Tiger-Lake-Prozessoren wird auch die nächste Generation der Xeon-Modelle Sapphire Rapids auf die Fertigung in 10 nm bzw. auf die 10nm SuperFin Technology setzen.

Die Verbesserungen in der Fertigung in 10 nm, zusammengefasst als 10nm SuperFin Technology, sind Intels Rettungsanker, um diesen Fertigungsschritt noch zu retten. Dies ist auch notwendig, denn in den bisherigen Ausführungen ist Intels 10-nm-Fertigung nicht in der Lage die eigens gesteckten Ziele zu erreichen.

Intel informierte uns mittels eines recht kurz gefassten Fact Sheet über die Neuerungen des Architecture Day 2020. Weitere Informationen werden wir erst nach der Veröffentlichung dieser News erhalten und diese dann entsprechend ergänzen.