Werbung

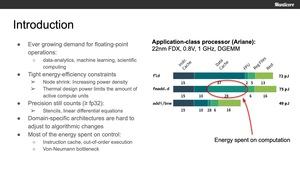

Auf der HotChips-Konferenz zeigten Wissenschaftler der Systems Laboratory der ETH Zürich sowie der Universität von Bologna ein Multi-Chiplet-Konzept auf Basis eines RISC-V-Designs. HBM2, ein Chiplet-Design, schneller Interconnect und bis zu 4.096 Kerne zeigen die Richtung, in die es gehen soll. Mit dem Manticore getauften Design zielt man klar auf ein HPC-Design für einen solchen Prozessor ab.

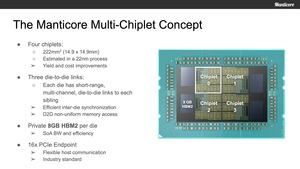

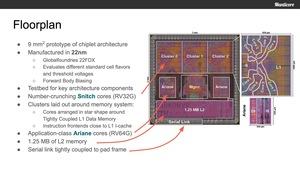

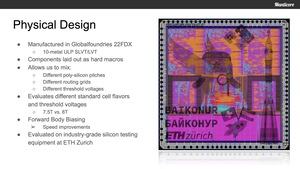

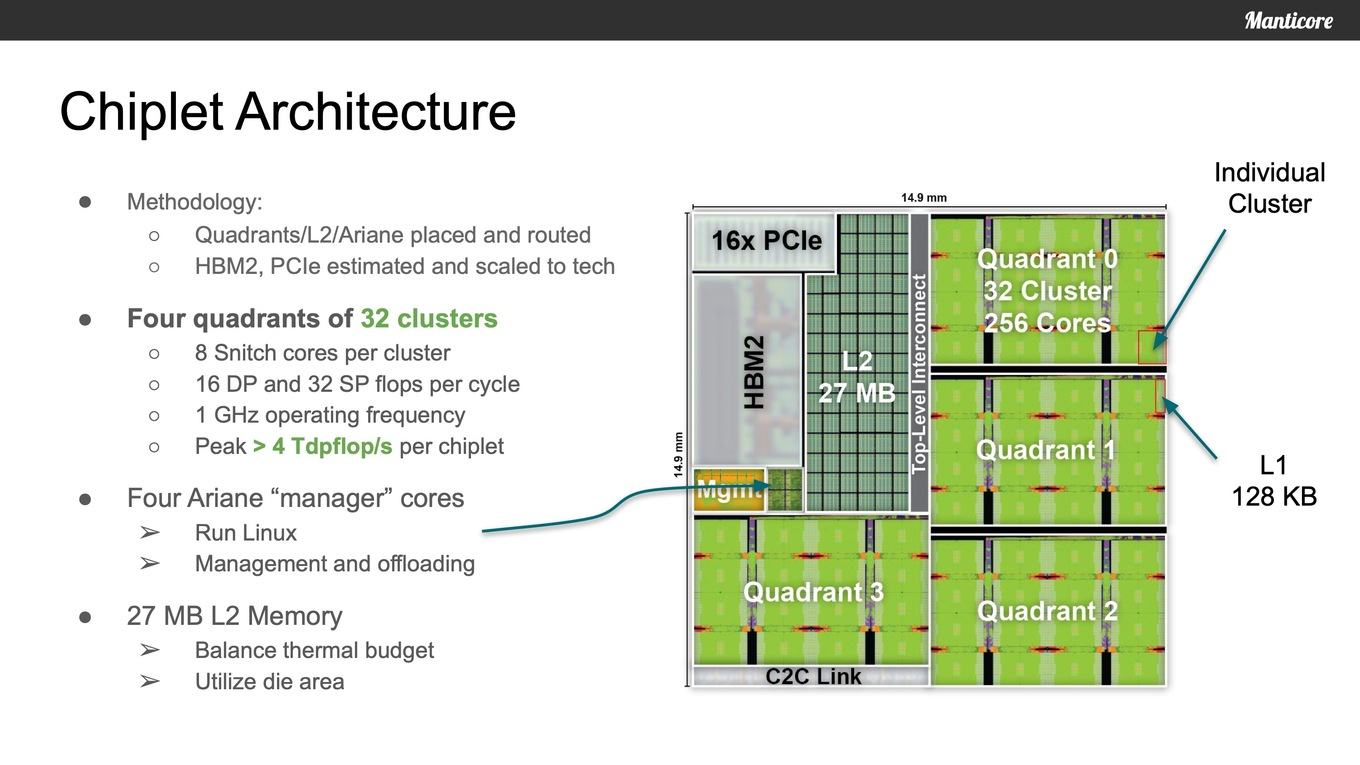

Das Manticore-Konzept besteht aus vier Chiplets. Jedes dieser Chiplets misst 222 mm² (14,9 x 14,9mm). Die Fertigung könnte bei GlobalFoundries in 22 nm (22FDX) stattfinden. Diese Prozesstechnologie wurde gewählt, weil die Ausbeute und Kosten in einem guten Verhältnis stehen. Jedes der vier Chiplets ist mit den anderen dreien per Interconnect verbunden. Pro Chiplet sind 8 GB an HBM2 geplant. Zur Anbindung des Manticore-Konzepts soll ein PCI-Express-Interface genutzt werden.

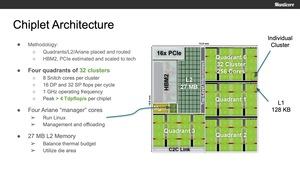

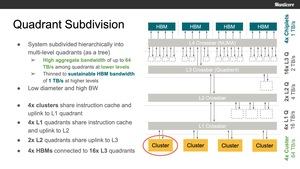

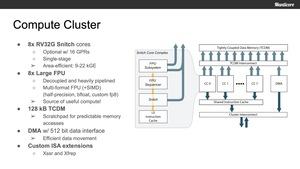

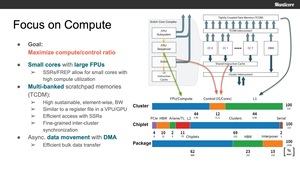

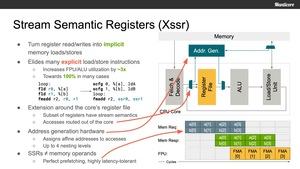

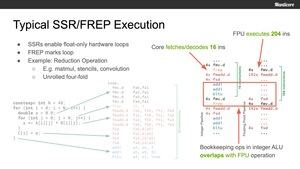

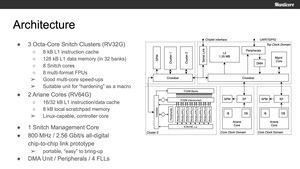

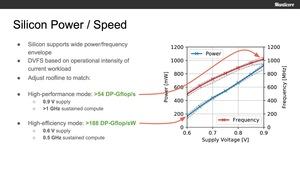

Jedes der Chiplets besteht aus vier Quadranten (in denen sich die Rechenkerne befinden), einem 27 MB großen L2-Cache, einem HBM2-Speicherinterface sowie dem PCI-Express-Controller. Jeder der vier Quadranten besteht aus 32 Clustern bzw. 256 Kernen – jedes Cluster besitzt also acht RV32G Snitch Kerne. Pro Takt können die Kerne 16DP- und 32SP-Operationen ausführen. Die Taktfrequenz soll bei 1.000 MHz liegen. Auf jedem Chiplet befinden sich außerdem vier Management-Kerne namens Ariane. Auf diesen kann ein Linux arbeiten.

Die RV32G-Kerne haben einen 8 kB großen L1-Instruction- und einen 128 kB großen L1-Data-Cache. Die großen Caches für die Daten sind notwendig, um die zu verarbeitenden Daten so nahe wie möglich am eigentlichen Rechenkern behalten zu können. Dies trifft auch auf den großen L2-Cache sowie den HBM2 zu. Die Ariane-Kerne (RV64G) haben ein anderes Design und bieten daher 16/32 kB an L1-Instruction/Data-Cache.

Einen solch großen Chip können die Wissenschaftler nicht einfach so fertigen lassen. Dies wäre zu aufwendig und kostenintensiv. Also hat man einen Prototypen der Chiplet-Architektur fertigen lassen. Dieser hat eine Fläche von gerade einmal 9 mm². Man will hier die wichtigsten Komponenten testen können – darunter die RV32G Snitch Kerne, 1,25 MB an L2-Cache und die Ariane-Kerne auf Basis eines RV64G-Designs.

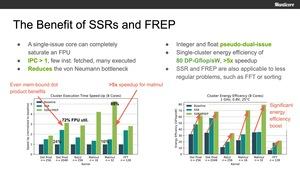

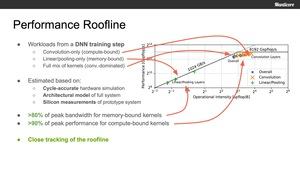

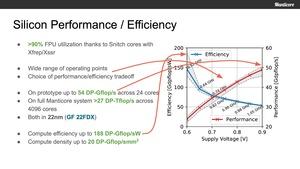

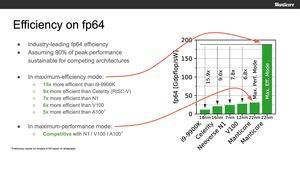

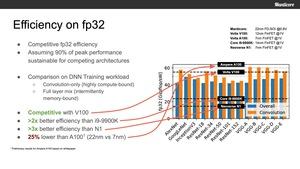

Hinsichtlich der Rechenleistung und Effizienz muss man sich auf Projektionen verlassen, die auf Basis des Prototyps erstellt wurden. Demnach käme das Manticore-Konzept auf eine Rechenleistung im Bereich einer GV100-GPU von NVIDIA – je nach Art der Berechnungen natürlich. Als HPC-Chip stehen die FP64, also Berechnungen bei doppelter Genauigkeit, im Fokus. Auf der Spannungs/Takt-Kurve entsprechend getrimmt wäre das Manticore-Konzept im den Faktor fünf effizienter als ein A100-Beschleuniger von NVIDIA. Hinsichtlich der FP32-Rechenleistung ist man etwas im Nachteil, aber noch immer besser als anderen Designs.

In einem nächsten Schritt soll nun ein Quad-Chiplet-Prototyp hergestellt werden. Dabei wird es sich aber noch nich um ein vollintegriertes Package handeln. Zunächst einmal will man Chip-Prototypen mit FinFET-Komponenten fertigen lassen, um die Vorteile einer modernen Fertigung mit einfließen zu lassen.