News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

RISC-V

-

Tenstorrent Dev Day: Blackhole mit neuen RISC-V-Kernen können bestellt werden

Auf seinem Dev Day hat Tenstorrent die nächste Generation seiner RISC-V-Beschleuniger vorgestellt, die auch ab sofort bestellt werden können. Die letzten Div-Kits mit der vorherigen Generation (Wormhole) können in einer luft- und wassergekühlten Version seit Mitte des vergangenen Jahres vorbestellt werden. Blackhole ist eine Weiterentwicklung von Wormhole. Die betrifft fast alle Aspekte der Architektur bzw. des Aufbaus des Chips. Die Tensix... [mehr]

Auf seinem Dev Day hat Tenstorrent die nächste Generation seiner RISC-V-Beschleuniger vorgestellt, die auch ab sofort bestellt werden können. Die letzten Div-Kits mit der vorherigen Generation (Wormhole) können in einer luft- und wassergekühlten Version seit Mitte des vergangenen Jahres vorbestellt werden. Blackhole ist eine Weiterentwicklung von Wormhole. Die betrifft fast alle Aspekte der Architektur bzw. des Aufbaus des Chips. Die Tensix... [mehr] -

RISC-V Edition: Framework bietet Entwickler-Board für Laptop 13 an

Framework bietet für sein modulares und frei konfigurierbares Notebook-Design Laptop 13 nun auch ein Mainboard mit RISC-V- Prozessor an. Das Framework Laptop 13 RISC-V Edition Mainboard wurde zusammen mit DeepComputing entwickelt und soll einen leichten Zugang zur Open-Source-Architektur RISC-V ermöglichen. Beim verwendeten Prozessor handelt es sich um den StarFive JH7110, der mit vier SiFive U74 RISC-V-Kernen ausgestattet ist. Die Kerne... [mehr]

Framework bietet für sein modulares und frei konfigurierbares Notebook-Design Laptop 13 nun auch ein Mainboard mit RISC-V- Prozessor an. Das Framework Laptop 13 RISC-V Edition Mainboard wurde zusammen mit DeepComputing entwickelt und soll einen leichten Zugang zur Open-Source-Architektur RISC-V ermöglichen. Beim verwendeten Prozessor handelt es sich um den StarFive JH7110, der mit vier SiFive U74 RISC-V-Kernen ausgestattet ist. Die Kerne... [mehr] -

RISC-V: Qualcomm kündigt ersten Chips für Android-Plattform an

Qualcomm hat bekannt gegeben, dass das Unternehmen seine langjährige Zusammenarbeit mit Google weiter ausbauen möchte, um RISC-V-basierte Wearables-Lösungen voranzutreiben. Ziel ist eine RISC-V-CPU, die für die Verwendung mit Wear OS, einem Ableger von Android, von Google gedacht ist. Diese will Qualcomm nutzen, um die Wearable-Plattform weltweit kommerziell zum Erfolg zu führen. Qualcomm erklärt, dass dieses erweiterte Framework dazu... [mehr]

Qualcomm hat bekannt gegeben, dass das Unternehmen seine langjährige Zusammenarbeit mit Google weiter ausbauen möchte, um RISC-V-basierte Wearables-Lösungen voranzutreiben. Ziel ist eine RISC-V-CPU, die für die Verwendung mit Wear OS, einem Ableger von Android, von Google gedacht ist. Diese will Qualcomm nutzen, um die Wearable-Plattform weltweit kommerziell zum Erfolg zu führen. Qualcomm erklärt, dass dieses erweiterte Framework dazu... [mehr] -

RISC-V: Zahlreiche Forschungsprojekte zur Stärkung der technologischen Souveränität Europas

Die quelloffene Befehlsarchitektur RISC-V, kurz für Reduced Instruction Set Computer V, wurde mit dem Ziel entworfen, Mikroprozessoren ohne Erwerb einer Lizenz entwerfen und fertigen zu können. Dabei sollen mit RISC-V energieeffiziente und gleichzeitig performante Prozessoren realisiert werden können. Die Zugänglichkeit von RISC-V ermöglicht es den Entwicklern zudem, Prozessoren zu entwerfen, die auf spezifische Anforderungen zugeschnitten... [mehr]

Die quelloffene Befehlsarchitektur RISC-V, kurz für Reduced Instruction Set Computer V, wurde mit dem Ziel entworfen, Mikroprozessoren ohne Erwerb einer Lizenz entwerfen und fertigen zu können. Dabei sollen mit RISC-V energieeffiziente und gleichzeitig performante Prozessoren realisiert werden können. Die Zugänglichkeit von RISC-V ermöglicht es den Entwicklern zudem, Prozessoren zu entwerfen, die auf spezifische Anforderungen zugeschnitten... [mehr] -

RISE: Die Abkehr von ARM organisiert sich

Es ist kein Geheimnis, dass RISC-V, die freie und offene Befehlssatzarchitektur, derzeit eine gewisse Konjunktur erlebt. Einige der größten Technologieanbieter versuchen sich momentan vom x86-Standard und den restriktiven und teuer gewordenen ARM-Lizenzen zu lösen, um mithilfe von RISC-V eigene, spezialisierte Prozessoren zu entwickeln, ohne dass dabei Lizenzgebühren an die etablierten Unternehmen fällig werden. Auch Staaten wie China haben... [mehr]

Es ist kein Geheimnis, dass RISC-V, die freie und offene Befehlssatzarchitektur, derzeit eine gewisse Konjunktur erlebt. Einige der größten Technologieanbieter versuchen sich momentan vom x86-Standard und den restriktiven und teuer gewordenen ARM-Lizenzen zu lösen, um mithilfe von RISC-V eigene, spezialisierte Prozessoren zu entwickeln, ohne dass dabei Lizenzgebühren an die etablierten Unternehmen fällig werden. Auch Staaten wie China haben... [mehr] -

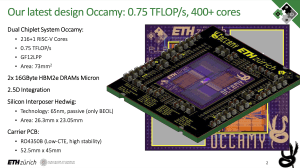

432 RISC-V-Kerne: Effizienter Number-Cruncher aus Europa

Auf der DATE-Konferenz (Design, Automation and Test in Europe) haben die Entwickler von der ETH Zürich sowie der Universität von Bologna zusammen mit den beteiligten Unternehmen, bzw. Plattform-Entwicklern wie PULP (Parallel Ultra-Low Power), GlobalFoundries, Rambus, Micron, Synopsys und Avery den Occamy vorgestellt, einen HPC-Chip mit Chiplet-Design und insgesamt 432 RISC-V-Kernen. Der Occamy besteht aus zwei Compute-Chiplets, welche jeweils... [mehr]

Auf der DATE-Konferenz (Design, Automation and Test in Europe) haben die Entwickler von der ETH Zürich sowie der Universität von Bologna zusammen mit den beteiligten Unternehmen, bzw. Plattform-Entwicklern wie PULP (Parallel Ultra-Low Power), GlobalFoundries, Rambus, Micron, Synopsys und Avery den Occamy vorgestellt, einen HPC-Chip mit Chiplet-Design und insgesamt 432 RISC-V-Kernen. Der Occamy besteht aus zwei Compute-Chiplets, welche jeweils... [mehr] -

SoftBank reicht Pläne ein: Arm soll an die Börse

In Wirtschaftskreisen wird schon länger gemunkelt, dass die SoftBank Group den britische Chipentwickler ARM Limited (arm) an die Börse bringen will. Diese Annahme resultierte aus den sich verteuernden Lizenzen zum Nutzen der Architektur. Tatsächlich hat der Konzern kürzlich seine Absichten offiziell bekannt gegeben. Demnach wurden der US-Börsenaufsicht Securities and Exchange Commission (SEC) bereits erste Entwürfe für den Börsengang... [mehr]

In Wirtschaftskreisen wird schon länger gemunkelt, dass die SoftBank Group den britische Chipentwickler ARM Limited (arm) an die Börse bringen will. Diese Annahme resultierte aus den sich verteuernden Lizenzen zum Nutzen der Architektur. Tatsächlich hat der Konzern kürzlich seine Absichten offiziell bekannt gegeben. Demnach wurden der US-Börsenaufsicht Securities and Exchange Commission (SEC) bereits erste Entwürfe für den Börsengang... [mehr] -

Imagination Technologies stellt RISC-V-Prozessor IMG RTXM-2200 vor

Ende des vergangenen Jahres kündigte Imagination Technologies an, dass man mit der Catapult-Serie an einer Reihe an Prozessoren auf Basis der quelloffenen Prozessor-Architektur RISC-V arbeite. Nun hat man mit dem RTXM-2200 eine erste Echtzeit-CPU vorgestellt. Es handelt sich bei der RTXM-2200 um eine auf Embedded Anwendungen optimierte CPU, die auf 32-Bit-Basis arbeitet. Als in-Order, Dual-Issue-Design mit einer elf Stages... [mehr]

Ende des vergangenen Jahres kündigte Imagination Technologies an, dass man mit der Catapult-Serie an einer Reihe an Prozessoren auf Basis der quelloffenen Prozessor-Architektur RISC-V arbeite. Nun hat man mit dem RTXM-2200 eine erste Echtzeit-CPU vorgestellt. Es handelt sich bei der RTXM-2200 um eine auf Embedded Anwendungen optimierte CPU, die auf 32-Bit-Basis arbeitet. Als in-Order, Dual-Issue-Design mit einer elf Stages... [mehr] -

NVIDIAs GPU System Processor soll Last von der CPU nehmen

Im Inneren der GPUs von NVIDIA arbeitet seit Jahren auch ein GPU System Processor (GSP). Dieser basierte bis etwa 2017 auf einem Arm-Design, NVIDIA entwickelte aber ein RISC-V-Design bzw. implementierte ein solches. Der GSP übernimmt beispielsweise die Zuteilung bestimmter Ressourcen. Dies geschieht GPU-intern aufgrund der geringeren Latenzen schneller, als über ein Offloading an den Hauptprozessor. Im Linux-Treiber 510.39... [mehr]

Im Inneren der GPUs von NVIDIA arbeitet seit Jahren auch ein GPU System Processor (GSP). Dieser basierte bis etwa 2017 auf einem Arm-Design, NVIDIA entwickelte aber ein RISC-V-Design bzw. implementierte ein solches. Der GSP übernimmt beispielsweise die Zuteilung bestimmter Ressourcen. Dies geschieht GPU-intern aufgrund der geringeren Latenzen schneller, als über ein Offloading an den Hauptprozessor. Im Linux-Treiber 510.39... [mehr] -

Imagination entwickelt eigene RISC-V-Kerne

Eine der ersten größeren Ankündigungen auf dem RISC-V Summit kommt vom britischen Chipentwickler Imagination – bis zuletzt vor allem bekannt für seine GPU-IP, die sich überwiegend in den ersten A-Series-Chips von Apple einen Namen gemacht hat. Inzwischen entwickelt Apple seine GPUs selbst und somit brach ein großer Bereich für Imagination weg. Zuletzt machte ein chinesischer Hersteller mit Grafikkarten auf sich aufmerksam, deren GPUs auf dem... [mehr]

Eine der ersten größeren Ankündigungen auf dem RISC-V Summit kommt vom britischen Chipentwickler Imagination – bis zuletzt vor allem bekannt für seine GPU-IP, die sich überwiegend in den ersten A-Series-Chips von Apple einen Namen gemacht hat. Inzwischen entwickelt Apple seine GPUs selbst und somit brach ein großer Bereich für Imagination weg. Zuletzt machte ein chinesischer Hersteller mit Grafikkarten auf sich aufmerksam, deren GPUs auf dem... [mehr] -

Schneller RISC-V: SiFive P650 macht dem Cortex-A77 Konkurrenz

Nach mehreren Vorab-Ankündigungen und noch vor dem RISC-V Summit in wenigen Tagen hat SiFive den Performane-Core P650 vorgestellt. Mit diesem will sich SiFive auf das Leistungsniveau eines Cortex-A77 von Arm herangearbeitet haben. Laut SiFive gibt es im General-Purpose-Umfeld aktuell keinen schnelleren RISC-V-Kern. Je nach Ausbaustufe des Clusters hat jeder Kern 256 KB an L1-Cache (je 128 kB für Daten und Instruktionen).{razuna... [mehr]

Nach mehreren Vorab-Ankündigungen und noch vor dem RISC-V Summit in wenigen Tagen hat SiFive den Performane-Core P650 vorgestellt. Mit diesem will sich SiFive auf das Leistungsniveau eines Cortex-A77 von Arm herangearbeitet haben. Laut SiFive gibt es im General-Purpose-Umfeld aktuell keinen schnelleren RISC-V-Kern. Je nach Ausbaustufe des Clusters hat jeder Kern 256 KB an L1-Cache (je 128 kB für Daten und Instruktionen).{razuna... [mehr] -

RISC-V-Konferenz: Details zur Chiplet-Architektur und dem P550-Nachfolger

Vom 6. bis zum 8. Dezember wird das RISC-V Summit stattfinden. SiFive kündigt für die Konferenz einige Neuigkeiten an. Auf der Supercomputing 2021 spielte das Thema RISC-V noch eine untergeordnete Rolle, dies soll sich jedoch in Zukunft ändern. Chiplets und der Nachfolger des P550 sollen der Fokus für SiFive sein. Bereits vor einigen Wochen gab SiFive erste Details zum Next-Gen P-Series-Kern preis. Dieser soll noch einmal um 50 % schneller als... [mehr]

Vom 6. bis zum 8. Dezember wird das RISC-V Summit stattfinden. SiFive kündigt für die Konferenz einige Neuigkeiten an. Auf der Supercomputing 2021 spielte das Thema RISC-V noch eine untergeordnete Rolle, dies soll sich jedoch in Zukunft ändern. Chiplets und der Nachfolger des P550 sollen der Fokus für SiFive sein. Bereits vor einigen Wochen gab SiFive erste Details zum Next-Gen P-Series-Kern preis. Dieser soll noch einmal um 50 % schneller als... [mehr] -

SiFive gibt Vorschau auf den Nachfolger des RISC-V-P550-Kerns

Im Frühsommer stellte SiFive mit den P550 die vorläufig schnellsten RISC-V-Kerne vor. Davon war offenbar auch Intel überzeugt und bietet schon bald entsprechende Designs Kunden des Intel Foundry Services (IFS) an. Bereits 2022 will Intel mit der Horse -Creek-RISC-V-Entwicklungsplattform einen Prozess anbieten, der Kerne, bzw. Cluster und ganze SoCs wie den P550 in 7 nm fertigen lässt. Auf der Linley-Konferenz sprach der... [mehr]

Im Frühsommer stellte SiFive mit den P550 die vorläufig schnellsten RISC-V-Kerne vor. Davon war offenbar auch Intel überzeugt und bietet schon bald entsprechende Designs Kunden des Intel Foundry Services (IFS) an. Bereits 2022 will Intel mit der Horse -Creek-RISC-V-Entwicklungsplattform einen Prozess anbieten, der Kerne, bzw. Cluster und ganze SoCs wie den P550 in 7 nm fertigen lässt. Auf der Linley-Konferenz sprach der... [mehr] -

Erster RISC-V-Beschleuniger des EU-Prozessors startet

Die European Processor Initiative (EPI) macht einen ersten erfolgreichen Schritt hin zu HPC-Hardware, die in Europa entwickelt und später auch betrieben wird. Für den EU-Prozessor fährt man dabei mehrgleisig und will die Hardware auf verschiedene Architektur-Beine stellen. Zentrale Komponente wird ein Rhea-HPC-SoC auf Basis von 72 Arm-Kernen nebst HBM2 sein. Doch es werden auch spezielle Beschleuniger entwickelt, die auf RISC-V... [mehr]

Die European Processor Initiative (EPI) macht einen ersten erfolgreichen Schritt hin zu HPC-Hardware, die in Europa entwickelt und später auch betrieben wird. Für den EU-Prozessor fährt man dabei mehrgleisig und will die Hardware auf verschiedene Architektur-Beine stellen. Zentrale Komponente wird ein Rhea-HPC-SoC auf Basis von 72 Arm-Kernen nebst HBM2 sein. Doch es werden auch spezielle Beschleuniger entwickelt, die auf RISC-V... [mehr] -

SiFive P550: Auch Intel wird den schnellsten RISC-V-Kern in 7 nm nutzen

Wurde in der vergangenen Woche über einen möglichen Kauf von SiFive durch Intel berichtet, gibt es nun Neuigkeiten, an denen ebenfalls beide Unternehmen beteiligt sind. SiFive hat mit dem P550 den aktuell schnellsten RISC-V-Kern angekündigt. Diesen will Intel für seine RISC-V-Entwicklungsplattform verwenden und bieten ihn damit auch Kunden des Intel Foundry Services (IFS) an. Beim P550 handelt es sich eigentlich um ein... [mehr]

Wurde in der vergangenen Woche über einen möglichen Kauf von SiFive durch Intel berichtet, gibt es nun Neuigkeiten, an denen ebenfalls beide Unternehmen beteiligt sind. SiFive hat mit dem P550 den aktuell schnellsten RISC-V-Kern angekündigt. Diesen will Intel für seine RISC-V-Entwicklungsplattform verwenden und bieten ihn damit auch Kunden des Intel Foundry Services (IFS) an. Beim P550 handelt es sich eigentlich um ein... [mehr] -

2 Milliarden US-Dollar: Intel soll Übernahmeangebot an SiFive gemacht haben

Intel soll ein Übernahmeangebot in Höhe von 2 Milliarden US-Dollar an SiFive gemacht haben. Bisher wollten beiden Unternehmen dies nicht bestätigen, der erste Bericht dazu stammt von Bloomberg. SiFive ist ein IP-Entwickler für Mikroarchitekturen auf Basis der freien RISC-V-Architektur. Geld verdienen will man über Lizenzgebühren für besagte Architekturen und Chipdesigns. SiFive arbeitet allerdings auch mit Auftragsfertigern... [mehr]

Intel soll ein Übernahmeangebot in Höhe von 2 Milliarden US-Dollar an SiFive gemacht haben. Bisher wollten beiden Unternehmen dies nicht bestätigen, der erste Bericht dazu stammt von Bloomberg. SiFive ist ein IP-Entwickler für Mikroarchitekturen auf Basis der freien RISC-V-Architektur. Geld verdienen will man über Lizenzgebühren für besagte Architekturen und Chipdesigns. SiFive arbeitet allerdings auch mit Auftragsfertigern... [mehr] -

SiFive und Samsung Foundry gehen Zusammenarbeit ein

Nachdem OpenFive vor einigen Wochen eine neue technische Umsetzung eines Interconnect-PHY für zukünftige Chiplet-Designs vorstellte und SiFive bekanntgegeben hat, dass ab sofort High-Performance-SoCs mit SiFive-IP bei TSMC in 5 nm gefertigt werden können, erfolgte in der vergangenen Woche die Vorstellung des Intelligence X280 Core-Designs, welches mit 512 Bit Vektoreinheiten sämtliche AI- und ML-Workloads beschleunigen... [mehr]

Nachdem OpenFive vor einigen Wochen eine neue technische Umsetzung eines Interconnect-PHY für zukünftige Chiplet-Designs vorstellte und SiFive bekanntgegeben hat, dass ab sofort High-Performance-SoCs mit SiFive-IP bei TSMC in 5 nm gefertigt werden können, erfolgte in der vergangenen Woche die Vorstellung des Intelligence X280 Core-Designs, welches mit 512 Bit Vektoreinheiten sämtliche AI- und ML-Workloads beschleunigen... [mehr] -

RISC-V-SoC mit HBM3-Subsystem kann in 5 nm gefertigt werden

Nachdem OpenFive in der vergangenen Woche eine neue technische Umsetzung eines Interconnect-PHY für zukünftige Chiplet-Designs vorstellte, folgte jetzt die Ankündigung, dass man nun High-Performance-SoCs bei TSMC in 5 nm fertigen könne. Ein Referenzdesign habe den Tape Out erfolgreich geschafft und mache damit den Weg frei, so dass Kunden ihrerseits Chips auf Basis der 5-nm-Fertigung entwickeln können. Nun ist eine Fertigung in 5 nm keine... [mehr]

Nachdem OpenFive in der vergangenen Woche eine neue technische Umsetzung eines Interconnect-PHY für zukünftige Chiplet-Designs vorstellte, folgte jetzt die Ankündigung, dass man nun High-Performance-SoCs bei TSMC in 5 nm fertigen könne. Ein Referenzdesign habe den Tape Out erfolgreich geschafft und mache damit den Weg frei, so dass Kunden ihrerseits Chips auf Basis der 5-nm-Fertigung entwickeln können. Nun ist eine Fertigung in 5 nm keine... [mehr] -

RV64X: RISC-V-GPU befindet sich in der Entwicklung

Die quelloffene CPU-Architektur RISC-V hat sich in einigen Bereich inzwischen breit gemacht und soll die Zukunft der CPU-Entwicklung durch den einfachen Zugang revolutionieren. Doch was in der Entwicklung noch fehlt, ist eine dazugehörige und ebenso quelloffene GPU. Das Unternehmen Pixilica will nun eine Grafikeinheit für SoCs entwicklen, deren Befehlssatz als RISC-V – RV64X bezeichnet wird und den in RISC-V... [mehr]

Die quelloffene CPU-Architektur RISC-V hat sich in einigen Bereich inzwischen breit gemacht und soll die Zukunft der CPU-Entwicklung durch den einfachen Zugang revolutionieren. Doch was in der Entwicklung noch fehlt, ist eine dazugehörige und ebenso quelloffene GPU. Das Unternehmen Pixilica will nun eine Grafikeinheit für SoCs entwicklen, deren Befehlssatz als RISC-V – RV64X bezeichnet wird und den in RISC-V... [mehr] -

HiFive Unmatched: Mini-ITX-Board mit RISC-V-Prozessor (Update)

RISC-V-Designs sind auf dem Vormarsch und kommen bereits heute in vielen Chips als Co-Prozessor zum Einsatz – oft ohne dass der Nutzer der Hardware dies weiß. SiFive ist ein Startup, welches die Entwicklung derzeit besonders aggressiv vorantreibt. RISC-V ist als Hardware-Open-Source-Entwicklung ein ähnlich wichtiger Schritt, wie er dies Linux in der Softwarewelt ist. SiFive bietet zahlreiche unterschiedliche Core IP, die sich... [mehr]

RISC-V-Designs sind auf dem Vormarsch und kommen bereits heute in vielen Chips als Co-Prozessor zum Einsatz – oft ohne dass der Nutzer der Hardware dies weiß. SiFive ist ein Startup, welches die Entwicklung derzeit besonders aggressiv vorantreibt. RISC-V ist als Hardware-Open-Source-Entwicklung ein ähnlich wichtiger Schritt, wie er dies Linux in der Softwarewelt ist. SiFive bietet zahlreiche unterschiedliche Core IP, die sich... [mehr] -

Manticore: RISC-V Multi-Chiplet-Konzept mit HBM2 und 4.096 Kernen

Auf der HotChips-Konferenz zeigten Wissenschaftler der Systems Laboratory der ETH Zürich sowie der Universität von Bologna ein Multi-Chiplet-Konzept auf Basis eines RISC-V-Designs. HBM2, ein Chiplet-Design, schneller Interconnect und bis zu 4.096 Kerne zeigen die Richtung, in die es gehen soll. Mit dem Manticore getauften Design zielt man klar auf ein HPC-Design für einen solchen Prozessor ab. Das Manticore-Konzept besteht aus vier... [mehr]

Auf der HotChips-Konferenz zeigten Wissenschaftler der Systems Laboratory der ETH Zürich sowie der Universität von Bologna ein Multi-Chiplet-Konzept auf Basis eines RISC-V-Designs. HBM2, ein Chiplet-Design, schneller Interconnect und bis zu 4.096 Kerne zeigen die Richtung, in die es gehen soll. Mit dem Manticore getauften Design zielt man klar auf ein HPC-Design für einen solchen Prozessor ab. Das Manticore-Konzept besteht aus vier... [mehr] -

RISC-V wird schneller und sparsamer: SiFive Core IP 20G1

Das Thema RISC-V haben wir bisher etwas sträflich behandelt. Dabei ist RISC-V als Hardware-Open-Source-Entwicklung ein ähnlich wichtiger Schritt, wie er dies als Linux in der Softwarewelt ist. SiFive hat nun mit der Core IP 20G1 die nächste Generation in dieser Entwicklung vorgestellt. Mit der Core IP 20G1 wertet SiFive seine Produktpalette weit auf. Innerhalb der U7- und E2-Serie wird die Leistung um den Faktor 2,8 gesteigert. Zugleich... [mehr]

Das Thema RISC-V haben wir bisher etwas sträflich behandelt. Dabei ist RISC-V als Hardware-Open-Source-Entwicklung ein ähnlich wichtiger Schritt, wie er dies als Linux in der Softwarewelt ist. SiFive hat nun mit der Core IP 20G1 die nächste Generation in dieser Entwicklung vorgestellt. Mit der Core IP 20G1 wertet SiFive seine Produktpalette weit auf. Innerhalb der U7- und E2-Serie wird die Leistung um den Faktor 2,8 gesteigert. Zugleich... [mehr] -

Chris Lattner arbeitet zukünftig bei SiFive an RISC-V-Designs

Chris Lattner, der unter anderem das Software-Team bei Tesla leitete, welches den Autopiloten entwickelt hat, ist ab sofort für SiFive als Senior Vice President im Platform Engineering tätig. Für SiFive ist er die prominenteste Neuanstellung in der bisher kurzen Schaffensphase des Unternehmens. Zehn Jahre war Lattner für Apple tätig und hat dort verschiedene LLVM-Projekte umgesetzt, die Compiler Frontends wie Clang oder... [mehr]

Chris Lattner, der unter anderem das Software-Team bei Tesla leitete, welches den Autopiloten entwickelt hat, ist ab sofort für SiFive als Senior Vice President im Platform Engineering tätig. Für SiFive ist er die prominenteste Neuanstellung in der bisher kurzen Schaffensphase des Unternehmens. Zehn Jahre war Lattner für Apple tätig und hat dort verschiedene LLVM-Projekte umgesetzt, die Compiler Frontends wie Clang oder... [mehr]