Werbung

OpenFive, eine Tochter von SiFive, die wiederum Kern-IP und Designs auf Basis der freien RISC-V-Befehlssatzstruktur entwickelt, hat ein Die-to-Die-Interface für Chiplets vorgestellt, welches eine Alternative zu Intels EMIB oder Foveros, bzw. den verschiedenen 3DFabric-Technologien von TSMC sein soll.

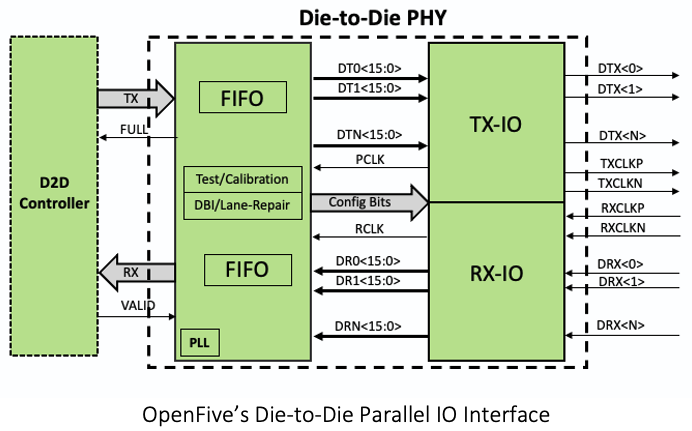

OpenFive bietet bereits verschiedene Die-to-Die-Interfaces (D2D) an, die mit einer Bandbreite von 1.024 Bit sowie bei einem Takt von 2 GHz bis zu 2 TBit/s erreichen. Das nun neue PHY, also das eigentliche physikalische Interface samt Controller, soll vor allem besonders effizient arbeiten und sich daher für den Einsatz auf Chiplet-SoC, also Chips, die mehrere einzelne Chips miteinander verbinden, eignen.

Konkret spricht OpenFive von 40 IOs pro Kanal, die jeweils 16 GBit/s übertragen können. Über diese ist eine Bandbreite von 1,75 TBit/s möglich und es lassen sich mehrere Kanäle zusammenschalten, so dass die Bandbreite recht schnell und einfach skaliert werden kann. In aktuellen Fertigungsverfahren ist so eine Bandbreitendichte von ~1,75 TBit/s pro Millimeter möglich. Zudem bietet das D2D-Interface eine Effizienz von weniger als 0,5 pJ/Bit.

Zum Vergleich: Der CoWoS von TSMC kommt auf 0,56 pJ/Bit und AMDs Infinity Fabric auf etwa 1,5 pJ/Bit. Das Foveros Die Interface (FDI) erreicht in den Lakefield-Prozessoren 0,2 pJ/Bit und das ebenfalls von Intel entwickelte EMIB bietet 0,3 pJ/Bit.

So einfach vergleichen lassen sich die verschiedenen Interconnect-Technologien allerdings nicht. Hier spielen noch weitere Faktoren eine Rolle – Abstand der Chips zueinander, EMIB ist beispielsweise ein serielles Interface, der Infinity Fabric hingegen ein paralleler Bus für größere Chip-Abstände.

"The D2D subsystem, including both the controller and PHY, provides best-in-class latency, performance and power profile for various IO, CPU and analog chiplets," sagt Ketan Mehta, Sr. Director, Product/Application Marketing, SoC IP, bei OpenFive.

Zum IP-Portfolio von OpenFive gehören neben D2D-Interfaces auch Ethernet-, USB- und Speicher-IP (HBM2/HBM2E). Core-IP, also die Designs der RISC-V-Kerne, werden hingegen bei SiFive entwickelt.