News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

Chiplet

-

Vertical Compute: imec Spin-Off soll Chiplet-Speichertechnologien entwickeln

Das imec Forschungszentrum hat mit Vertical Compute eine Ausgründung verkündet, welche als Deep-Tech-Halbleiter-Startup die Entwicklung von Chiplet-Technologien vorantreiben soll. Dabei konzentriert man sich auf die Herausforderungen im Bereich der Speicherintegration in Systemen, um die sogenannte Memory Wall zu umgehen, bzw. die Limitierungen im Bereich des schnellen und hochkapazitiven Speichers zu verschieben. In einer ersten... [mehr]

Das imec Forschungszentrum hat mit Vertical Compute eine Ausgründung verkündet, welche als Deep-Tech-Halbleiter-Startup die Entwicklung von Chiplet-Technologien vorantreiben soll. Dabei konzentriert man sich auf die Herausforderungen im Bereich der Speicherintegration in Systemen, um die sogenannte Memory Wall zu umgehen, bzw. die Limitierungen im Bereich des schnellen und hochkapazitiven Speichers zu verschieben. In einer ersten... [mehr] -

Intel Silicon Photonics: Optical Compute Interconnect (OCI) Chiplet soll endlich kommen

Schon seit Jahrzehnten spricht Intel über die Entwicklung einer optischen Übertragung von Daten im Nah- und Fernbereich. Tatsächlich ist Silicon Photonics in Netzwerkumgebungen bereits im Einsatz und das schon seit Jahren. Doch bisher gab es noch kein entscheidendes Unterscheidungsmerkmal zu anderen Übertragungen auf Basis von Lichtwellenleitern – zumindest keine besonders prominenten. Mit der Integration einer optischen Verbindung direkt in... [mehr]

Schon seit Jahrzehnten spricht Intel über die Entwicklung einer optischen Übertragung von Daten im Nah- und Fernbereich. Tatsächlich ist Silicon Photonics in Netzwerkumgebungen bereits im Einsatz und das schon seit Jahren. Doch bisher gab es noch kein entscheidendes Unterscheidungsmerkmal zu anderen Übertragungen auf Basis von Lichtwellenleitern – zumindest keine besonders prominenten. Mit der Integration einer optischen Verbindung direkt in... [mehr] -

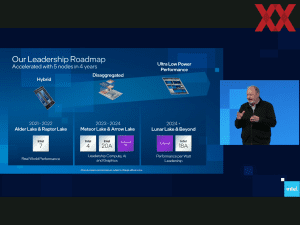

Meteor Lake: Das sind die Prozessoren für Notebooks

Bereits Mitte September präsentierte Intel alle technischen Details zu den Meteor-Lake-Prozessoren, die im Notebook-Segment mit Leistung und Effizienz überzeugen sollen. Das desintegrierte Design besteht aus mehreren Bausteinen, die zusammengesetzt dann den Prozessor ergeben: ein Compute-Tile, ein Graphics-Tile, ein SoC-Tile und ein I/O-Tile sitzen auf einem Base-Tile. Von Intel gefertigt werden aber nur der Compute- und Base-Tile, während die... [mehr]

Bereits Mitte September präsentierte Intel alle technischen Details zu den Meteor-Lake-Prozessoren, die im Notebook-Segment mit Leistung und Effizienz überzeugen sollen. Das desintegrierte Design besteht aus mehreren Bausteinen, die zusammengesetzt dann den Prozessor ergeben: ein Compute-Tile, ein Graphics-Tile, ein SoC-Tile und ein I/O-Tile sitzen auf einem Base-Tile. Von Intel gefertigt werden aber nur der Compute- und Base-Tile, während die... [mehr] -

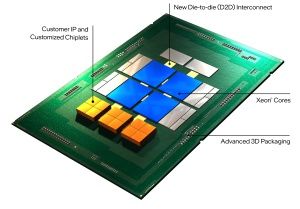

Multi-Chip-Packages: Intel über Glassubstrate, Die-Testing und Package-Fertigung

Bereits vielfach hatten wir darüber berichtet, dass nahezu alle Halbleiterhersteller einerseits die Entwicklung immer weiter optimierter Fertigungsgrößen mit immer feineren Strukturen vorantreiben und andererseits auch das Packaging zu einem immer wichtigeren Faktor wird. Die Chipentwicklung selbst bewegt sich immer an der Grenze des aktuell möglichen. Das Packaging eröffnet neue Möglichkeiten – sei es das Zusammenführen mehrere Compute-Chips... [mehr]

Bereits vielfach hatten wir darüber berichtet, dass nahezu alle Halbleiterhersteller einerseits die Entwicklung immer weiter optimierter Fertigungsgrößen mit immer feineren Strukturen vorantreiben und andererseits auch das Packaging zu einem immer wichtigeren Faktor wird. Die Chipentwicklung selbst bewegt sich immer an der Grenze des aktuell möglichen. Das Packaging eröffnet neue Möglichkeiten – sei es das Zusammenführen mehrere Compute-Chips... [mehr] -

Power-on: Intel startet Meteor-Lake-Chiplet SoC erfolgreich

Im Rahmen der Bekanntgabe der aktuellen Quartalszahlen, in denen Intel gute Trends im Server-Bereich vermeldete, dafür aber im Client-Segment zu kämpfen hat, verkündete Intel auch einige interessante Details in der Entwicklungsphase zukünftiger Prozessoren. Michelle Johnston Holthaus, EVP & GM der Client Computing Group bei Intel, verkündete via Twitter, dass man Meteor Lake erfolgreich eingeschaltet habe. Im Mai 2021 vermeldete Intel,... [mehr]

Im Rahmen der Bekanntgabe der aktuellen Quartalszahlen, in denen Intel gute Trends im Server-Bereich vermeldete, dafür aber im Client-Segment zu kämpfen hat, verkündete Intel auch einige interessante Details in der Entwicklungsphase zukünftiger Prozessoren. Michelle Johnston Holthaus, EVP & GM der Client Computing Group bei Intel, verkündete via Twitter, dass man Meteor Lake erfolgreich eingeschaltet habe. Im Mai 2021 vermeldete Intel,... [mehr] -

Gerüchte zu den kommende Flaggschiffen von AMD, Intel und NVIDIA

Zu den Grafikkarten der nächsten Generation kursieren seit kurzem wieder neue Gerüchte im Netz. Updates bezüglich der Informationen soll es zu AMDs Navi 3x, Intels Battlemage sowie NVIDIAs Ada Lovelace geben. Auch wenn die bekannten Leaker @Greymon55 und @kopite7kimi bereits vorab richtige Informationen lieferten, sind diese natürlich weiterhin mit Vorsicht zu genießen. Die beiden genannten Twitter-Nutzer veröffentlichten dort... [mehr]

Zu den Grafikkarten der nächsten Generation kursieren seit kurzem wieder neue Gerüchte im Netz. Updates bezüglich der Informationen soll es zu AMDs Navi 3x, Intels Battlemage sowie NVIDIAs Ada Lovelace geben. Auch wenn die bekannten Leaker @Greymon55 und @kopite7kimi bereits vorab richtige Informationen lieferten, sind diese natürlich weiterhin mit Vorsicht zu genießen. Die beiden genannten Twitter-Nutzer veröffentlichten dort... [mehr] -

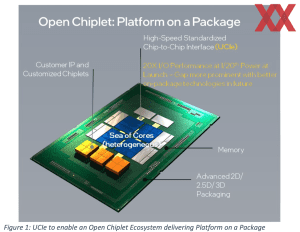

AMD, Intel, Arm und Co: UCIe soll Standard für Chiplet-Interconnects werden

Einige der großen Halbleiterhersteller haben heute angekündigt, einen neuen, offenen Standard für Chiplet-Interconnects ins Leben rufen zu wollen. Universal Chiplet Interconnect Express oder kurz UCIe tritt dabei in gewisser Weise in die Fußstapfen von PCI-Express, bzw. orientiert sich in der grundsätzlichen Herangehensweise daran. Ziel ist es gewisse Vorgaben zu entwickeln und in den beteiligten Unternehmen umsetzen zu lassen, die... [mehr]

Einige der großen Halbleiterhersteller haben heute angekündigt, einen neuen, offenen Standard für Chiplet-Interconnects ins Leben rufen zu wollen. Universal Chiplet Interconnect Express oder kurz UCIe tritt dabei in gewisser Weise in die Fußstapfen von PCI-Express, bzw. orientiert sich in der grundsätzlichen Herangehensweise daran. Ziel ist es gewisse Vorgaben zu entwickeln und in den beteiligten Unternehmen umsetzen zu lassen, die... [mehr] -

Intel legt Fond mit einer Milliarde US-Dollar zur Chiplet-Entwicklung auf

Intel bzw. die Intel-Töchter Intel Capital und Intel Foundry Services (IFS) haben heute die Einführung eines eine Milliarde US-Dollar schweren Fonds angekündigt, der Start-Ups und andere Unternehmen bei der Entwicklung neuer modularer Designs und Chips unterstützen soll. Ziel ist es Entwicklungen voranzutreiben, die als Bestandteil der Open Chiplet Platform nicht nur auf ARM- oder x86-Kerne verwenden, sondern die einen... [mehr]

Intel bzw. die Intel-Töchter Intel Capital und Intel Foundry Services (IFS) haben heute die Einführung eines eine Milliarde US-Dollar schweren Fonds angekündigt, der Start-Ups und andere Unternehmen bei der Entwicklung neuer modularer Designs und Chips unterstützen soll. Ziel ist es Entwicklungen voranzutreiben, die als Bestandteil der Open Chiplet Platform nicht nur auf ARM- oder x86-Kerne verwenden, sondern die einen... [mehr] -

AMD Ryzen 5800GX bestehend aus IOD+CCD+GPU - die Chiplet-Vollendung?

Mit den Ryzen-6000-Prozessoren führt AMD den Mix aus Zen- und GPU-Kernen in 6 nm gefertigt auf einen vorläufigen Höhepunkt. Doch der hier noch immer angewendete monolithische Ansatz ist bei weitem noch nicht so flexibel, wie die Chiplet-Strategie, die AMD auf dem Desktop- und Servermarkt immer stärker vorantreibt. Auf Twitter ist nun eine schematische Zeichnung aufgetaucht, die soweit geht einen Ryzen-Prozessor bestehend aus CCD (Core Complex... [mehr]

Mit den Ryzen-6000-Prozessoren führt AMD den Mix aus Zen- und GPU-Kernen in 6 nm gefertigt auf einen vorläufigen Höhepunkt. Doch der hier noch immer angewendete monolithische Ansatz ist bei weitem noch nicht so flexibel, wie die Chiplet-Strategie, die AMD auf dem Desktop- und Servermarkt immer stärker vorantreibt. Auf Twitter ist nun eine schematische Zeichnung aufgetaucht, die soweit geht einen Ryzen-Prozessor bestehend aus CCD (Core Complex... [mehr] -

Versteckter Bereich des M1 Max als Vorbereitung für ein Multi-Chip-Design

Gemeinsam mit den neuen MacBook-Pro-Modelle stellten Apple auch die neuesten Ableger der M1-SoC-Generation alias M1 Pro und M1 Max vor. Die von Apple veröffentlichten Renderings der Die-Shots zeigten recht schnell, wie man hier vorgegangen ist. Der M1 ist ein eigenständiges Design mit vier CPU- und acht GPU-Kernen auf einer Fläche von 119 mm². Der M1 Pro entspricht mit seinen etwa 240 mm² mit vier CPU- und 16 GPU-Kernen... [mehr]

Gemeinsam mit den neuen MacBook-Pro-Modelle stellten Apple auch die neuesten Ableger der M1-SoC-Generation alias M1 Pro und M1 Max vor. Die von Apple veröffentlichten Renderings der Die-Shots zeigten recht schnell, wie man hier vorgegangen ist. Der M1 ist ein eigenständiges Design mit vier CPU- und acht GPU-Kernen auf einer Fläche von 119 mm². Der M1 Pro entspricht mit seinen etwa 240 mm² mit vier CPU- und 16 GPU-Kernen... [mehr] -

RISC-V-Konferenz: Details zur Chiplet-Architektur und dem P550-Nachfolger

Vom 6. bis zum 8. Dezember wird das RISC-V Summit stattfinden. SiFive kündigt für die Konferenz einige Neuigkeiten an. Auf der Supercomputing 2021 spielte das Thema RISC-V noch eine untergeordnete Rolle, dies soll sich jedoch in Zukunft ändern. Chiplets und der Nachfolger des P550 sollen der Fokus für SiFive sein. Bereits vor einigen Wochen gab SiFive erste Details zum Next-Gen P-Series-Kern preis. Dieser soll noch einmal um 50 % schneller als... [mehr]

Vom 6. bis zum 8. Dezember wird das RISC-V Summit stattfinden. SiFive kündigt für die Konferenz einige Neuigkeiten an. Auf der Supercomputing 2021 spielte das Thema RISC-V noch eine untergeordnete Rolle, dies soll sich jedoch in Zukunft ändern. Chiplets und der Nachfolger des P550 sollen der Fokus für SiFive sein. Bereits vor einigen Wochen gab SiFive erste Details zum Next-Gen P-Series-Kern preis. Dieser soll noch einmal um 50 % schneller als... [mehr] -

Samsung I-Cube4: Chiplets auf dünnem Interposer werden effizienter

Nachdem IBM heute den ersten im 2-nm-Prozess gefertigten Chip angekündigt hat, folgt eine weitere Ankündigung aus der Halbleiterfertigung. Samsung kündigt mit Interposer-Cube4 (I-Cube4) die nächste Generation der 2.5D-Integration für die Kombination verschiedener Chiplets auf einem Package an. Im Vergleich zu I-Cube2 hat Samsung vor allem einige Änderungen in der Interposer-Technik vorgenommen. Die I-Cube-IP von... [mehr]

Nachdem IBM heute den ersten im 2-nm-Prozess gefertigten Chip angekündigt hat, folgt eine weitere Ankündigung aus der Halbleiterfertigung. Samsung kündigt mit Interposer-Cube4 (I-Cube4) die nächste Generation der 2.5D-Integration für die Kombination verschiedener Chiplets auf einem Package an. Im Vergleich zu I-Cube2 hat Samsung vor allem einige Änderungen in der Interposer-Technik vorgenommen. Die I-Cube-IP von... [mehr] -

OpenFive stellt Interconnect-PHY für zukünftige Chiplet-Designs vor

OpenFive, eine Tochter von SiFive, die wiederum Kern-IP und Designs auf Basis der freien RISC-V-Befehlssatzstruktur entwickelt, hat ein Die-to-Die-Interface für Chiplets vorgestellt, welches eine Alternative zu Intels EMIB oder Foveros, bzw. den verschiedenen 3DFabric-Technologien von TSMC sein soll. OpenFive bietet bereits verschiedene Die-to-Die-Interfaces (D2D) an, die mit einer Bandbreite von 1.024 Bit sowie bei einem Takt von 2... [mehr]

OpenFive, eine Tochter von SiFive, die wiederum Kern-IP und Designs auf Basis der freien RISC-V-Befehlssatzstruktur entwickelt, hat ein Die-to-Die-Interface für Chiplets vorgestellt, welches eine Alternative zu Intels EMIB oder Foveros, bzw. den verschiedenen 3DFabric-Technologien von TSMC sein soll. OpenFive bietet bereits verschiedene Die-to-Die-Interfaces (D2D) an, die mit einer Bandbreite von 1.024 Bit sowie bei einem Takt von 2... [mehr] -

AMD verkauft teilaktivierte Ryzen 5900X/5950X mit nur einem CCD

AMDs Chiplet-Design versetzt das Unternehmen in die Lage das Produkt-Design entsprechend flexibel zu gestalten. Im Falle der Ryzen-5000-Prozessoren befindet sich neben einem I/O-Die entweder ein oder zwei CCDs mit jeweils acht Kernen im Package. Alle Prozessoren mit acht oder weniger Kernen verwenden dabei nur ein CCD. Sobald wir aber vom Ryzen 9 5900X mit 12 oder dem Ryzen 9 5950X mit gar 16 Kernen sprechen, kommen zwei CCDs (CCD#1 und CCD#2)... [mehr]

AMDs Chiplet-Design versetzt das Unternehmen in die Lage das Produkt-Design entsprechend flexibel zu gestalten. Im Falle der Ryzen-5000-Prozessoren befindet sich neben einem I/O-Die entweder ein oder zwei CCDs mit jeweils acht Kernen im Package. Alle Prozessoren mit acht oder weniger Kernen verwenden dabei nur ein CCD. Sobald wir aber vom Ryzen 9 5900X mit 12 oder dem Ryzen 9 5950X mit gar 16 Kernen sprechen, kommen zwei CCDs (CCD#1 und CCD#2)... [mehr] -

Weiteres Chiplet-Patent für GPUs: AMD zeigt Konzept auf

Unter der Patentnummer "US 2020/0409859 A1" hat AMD gegenüber dem United States Patent and Trademark Office ein weiteres Patent eingereicht, welches sich mit einem Chiplet-Design für GPUs beschäftigt. Wir haben ein solches bereits mehrfach gesehen, auch schon von NVIDIA. Selbst konkrete Umsetzungen gibt es in gewissen Bereichen bereits. Imagination stellte kürzlich seine neueste GPU-Serie vor, deren BXE-, BXM- und... [mehr]

Unter der Patentnummer "US 2020/0409859 A1" hat AMD gegenüber dem United States Patent and Trademark Office ein weiteres Patent eingereicht, welches sich mit einem Chiplet-Design für GPUs beschäftigt. Wir haben ein solches bereits mehrfach gesehen, auch schon von NVIDIA. Selbst konkrete Umsetzungen gibt es in gewissen Bereichen bereits. Imagination stellte kürzlich seine neueste GPU-Serie vor, deren BXE-, BXM- und... [mehr] -

Intels Zukunft liegt im Packaging und Chiplet-Design

Der Intel Architecture Day 2020 hatte zahlreiche Neuheiten zu verkünden. Dazu gehören die Tiger-Lake-Prozessoren, Intels Rettungsaktion für die Fertigung in 10 nm, die Ankündigung einer Xe-HPG Gaming-GPU und vieles mehr. Doch auch wenn die Fertigung in 10 nm erst jetzt in Fahrt kommen wird und man erst kürzlich verkünden musste, dass sich die ersten Chips aus der Fertigung in 7 nm um sechs Monate verzögern werden, so hat man bei Intel... [mehr]

Der Intel Architecture Day 2020 hatte zahlreiche Neuheiten zu verkünden. Dazu gehören die Tiger-Lake-Prozessoren, Intels Rettungsaktion für die Fertigung in 10 nm, die Ankündigung einer Xe-HPG Gaming-GPU und vieles mehr. Doch auch wenn die Fertigung in 10 nm erst jetzt in Fahrt kommen wird und man erst kürzlich verkünden musste, dass sich die ersten Chips aus der Fertigung in 7 nm um sechs Monate verzögern werden, so hat man bei Intel... [mehr] -

Xeon SoMa: Geheimnisvolles MCM-Design von Intel aufgetaucht (Update: Die-Shots)

Auf eBay sind in den vergangenen Stunden ältere, aber bisher unbekannte Prozessoren von Intel aufgetaucht. Diese hören auf den Namen Xeon SoMa und sollen ein bisher unbekanntes MCM-Design verwenden. Welchen genauen Verwendungszweck der Chip erfüllt, ist nicht bekannt. Das Package-Design ist dem der Skylake-Prozessoren für den Sockel LGA1151 nicht ganz unähnlich, offenbar aber kann der Prozessor nicht einfach einem entsprechenden Mainboard... [mehr]

Auf eBay sind in den vergangenen Stunden ältere, aber bisher unbekannte Prozessoren von Intel aufgetaucht. Diese hören auf den Namen Xeon SoMa und sollen ein bisher unbekanntes MCM-Design verwenden. Welchen genauen Verwendungszweck der Chip erfüllt, ist nicht bekannt. Das Package-Design ist dem der Skylake-Prozessoren für den Sockel LGA1151 nicht ganz unähnlich, offenbar aber kann der Prozessor nicht einfach einem entsprechenden Mainboard... [mehr] -

Ohne Chiplet-Design wäre ein Ryzen 9 3950X mehr als doppelt so teuer

AMDs Entscheidung, mit der ersten Zen-Architektur und den ersten Ryzen-Prozessoren auf ein Chiplet-Design zu setzen, hat sich am Ende als eine richtige herausgestellt. AMD setzte mit der Entwicklung alles auf eine Karte. Bereits mehrfach haben wir die Vorteile einer solchen Strategie herausgestellt. Mit der Zen-2-Architektur hat AMD das Konzept dann noch etwas weiter gesponnen und trennt beispielsweise die Compute-Dies (CCDs) und die... [mehr]

AMDs Entscheidung, mit der ersten Zen-Architektur und den ersten Ryzen-Prozessoren auf ein Chiplet-Design zu setzen, hat sich am Ende als eine richtige herausgestellt. AMD setzte mit der Entwicklung alles auf eine Karte. Bereits mehrfach haben wir die Vorteile einer solchen Strategie herausgestellt. Mit der Zen-2-Architektur hat AMD das Konzept dann noch etwas weiter gesponnen und trennt beispielsweise die Compute-Dies (CCDs) und die... [mehr] -

8,34 Milliarden Transistoren: Ein Rome-IOD zeigt seine Details

Mit dem Chiplet-Design der aktuellen Ryzen-, Ryzen-Threadripper- und EPYC-Prozessoren ist es AMD zusammen mit einer stetigen Weiterentwicklung der µArchitektur gelungen in fast allen Bereichen wieder ein echter Gegenspieler zum Konkurrenten Intel zu sein. Bereits mehrfach hatten wir über die Details des Designs berichtet. So haben wir uns die CCDs und IODs der neuen Ryzen-Prozessoren in detailreichen Chipshots bereits angeschaut. Auch die... [mehr]

Mit dem Chiplet-Design der aktuellen Ryzen-, Ryzen-Threadripper- und EPYC-Prozessoren ist es AMD zusammen mit einer stetigen Weiterentwicklung der µArchitektur gelungen in fast allen Bereichen wieder ein echter Gegenspieler zum Konkurrenten Intel zu sein. Bereits mehrfach hatten wir über die Details des Designs berichtet. So haben wir uns die CCDs und IODs der neuen Ryzen-Prozessoren in detailreichen Chipshots bereits angeschaut. Auch die... [mehr] -

EPYC und Ryzen Threadripper: Das CCD- und L3-Layout für 16 bis 64 Kerne

Die EPYC-Prozessoren der zweiten Generation alias Rome sind bereits offiziell vorgestellt worden. Die dritte Generation der Ryzen-Threadripper-Prozessoren wird auf der gleichen Hardware basieren – verwendet also auch einen zentralen I/O-Die und bis zu acht Compute-Chiplets mit wiederum jeweils acht Kernen. Im November sollen die ersten der neuen Ryzen-Threadripper-Prozessoren auf den Markt kommen. Ein Detail welches bisher noch wenig Beachtung... [mehr]

Die EPYC-Prozessoren der zweiten Generation alias Rome sind bereits offiziell vorgestellt worden. Die dritte Generation der Ryzen-Threadripper-Prozessoren wird auf der gleichen Hardware basieren – verwendet also auch einen zentralen I/O-Die und bis zu acht Compute-Chiplets mit wiederum jeweils acht Kernen. Im November sollen die ersten der neuen Ryzen-Threadripper-Prozessoren auf den Markt kommen. Ein Detail welches bisher noch wenig Beachtung... [mehr] -

AMD nennt Details zum I/O-Die der EPYC-Prozessoren

Bisher hatte sich AMD noch nicht zu einer entscheidenden Komponente der neuen EPYC-Prozessoren geäußert: Dem I/O-Die oder kurz IOD. Nun hat AMD Informationen zur Größe und Komplexität des IOD auf der Hotchips-Konferenz veröffentlicht. Dabei werden auch die Vorteile des Chiplet-Designs einmal mehr deutlich. AMD lässt die CCDs mit jeweils acht Kernen bei TSMC in 7 nm fertigen und kann diese auf den Ryzen- und EPYC-Prozessoren (sowie... [mehr]

Bisher hatte sich AMD noch nicht zu einer entscheidenden Komponente der neuen EPYC-Prozessoren geäußert: Dem I/O-Die oder kurz IOD. Nun hat AMD Informationen zur Größe und Komplexität des IOD auf der Hotchips-Konferenz veröffentlicht. Dabei werden auch die Vorteile des Chiplet-Designs einmal mehr deutlich. AMD lässt die CCDs mit jeweils acht Kernen bei TSMC in 7 nm fertigen und kann diese auf den Ryzen- und EPYC-Prozessoren (sowie... [mehr] -

TSMC zeigt riesiges Chiplet-Design mit ebenso gigantischem Interposer

TSMC reiht sich in die Reihe derjenigen ein, für die Moore's law noch lange nicht am Ende ist. Eine Kombination aus voranschreitenden Fertigungstechniken und neuen Design-Ansätzen soll dafür sorgen, dass wir noch über Jahre hinweg regelmäßige Steigerungen in der Packdichte und Rechenleistung sehen werden – so zumindest sieht dies Godfrey Cheng, Leiter des Marketing bei TSMC in einem Blogpost. Dabei gibt Cheng erstaunliche Einblicke... [mehr]

TSMC reiht sich in die Reihe derjenigen ein, für die Moore's law noch lange nicht am Ende ist. Eine Kombination aus voranschreitenden Fertigungstechniken und neuen Design-Ansätzen soll dafür sorgen, dass wir noch über Jahre hinweg regelmäßige Steigerungen in der Packdichte und Rechenleistung sehen werden – so zumindest sieht dies Godfrey Cheng, Leiter des Marketing bei TSMC in einem Blogpost. Dabei gibt Cheng erstaunliche Einblicke... [mehr] -

TSMC zeigt eigene Chiplet-Techniken für ARM-HPC-Prozessoren

Die Zukunft scheint den Chiplet-Designs zu gehören. AMD wird dazu mit den Ryzen-Prozessoren der dritten Generation und den EPYC-Prozesoren der zweiten Generation erste Produkte auf den Markt bringen und die Erfahrungen, die AMD bei den Zen-Prozessoren gemacht hat, will man in zukünftigen RDNA-Architekturen für die Grafikkarten umsetzen. Auch Intel arbeitet bei den Prozessoren in diese Richtung und das, was Intel bisher... [mehr]

Die Zukunft scheint den Chiplet-Designs zu gehören. AMD wird dazu mit den Ryzen-Prozessoren der dritten Generation und den EPYC-Prozesoren der zweiten Generation erste Produkte auf den Markt bringen und die Erfahrungen, die AMD bei den Zen-Prozessoren gemacht hat, will man in zukünftigen RDNA-Architekturen für die Grafikkarten umsetzen. Auch Intel arbeitet bei den Prozessoren in diese Richtung und das, was Intel bisher... [mehr] -

AMD will DRAM und SRAM in das CPU-Package bringen

Auf der High Performance Computing Conference gab Forrest Norrod, Senior Vice President und General Manager der Datacenter-Gruppe bei AMD, eine interessante Präsentation. Dabei ging er zunächst einmal auf die aktuellen Herausforderungen im Chipdesign ein. Diese liegen laut AMD in der Fertigung immer kleinerer Strukturen bei gleichzeitig immer größeren Anzahl an Transistoren und damit einer erhöhten Komplexität sowie der Tatsache, dass die... [mehr]

Auf der High Performance Computing Conference gab Forrest Norrod, Senior Vice President und General Manager der Datacenter-Gruppe bei AMD, eine interessante Präsentation. Dabei ging er zunächst einmal auf die aktuellen Herausforderungen im Chipdesign ein. Diese liegen laut AMD in der Fertigung immer kleinerer Strukturen bei gleichzeitig immer größeren Anzahl an Transistoren und damit einer erhöhten Komplexität sowie der Tatsache, dass die... [mehr] -

Ascend 910: Auch Huawei präsentiert einen Chip mit acht Dies

Für AMD ist das Chiplet-Design aus getrennten Chips für die CPU-Kerne und die I/O-Komponenten wegweisend. Die EPYC-Prozessoren der 2. Generation werden derart aufgebaut sein und gleiches gilt auch für die Ryzen- und Ryzen-Threadripper-Prozessoren der 3. Generation auf Basis der Zen-2-Architektur. Für Intel ist ist die EMIB-Weiterentwicklung (Embedded Multi-die Interconnect Bridge) namens Foveros der Weg in die Multi-Chip-Zukunft und... [mehr]

Für AMD ist das Chiplet-Design aus getrennten Chips für die CPU-Kerne und die I/O-Komponenten wegweisend. Die EPYC-Prozessoren der 2. Generation werden derart aufgebaut sein und gleiches gilt auch für die Ryzen- und Ryzen-Threadripper-Prozessoren der 3. Generation auf Basis der Zen-2-Architektur. Für Intel ist ist die EMIB-Weiterentwicklung (Embedded Multi-die Interconnect Bridge) namens Foveros der Weg in die Multi-Chip-Zukunft und... [mehr] -

Keine APU im Chiplet-Design für Ryzen 3000 geplant

Die Vorschau auf die Ryzen-3000-Serie alias Matisse auf der CES ist wie die Präsentation der Radeon VII ein wahrer Paukenschlag gewesen. Nach den EPYC-Prozessoren der zweiten Generation setzt AMD auch im Desktop auf das Chiplet-Design. Das CPU-Package besteht aus einem in 7 nm gefertigten CPU-Die mit acht Zen-2-Kernen sowie einem in 14 nm gefertigten I/O-Die. Das Chiplet-Design versetzt AMD bei den EPYC-Prozessoren in die Lage, extrem flexibel... [mehr]

Die Vorschau auf die Ryzen-3000-Serie alias Matisse auf der CES ist wie die Präsentation der Radeon VII ein wahrer Paukenschlag gewesen. Nach den EPYC-Prozessoren der zweiten Generation setzt AMD auch im Desktop auf das Chiplet-Design. Das CPU-Package besteht aus einem in 7 nm gefertigten CPU-Die mit acht Zen-2-Kernen sowie einem in 14 nm gefertigten I/O-Die. Das Chiplet-Design versetzt AMD bei den EPYC-Prozessoren in die Lage, extrem flexibel... [mehr]