Werbung

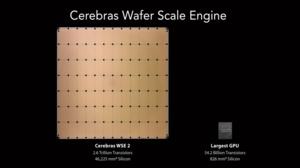

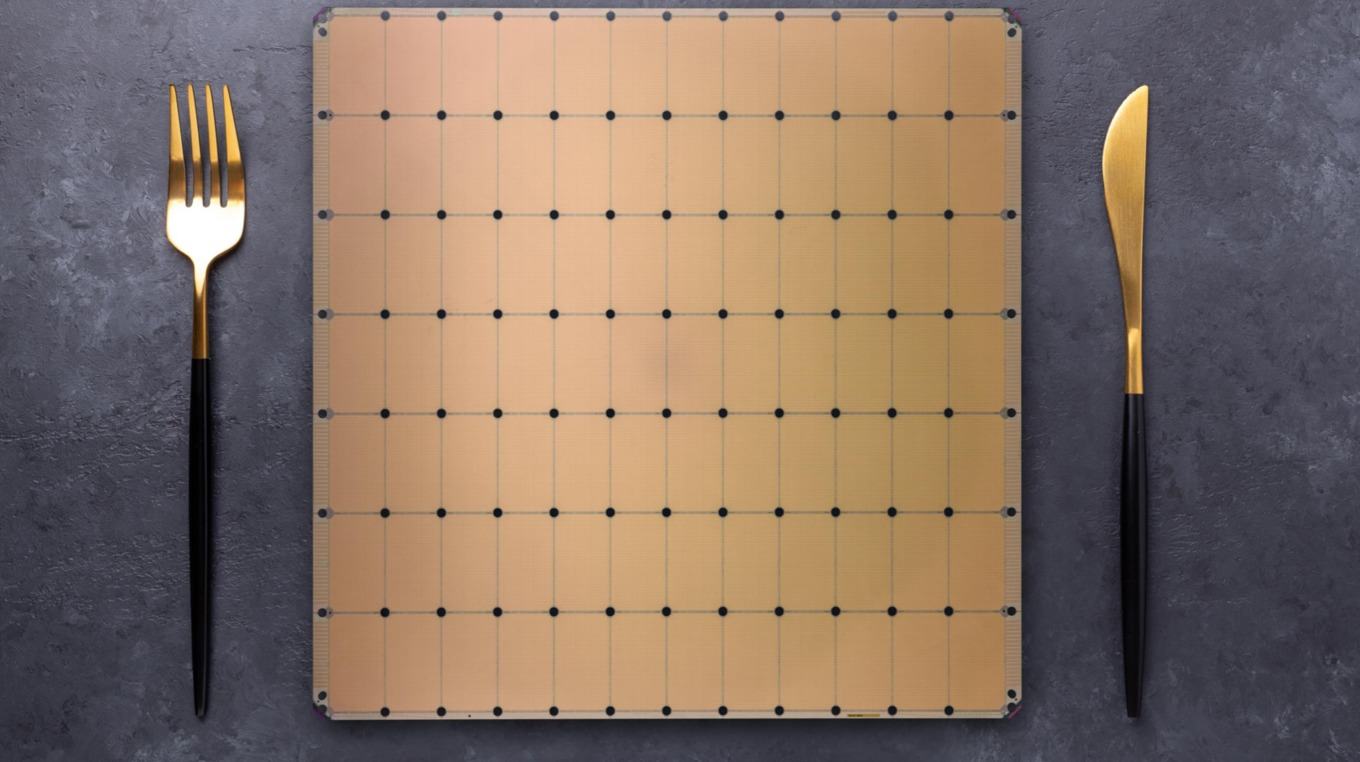

Auf der Linley Spring Processor Conference 2021 hat Cerebras seine zweite Generation der Wafer Scale Engine oder kurz WSE-2 vorgestellt. Im Sommer 2019 sorgte der gigantische AI-Chip mit 46.225 mm² für Aufmerksamkeit, da er neben der Fertigung auch in der Anwendung völlig neue Konzepte anführte. Die zweite Genration setzt den Weg fort, den man eingeschlagen hat.

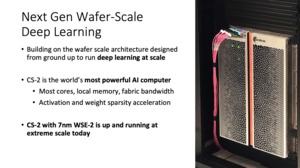

Durch die Fertigung ist man allerdings in gewisser Weise limitiert. Aus einem runden Wafer mit einem Durchmesser von 300 mm kann kein Chip hergestellt werden, der bei rechteckigen Abmessungen größer als diese 46.225 mm² sein kann. Insofern bleibt es auch bei der zweiten Generation bei diesen Abmessungen. Allerdings wechselt man von einer Fertigung in 16 nm bei TSMC zur Fertigung in 7 nm. Dies macht es möglich, dass nicht mehr "nur" 400.000 AI-Kerne auf dem Chip Platz haben, sondern nun mehr als doppelt so viele – 850.000 sind es um genau zu sein. Die Anzahl der Transistoren steigt von 1.200 Milliarden auf 2.600 Milliarden. Die Größe des integrierten SRAM wächst von 18 auf 40 GB. Die kombinierte Speicherbandbreite beläuft sich auf 20 PB/s. Der Interconnect, der alle 850.000 AI-Kerne miteinander verbindet, kommt auf eine kombinierte Bandbreite von 220 PB/s. In beiden Fällen ist dies ebenfalls eine Verdopplung gegenüber dem Vorgänger.

Die eigentlichen AI-Kerne (Sparse Linear Algebra Compute Cores) SLAC haben in der Mikroarchitektur ebenfalls einige Änderungen erhalten. Auf Details geht Cerebras aber nicht ein. Ein paar weitere Details gibt es zum Aufbau: Der Chip besteht aus 84 Dies, die aber eben auf dem Wafer verbleiben und über 84 unabhängige Taktdomains verfügen. Diese 84 Chips werden auch unabhängig voneinander mit Spannung versorgt.

| WSE-1 | WSE-2 | |

| Fertigung | 16 nm | 7 nm |

| Chipgröße | 46.225 mm² | 46.225 mm² |

| Anzahl der Transistoren | 1.200 Milliarden | 2.600 Milliarden |

| AI-Kerne | 400.000 | 850.000 |

| SRAM | 18 GB | 40 GB |

| Speicherbandbreite | 9 PB/s | 20 PB/s |

| Fabric-Bandbreite | 100 PB/s | 220 PB/s |

Noch eindrucksvoller sind diese Zahlen, wenn man die WSE-2 mit anderen Chips vergleicht. Der NVIDIA A100 kommt als größte GPU auf 826 mm². Darin bringt NVIDIA 54 Milliarden Transistoren unter. Die Anzahl der Kerne ist etwas schwer zu bestimmen. So verbaut NVIDIA hier 6.912 FP32-Recheneinheiten, 3.456 FP64-Recheneinheiten und 432 Tensor Cores. Der L2-Cache ist mit 40 MB natürlich ebenfalls deutlich kleiner. Mit HBM2E kommt die GA100-GPU inzwischen auf 2 TB/s an Speicherbandbreite und NVLink 3.0 bietet immerhin 600 GB/s zwischen mehreren GA100-GPUs. Aber wie gesagt: Nicht alle diese Zahlen lassen sich auch gut miteinander vergleichen.

Die Fertigung eines Chips in der Größe eines Wafers hat natürlich Herausforderungen hinsichtlich der Ausbeute – sollte man denken, denn Cerebras hat auch diesen Aspekt neu betrachtet und ist zu einer interessanten Lösung gekommen, die man bereits für die erste Generation einsetzte. Cerebras ließ 1,0 bis 1,5 % an zusätzlichen AI-Kernen fertigen. Kommt es also zu Fehlern in der Fertigung, hat man eben diese 1,0 bis 1,5 % als Sicherheit auf dem Chip. Dies handhabt man für die WSE-2 mit 1 bis 2 % ähnlich. Fällt einer der Kerne aus, wird der ebenfalls redundant vorhandene Fabric umgeleitet, um den defekten Kern auszusparen und einen der zusätzlichen Kerne zu verwenden. Cerebras bestätigte allerdings auch, dass die Ausbeute in 7 nm deutlich geringer ist, als dies für 16 nm der Fall war. Offenbar aber kann man dies über die Redundanz kompensieren.

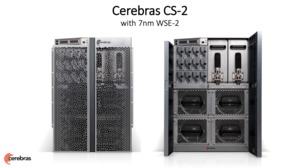

Aber diesem Thema haben wir uns schon genauso gewidmet wie dem eigentlichen System, in dem ein solcher Chip steckt. Stromversorgung, Kühlung, Anbindung an weitere Systeme – all dies kann die theoretische Leistung eines solch gigantischen Chips überhaupt erst nutzbar machen. Das CS-2 soll als Gesamtsystem ähnlich bis identisch aufgebaut sein. Wir reden also von einer Leitungsaufnahme von 20 kW und der schnellen Netzwerkanbindung über zwölf 100-GbE-Anschlüsse. Gekühlt wird der Chip über eine Wasserkühlung.

Weiterhin viel Arbeit steckt Cerebras auch weiterhin in die Software, um die Sparse Linear Algebra Compute (SLAC) Cores vollständig nutzen zu können. ML-Frameworks wie TensorFlow und PyTorch werden bereits unterstützt. Es gibt auch bereits einen Cerebras Graph Compiler (CGC), um benutzerspezifische Daten auf ein ML-Netzwerk zu überführen. Die Software soll neben der extremen Bandbreite des Interconnects dafür sorgen, dass die Auslastung der Hardware extrem hoch ist und die Rechenleistung dementsprechend ihr Maximum erreicht. Die 850.000 Kerne müssen auch gefüttert und ausgelastet werden, damit ein solches System sein Leistungspotential auch abrufen kann.

Ab dem dritten Quartal will Cerebras die ersten CS-2 mit WSE-2 ausliefern. Der Preis des CS-1 lag bei knapp über zwei Millionen US-Dollar. Ein CS-2-System soll "mehrere Millionen US-Dollar" kosten.