Werbung

Auf der Linley Spring Processor Conference 2021 in der vergangenen Woche stellte Cerebras die zweite Generation der Wafer Scale Engine mit 850.000 AI-Kernen vor. Außerdem verkündete SiFive eine Erweiterung seiner Intelligence IP um den neuen X280-Prozessor. Eingebaut werden kann dieser in die U7-Series-Kerne mit RISC-V ISA.

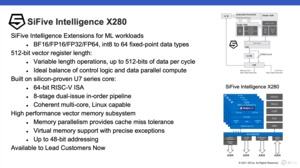

Der Intelligence X280 soll sämtliche AI- und ML-Workloads beschleunigen – von INT8, über BF16 und FP16 bis hin zu FP32 und FP64. Entscheidend aber dürften die 512 Bit breiten Vektor-Register sein, die über eine 256 Bit Pipeline und 256 Bit Speichereinheit einen Vektor mit 512 Bit pro Taktzyklus verarbeiten können. Skalare Recheneinheiten sind als Controler Logic vorhanden und sollen zum Vektor-Teil sehr ausbalanciert aufgebaut sein. Auf diesen Rechenkernen kann zudem ein Linux ausgeführt werden.

Die Vektorerweiterungen werden immer wichtiger. Mit Armv9 stellte Arm erst kürzlich eine neue Erweiterung des AArch64 Instruction Sets vor, die SVE- und SVE2-Befehlssatzerweiterungen vorsieht. Mit 512 Bit pro Taktzyklus ist der Intelligence X280 schon recht breit aufgestellt. Ein Blockdiagramm des Intelligence X280 zeigt den üblichen Aufbau über ein Frontend, welches die Daten wiederum auf die skalaren und Vektor-Einheiten verteilt, in eine Load/Store-Einheit übergibt und mit 256 Bit pro Taktzyklus an den L2-Cache übergibt.

Einer der ersten Kunden für den Intelligence X280 ist das kanadische AI-Startup Tenstorrent, bei dem Jim Keller seit Januar als CTO angestellt ist.

"The Tenstorrent architecture addresses the growing demands that come with data-written code as part of Software 2.0," so Keller. "We’re excited to partner with SiFive because of their ability to deliver CPUs and software for the modern RISC-V ecosystem."

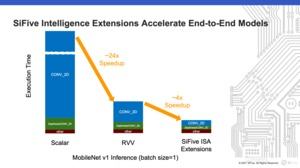

Der Intelligence X280 ist vollständig zu den RISC-V Vector Extension (RVV) kompatibel. Im Vergleich zu einem RV64GCV-Kern soll der Intelligence X280 in der Berechnung mit 64-Bit-Vektoren um den Faktor 12 schneller sein. Welche Stellenwert die Anpassungen der Befehlssatzerweiterungen haben, zeigt ein weiterer Vergleich, der zunächst die Berechnung in skalaren Kernen mit solche mit RVV-Erweiterung vergleicht (Faktor 24x) und dann noch die SiFive-ISA-Erweiterungen hinzunimmt (Faktor 4x).

Weder Tenstorrent noch SiFive macht aktuell genauere Angaben zum Aufbau der Kerne und deren erste Umsetzung. Theoretisch lässt sich ein SoC mit einer Vielzahl dieser Kerne ausbauen. Im Datacenter will man sicherlich möglichst viele Kerne in einen leistungsstarken Chip packen. Bei Tenstorrent äußerte man sich zuletzt eher in Richtung Edge- und Micro-Edge-Umsetzungen, so dass hier eher kleinere Chips zu erwarten sind.