Werbung

Nachdem OpenFive vor einigen Wochen eine neue technische Umsetzung eines Interconnect-PHY für zukünftige Chiplet-Designs vorstellte und SiFive bekanntgegeben hat, dass ab sofort High-Performance-SoCs mit SiFive-IP bei TSMC in 5 nm gefertigt werden können, erfolgte in der vergangenen Woche die Vorstellung des Intelligence X280 Core-Designs, welches mit 512 Bit Vektoreinheiten sämtliche AI- und ML-Workloads beschleunigen können soll. Tenstorrent ist einer der ersten Kunden dieses Designs.

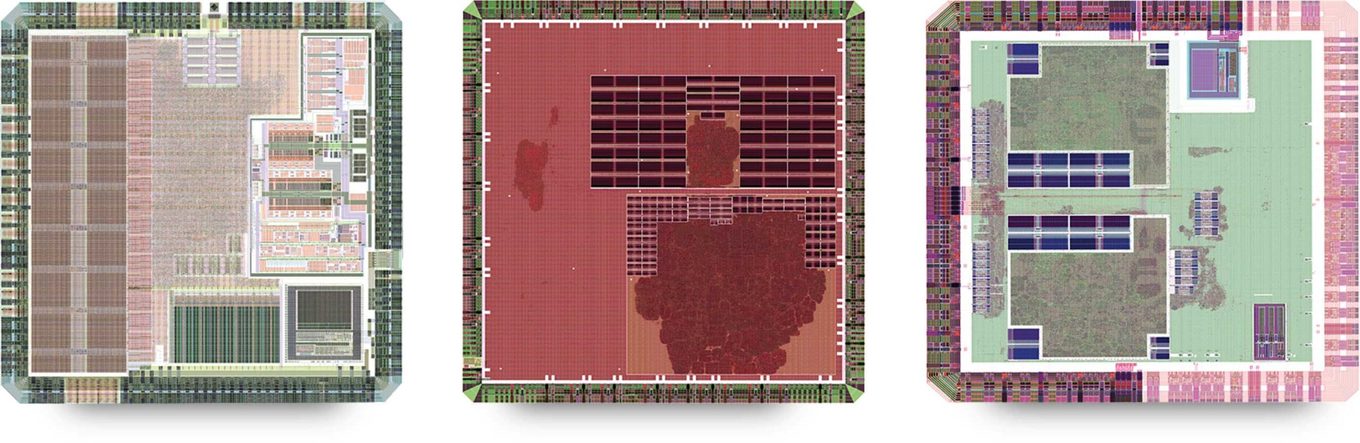

Nun vermeldet SiFive zudem eine enge Zusammenarbeit mit dem Auftragsfertiger Samsung Foundry, sodass hier in 14 nm gefertigte AI- und ML-SoCs auf Basis des RISC-V-Designs von SiFive vom Band laufen können sollen. Am 13. April seien die ersten Chips eines Projektes, welches AI-Inferencing-Rechenblöcke mit Microsofts Open Compute Project (OCP) "Zeppelin" verknüpft, fertiggestellt worden. Beim Projekt Zeppelin handelt es sich um einen Datenkompressions-Algorythmus samt dazugehöriger Hardwarebeschleunigung. Das Verfahren soll ein um den Faktor zwei höheres Kompressionsverhältnis im Vergleich zu Zlib-L4 erreichen können.

In der Entwicklung von SoCs für die Fertigung bei Samsung unterstützt werden Unternehmen durch SEMIFIVE. Das in Seoul ansässige Unternehmen ist auf solche Custom-Lösungen spezialisiert. Weitere Komponenten des SoCs sind ein PCI-Express-4.0-sowie ein Quad-Channel LPDDR4/4X-Interface.

Aktuell hagelt es Ankündigungen rund um Designs auf Basis von RISC-V. Während es einzelne Kerne des freien Designs schon in diverse Produkte geschafft haben, so wird in den kommenden Monaten der große Durchbruch erwartet, der solche Chips im Cloud-, Edge- und Datacenter-Bereich etablieren soll.