Werbung

IBM ist offenbar ein Durchbruch in der Fertigung von Transistoren gelungen. Alle großen Halbleiterhersteller sind auf der Suche nach Technologien, die es ermöglichen, Transistoren immer kleiner zu fertigen und dichter zu packen. Die Fertigung in 2 nm ermöglicht eine um 45 % höhere Leistung im Vergleich zur Fertigung in 7 nm – oder aber die Leistungsaufnahme kann um 75 % reduziert werden. Wohlgemerkt sprechen wir hier von einem Vergleich von 7 zu 2 nm, was ein untypisch großer Sprung wäre.

IBM hat eine lange Tradition in der Halbleiterfertigung – auch wenn Intel, TSMC oder Samsung hier deutlicher im Fokus stehen. Die erste Fertigung in 7 nm wurde 2015 angekündigt, eine Technik für die 5-nm-Fertigung in 2017. Für die 5-nm-Fertigung wechselte IBM von klassischen FinFETs auf Nanosheets.

Viel wichtiger als eine Größenangabe einer gewissen Strukturgröße, die zwischen den verschiedenen Herstellern nicht mehr vergleichbar ist, ist die Transistordichte. Zuletzt beim Thema Rocket Lake-S haben wir uns diesem Thema gewidmet und eine Tabelle aufgestellt.

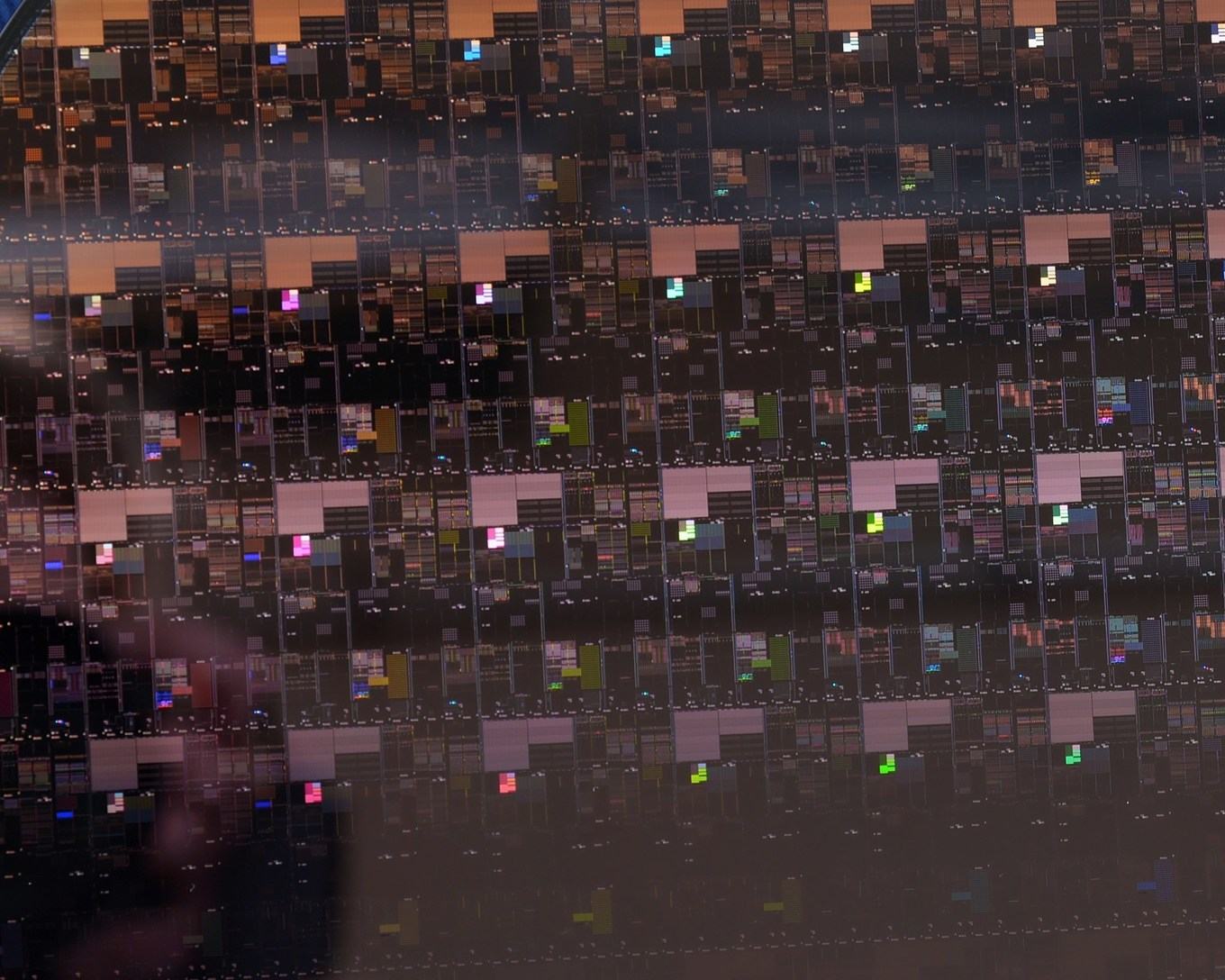

IBM spricht von 50 Milliarden Transistoren auf einer Chipfläche die einem Fingernagel entspricht. Wie groß der Fingernagel dabei angenommen wird, verrät man allerdings nicht. Anandtech hat bei IBM nachgefragt und bekam eine Größe von 150 mm² genannt. Somit kommen wir hier auf eine Transistordichte von 333 MT/mm².

| Transistordichte | |

| TSMC 16/14 nm | 28,2 MT/mm² |

| TSMC 10 nm | 52,5 MT/mm² |

| TSMC 7 nm | 91 MT/mm² |

| TSMC 5 nm | ? 170 MT/mm² |

| TSMC 3 nm | ? 300 MT/mm² |

| Intel 14 nm | 37,5 MT/mm² |

| Intel 10 nm | 101 MT/mm² |

| Intel 7 nm | ? 200 bis 250 MT/mm² |

| IBM 2 nm | ? 333 MT/mm² |

In etwa kennen wir die Vergleichsgrößen von TSMC und Samsung. So geht TSMC von etwa 300 MT/mm² für die Fertigung in 3 nm aus und läge damit mit IBMs 2-nm-Fertigung gleichauf. Intel kommt in 7 nm auf geschätzte 200 bis 250 MT/mm². Dies zeigt auch recht deutlich, wie wenig gut sich 7, 5, 3 und 2 nm untereinander vergleichen lassen, wenn man die Transistordichte nicht mit einbezieht.

Die Transistordichte ist auch nicht immer gleich. Ein High-Performance-Prozess, der auf hohe Taktraten optimiert ist, hat eine geringere Transistordichte, als der Speicherbereich. Selbst innerhalb eines Chips gibt es Bereiche die dichter gepackt sind und solche, bei denen mehr Platz zwischen den Transistoren ist.

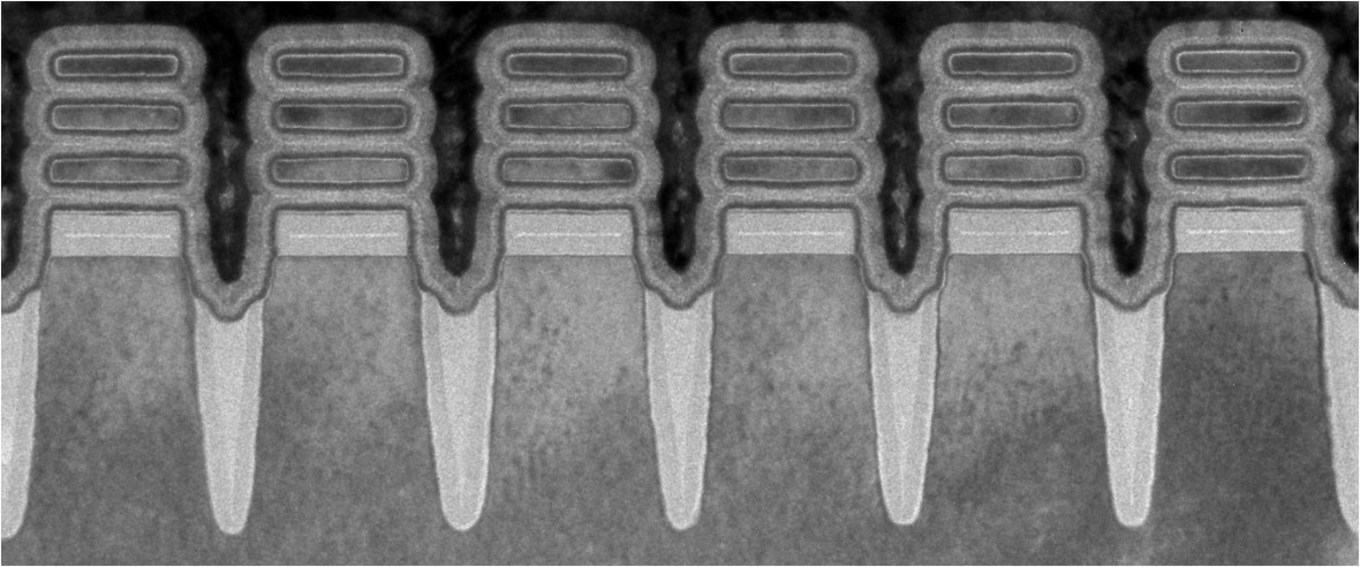

Der klassische FinFET hat bei solchen Strukturgrößen ausgedient. Stattdessen arbeiten alle Halbleiterhersteller an GAA-Transistoren (Gate-all-Around). GAA-Transistoren sind Feldeffekttransistoren (FET), deren Gates auf allen vier Seiten um ultradünne Kanäle gewickelt sind. Diese verbesserte Gate-Steuerung des Kanals überwindet die physikalischen Skalierungs- und Leistungsbeschränkungen von FinFETs und ermöglicht eine weitere Skalierung der Versorgungsspannung.

GAA-basierte FETs (GAAFETs) können in einer Vielzahl von Formfaktoren vorliegen. Einige Forschungsarbeiten haben sich auf GAAFETs auf der Basis von Nanodrähten konzentriert, wobei die GAAFETs so klein wie möglich sein sollten. Diese Art von GAAFETs sind in der Regel für Designs mit geringer Leistung nützlich, lassen sich aber nur schwer herstellen. Eine andere Implementierung macht den Kanal aus ultradünner Horizontalebene, was Vorteile in Bezug auf Leistung und kontinuierliche Skalierung bietet. Intel arbeitet an Self-Aligned 3D Stacked Multi-Ribbon CMOS Transistoren.

IBM stapelt die GAA-Transistoren in drei Ebenen. Die Zelle hat eine Höhe von 75 nm und eine Breite von 40 nm. Die Trennungen in den gestapelten Transistoren haben eine Höhe von 5 nm. Der Abstand zwischen den Stapeln beträgt 5 nm. Die Länge des Gates beträgt 12 nm. Hier fällt schnell auf, dass die 2 nm an keiner Stelle genannt werden. Diese Angabe ist eine reine Marketing-Zahl, die dazu dient die Fertigung überhaupt einordnen zu können, ohne zu sehr ins Detail gehen zu müssen.

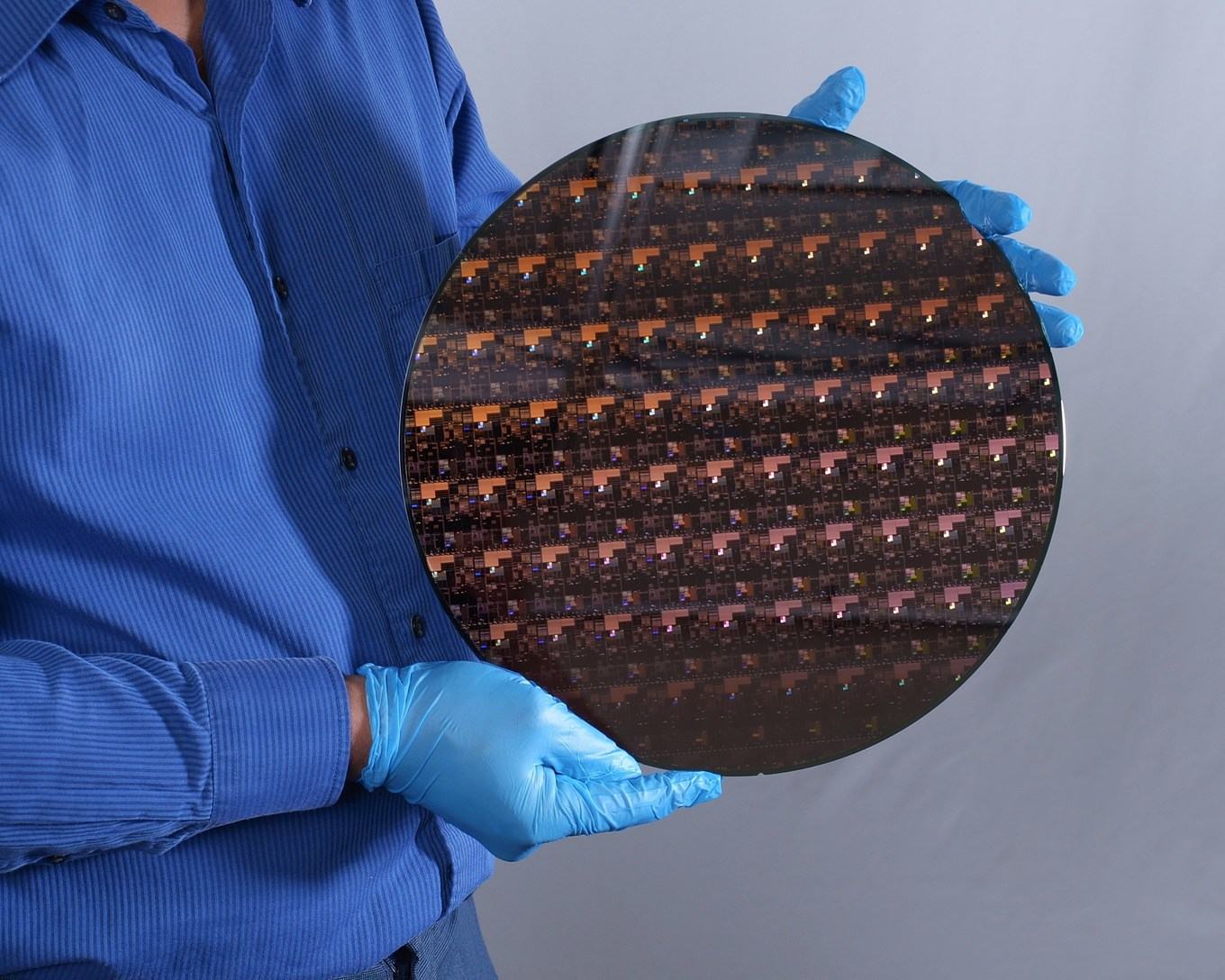

IBM hat die Testchips auf einem 300-mm-Wafer gefertigt. Diese Größe ist inzwischen typisch für die Fertigung großer Halbleitervolumen. Welchen Zweck der Testchip erfüllt, ist nicht bekannt. Vermutlich hat IBM hier in der Entwicklung typische Test-Strukturen gefertigt.

Wann die ersten richtigen Chips in 2 nm vom Band rollen, gibt IBM nicht bekannt. Ende diesen Jahres sollen die ersten in 7 nm gefertigten Power10-Prozessoren vom Band rollen. Dies gibt uns einen groben Zeitrahmen, denn die 7 nm wurden vor sechs Jahren angekündigt. Demnach dürfte es mindestens 4-5 Jahre dauern, bis die ersten Prozessoren mit dieser Technik hergestellt werden.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen